电子工程专辑讯 近日,佳能宣布将一款采用纳米压印光刻(NIL)技术的半导体制造设备推向市场,型号为FPA-1200NZ2C。该设备的NIL 技术可实现最小线宽 14 nm 的图案化,相当于生产目前最先进的逻辑半导体所需的5 nm节点。

佳能FPA-1200NZ2C纳米压印半导体制造设备。来源佳能佳能官网

正在运行的 FPA-1200NZ2C。来源佳能佳能官网

分光元件,具有三维微结构的光学元件,采用NIL工艺制成。来源佳能官网

NIL 技术是铠侠公司与佳能合作研发的光刻技术。

什么是NIL技术?

佳能表示,由于新产品不需要用于精细电路的特殊波长光源,因此与目前最先进逻辑半导体的光刻设备(5纳米节点,15纳米线宽)相比,可以显着降低功耗,还有助于环保。

NIL技术并不是什么新技术,该技术最早起源于1970 年,美国普林斯顿大学周郁(Stephen Y Chou)在1995年首次提出热纳米压印技术,压印作品分辨率高达 10~50nm,从此揭开了纳米压印制造技术的研究序幕。

NIL也就是古老的图形转移技术,活字印刷术是最初的压印技术原型,而纳米压印则是图形特征尺寸只有几纳米到几百纳米的一种压印技术。

纳米压印技术在国际半导体蓝图(ITRS)中被列为下一代32nm、22nm和16nm节点光刻技术的代表之一,比如在存储器市场,NIL就具有三分之一的市场份额,NIL极适合这种技术难度较低,结构化的产品制作,具有低成本、高效率等特点。

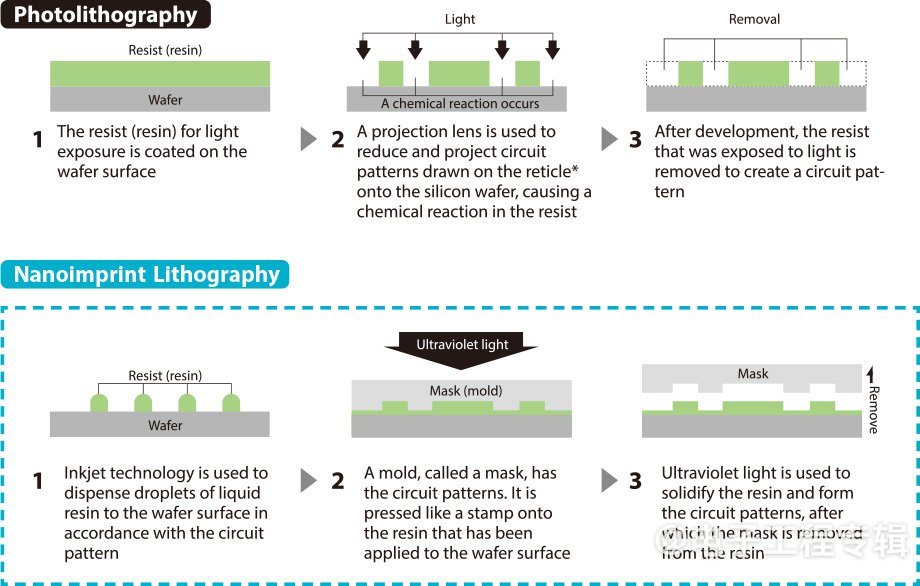

与使用光曝光电路图案的传统光刻技术不同,NIL 不需要光源。使用简单的原理形成电路,涉及将电路图案掩模(模具)转移到晶圆(薄硅板)表面上涂覆的抗蚀剂(树脂)上。

首先,NIL技术是先使用喷墨打印技术,将液滴状的纳米压印胶(本质也是光刻胶)喷涂在要压印电子回路图形的芯片上,然后将刻有电子回路图形的掩膜的模子像盖章一样按压在芯片的压印胶上,使用紫外线让压印胶变硬,形成电子回路图形,然后将掩膜从光刻胶分离。

光学光刻与纳米压印光刻原理

NIL技术实现也并不那么容易

这也意味着NIL技术与传统EUV技术一样,具有诸多难点,比如模板、压印胶、涂胶、设备、刻蚀等。

佳能提到了NIL技术的低成本优势,因为传统的光刻设备是将电路图案投射到涂有抗蚀剂的芯片上,而FPA-1200NZ2C则是将印有电路图案的光罩像印章一样压在芯片上。由于其电路图案转移过程不通过光学机构,掩膜上的精细电路图案可以在芯片上快速再现。因此,一次压印即可形成复杂的二维或三维电路图案,从而降低了成本。

但NIL技术的要求也很多,比如传统光学系统是在芯片表面均匀地形成光刻胶膜,NIL技术则却需要有针对的喷涂滴状压印胶,就像打印机喷墨一样要控制好力度。

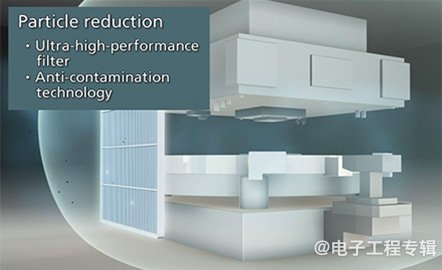

在压印过程中如何防止污染问题,“颗粒”是指颗粒状异物,颗粒是器件缺陷的一个原因,也是导致各种晶圆污染的原因之一。比如注意聚合物图形和掩膜间进入空气,就像手机贴膜也会进入气泡一样。实际生产过程更复杂,除了空气,任何细小的灰尘都会威胁产品的成品率,严重影响产能问题。

压印完成后该如何顺利且完整的脱模?因为模板和聚合物之间具有较强的粘性,行业时常会在模板表面蒸镀一层纳米级厚度的抗黏附材料,但固化后的聚合物避免不了与抗黏附材料发生物理摩擦,缩短模板寿命。

还有压印的材料问题,应力问题,形变问题,以及设备的寿命问题,要知道光刻机工作寿命普遍是20-30年的。

半导体芯片的发展与电路小型化的历史直接相关。这种小型化的关键是光源波长的缩短以及支持小型化的光刻技术的进步。20 世纪 90 年代初,350nm 图案(nm:纳米 = 十亿分之一米)通过 i 线光刻系统实现。此后,随着 KrF/ArF 光刻系统的出现,以及近年来 EUV 光刻系统的出现,这种小型化仍在继续。

光刻技术的进步对半导体芯片的小型化和成本降低做出了重大贡献。然而,仅通过现有技术的扩展,实现进一步小型化并以低成本制造复杂的半导体芯片变得越来越困难。佳能通过纳米压印光刻(NIL)这一替代传统光刻技术的新技术,以更低的功耗和更低的成本实现了小型化。但NIL真的有望彻底改变半导体行业?

电路图案小型化的历史

NIL技术不受光波长度的限制,直接采用实体模板转印微结构,随着模板技术的不断提升,分辨率可以继续缩小,最小线宽从14nm突破10nm,确实能为未来继续发展3nm、2nm技术奠定一个继续且连续性的技术发展基础。

除了存储和逻辑之外,覆盖的器件空间还包括CMOS图像传感器、衍射光学元件和元光学元件(MOEs)等。但是比NIL技术本身更难的是其产业链的发展,NIL技术走的是与传统光学光刻截然不同的道路,这将颠覆的不仅是光刻本身,更是整个光刻供应链。

随着摩尔定律逐渐消亡,可以预想,如果传统光学光刻的制造成本与未来科技产品之间的价格矛盾达到难以调节的情况,其他光刻工艺也将受到重视与投资。

佳能如何解决常见问题?

为了实现位置偏差的高精度测量,佳能开发了一种系统,可以实时测量掩模和晶圆之间的位置偏差。通过使用最佳莫尔图案以及与美国佳能纳米技术公司 (CNT) 合作开发的专有光学技术和控制技术,NIL 设备可以以纳米级精度测量和校正掩模与晶圆之间的位置偏差。

TTM 示波器能够实时测量掩模和晶圆之间的位置偏差

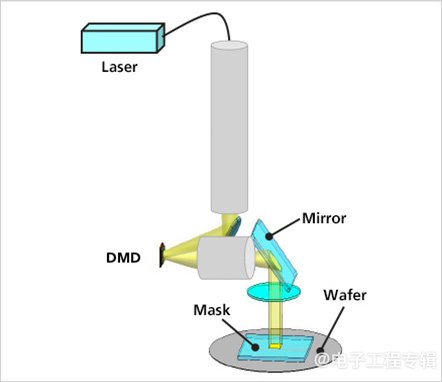

除了能够高精度测量位置偏差信息的技术之外,能够与下层图案对准的匹配技术也很重要。佳能开发了一种专有的匹配系统,通过使用激光照射使晶圆热变形来实现对准。

专有匹配系统

该系统通过控制称为数字微镜器件(DMD)的超精细镜组,可以改变热量输入模式并自由地使晶圆变形。佳能并没有像传统认为的那样假设晶圆的热变形会降低对准精度,而是采用了一种创新的对准方法。

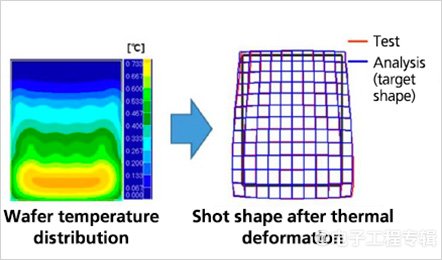

变形后的晶圆温度和形状

“颗粒”污染问题上,佳能是采用超高性能过滤器来消除颗粒,并利用设计技术使空气顺利流入 NIL 设备,尽管其复杂性和许多移动部件。

超高性能滤波器

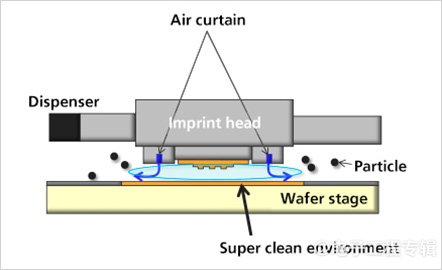

佳能还采用颗粒消除装置来处理设法进入设备的颗粒,并开发了包括气幕在内的技术,该技术用于通过按区域划分区域来划分最重要区域的超洁净环境。

风幕

NIL 技术在DRAM应用上扩大

据悉,铠侠已经将 NIL 技术应用到 15nm NAND 闪存器上,并有望在 2025 年推出应用 NIL 技术的 5nm 芯片。佳能正在尝试将 NIL 技术应用到 DRAM 和 CPU 等逻辑芯片上。

据佳能公布的半导体器件制造中纳米压印光刻(NIL)技术的进展中,在2022 年-2024 年间 3D NAND 使用工艺需要套刻精度 5nm,DRAM 使用设备工艺需要套刻精度 2.8-2.4nm,逻辑器件使用设备工艺需要套刻精度 2.4nm;在 2025-2027 年间,3D NAND 使用设备工艺需要套刻精度 5nm、DRAM 使用设备工艺需要套刻精度 2.2-2.0nm、逻辑器件使用设备工艺需要套刻精度 2nm;在 2028 之后,3D NAND 使用设备工艺需要套刻精度 5nm、DRAM 使用设备工艺需要小于 2nm、逻辑器件使用设备工艺则达到了 1.6nm。而且基于该路线图,高分辨率掩膜正在开发,使 NIL 应用于多个 DRAM 个逻辑设备迭代。

佳能在缺陷检测方面,使用 KLA 2905 检测的随机缺陷密度后,进行缺陷复查。NIL 技术的日常缺陷稳定性满足 3D NAND 大规模生产水平。

纳米压印光刻 (NIL) 作为一个概念已经存在了一段时间,但该技术一直受到缺陷、覆盖和吞吐量等挑战的困扰,不过预计五年前不会产生商业影响,有影响也将主要从存储芯片开始。