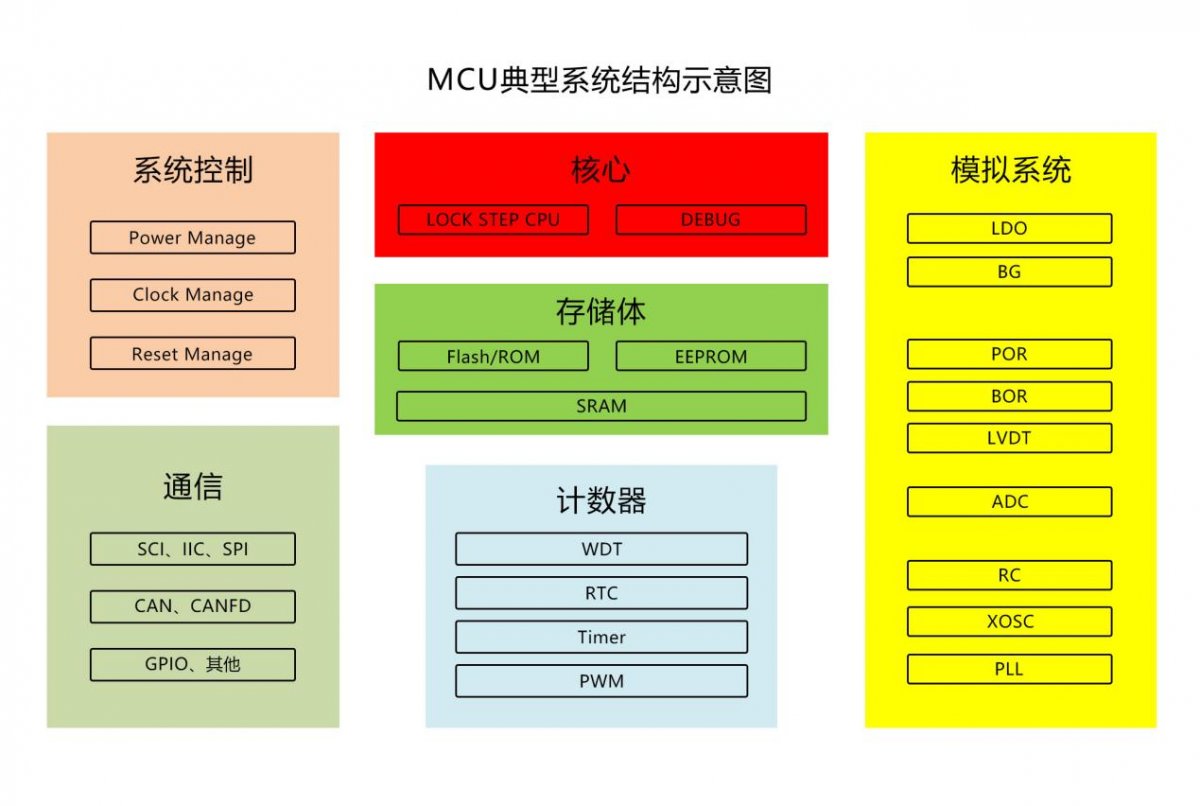

微控制芯片MCU是汽车电子控制系统中的核心组件,其中的存储体是最重要的组成部分之一,主要用于存储程序代码、数据、配置参数等信息。根据存储体类型的不同,车规MCU存储可以分为多种类型,包括ROM、EEPROM、Flash以及SRAM等。由于存储体用于存储MCU运行的数据代码,其故障可能会导致汽车电子控制系统出现严重的事故。因此,不同类型存储体的功能安全非常重要。在车规MCU中进行合理的存储体和控制器的功能安全设计,可以有效地提高汽车电子控制系统的可靠性和安全性。

图1:内嵌存储体的MCU系统结构示意图。

车规MCU中存储功能的功能安全,主要包括防止存储体及控制器本身的故障和防止外部攻击对存储体进行破坏和信息窃取两个方面。为防止存储体及控制器本身的故障,车规MCU需要采用多种技术手段来保证其功能安全,例如,使用业界成熟的ECC技术或使用CRC校验码,可以检测修复错误数据和检测数据完整性,使用备份存储可备用数据等。而为防止外部攻击对存储体进行破坏或数据窃取,车规MCU需要采用加密技术来保护存储体中的数据,例如使用不同种复杂的算法对数据进行加密,控制代码访问及运行权限,条件限制性数据交互等,可以有效地防止外部攻击和信息泄露。

本文在讨论车规MCU的设计开发时,将侧重于功能安全的设计实现。只有在存储体的功能安全得到保障的情况下,才能让汽车电子控制系统更加可靠和安全。因此,存储体及控制器功能安全设计是车规MCU中非常重要的一环,直接关系到汽车电子控制系统的可靠性和安全性。

存储体类型组成

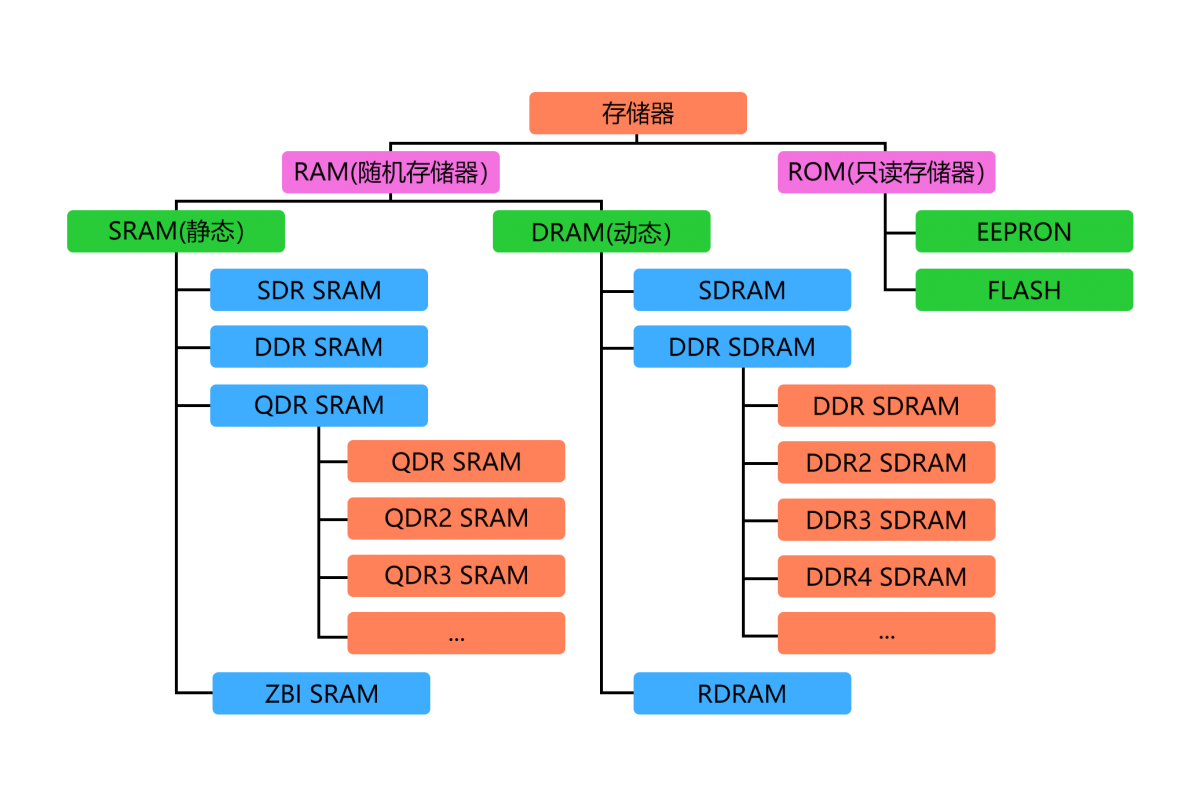

图2:不同的存储体类型。

以汽车域控制多核MCU芯片为例,基于不同的存储体类型,存储体可以分为ROM、EEPROM、Flash以及SRAM等。ROM作为只读存储体,用于一次编程BOOT启动程序后不能再被修改,负责存储MCU芯片上电启动程序代码、初始诊断测试代码和基本控制算法代码等。EEPROM是可擦除可编程只读存储体,它可以通过电信号进行擦写和编程,在汽车域控制多核MCU中,EEPROM通常用于存储车辆识别码、用户设置、故障码、参数等信息。Flash与EEPROM类似,但其擦除和编程速度更快,汽车域控制多核MCU中,通常被用于存储应用程序、操作系统和驱动程序等信息。基于技术发展迭代和市场化验证,目前EEPROM功能逐渐被小容量的Flash替代。SRAM是一种静态随机存取存储体,具有快速的读写速度和低功耗的特点,在汽车域控制多核MCU中,SRAM存储体通常被用于存储缓存、栈和堆等数据。

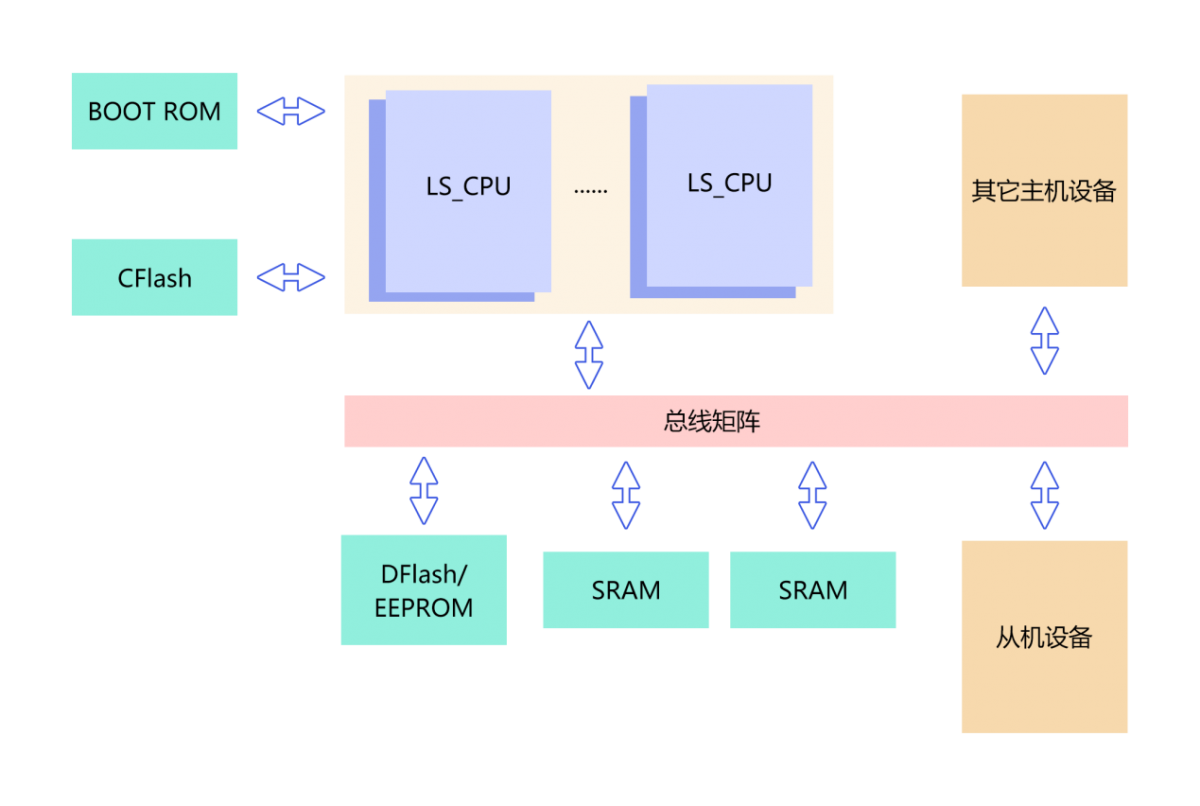

在MCU中的系统架构,ROM存储体通常分为两类:一是内部ROM,即直接集成在MCU芯片中;二是外部ROM,即通过串行或并行接口与MCU芯片相连的外部ROM。SRAM、EEPROM和Flash存储体通常都是内部集成,可以通过串行或并行接口进行读写操作。在复杂处理系统中,由于存储体容量需求巨大,集成至芯片内部已无成本优势,因此通常以独立的芯片形式存在,需要通过外部地址总线和数据总线与MCU芯片相连。

图3:通过外部地址总线和数据总线与外部MCU芯片相连接。

上述每种存储体类型,均需要符合自身读写控制时序的存储体控制器,支持存储体数据的正常存取操作。根据存储体的功能可知,无论时存储体本身还是控制器,任意一个发生故障,均会导致MCU芯片控制和处理功能失效,进而会导致系统故障。因此,有效实施存储体及控制器的功能安全设计方案,可以使汽车电子控制系统更加可靠和高效。

功能安全技术

主要功能安全技术包括:

包含地址信息的ECC

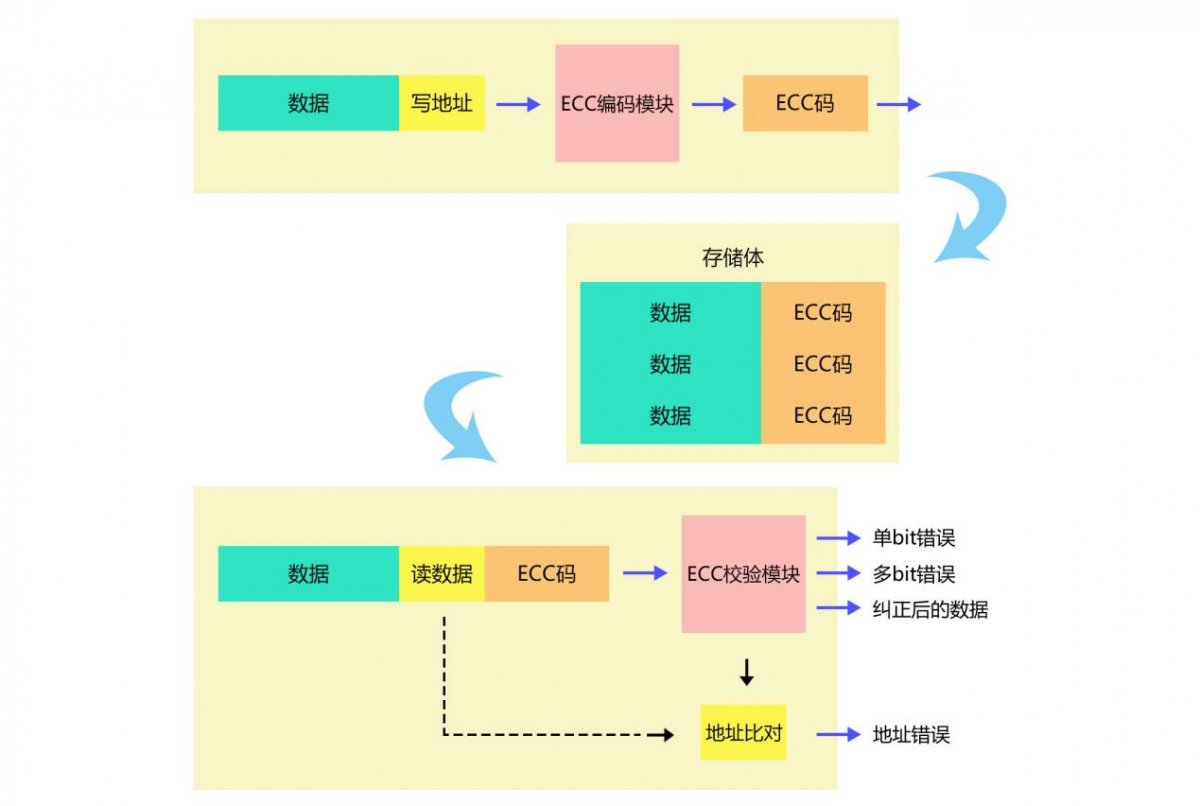

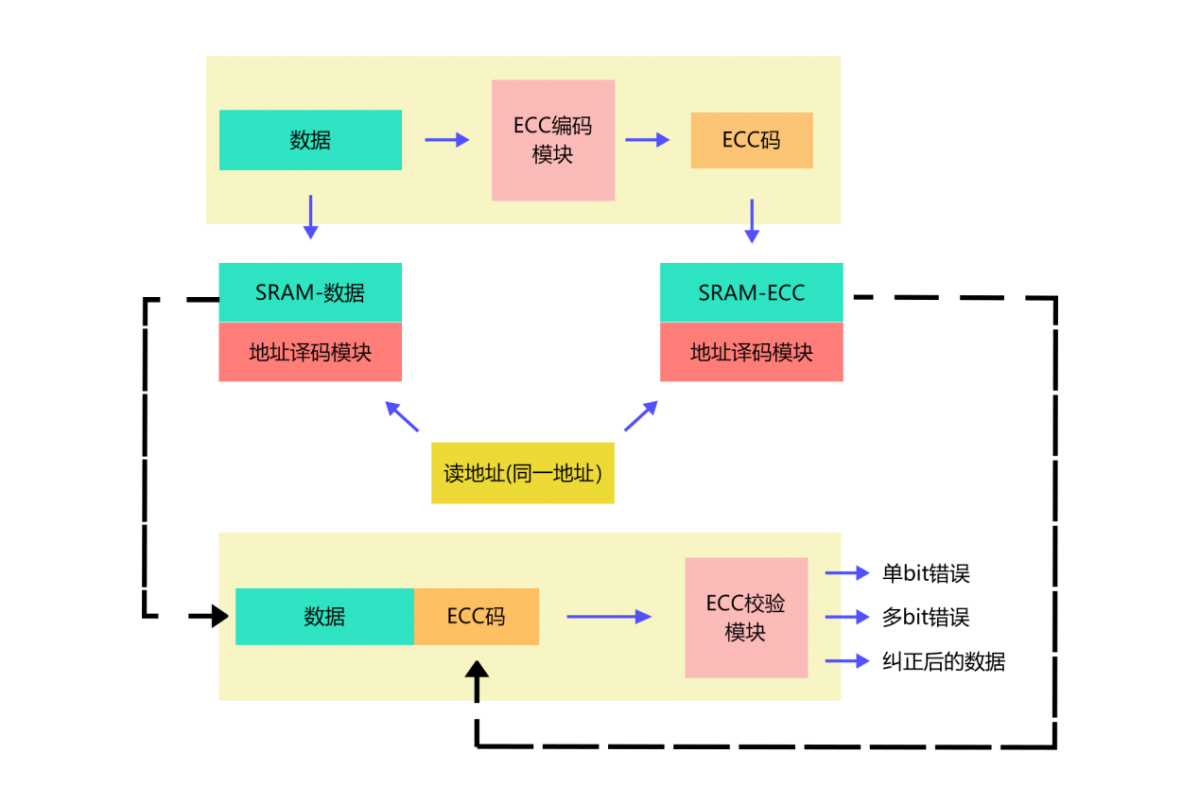

常规MCU芯片中存储体ECC方案,主要对其存储空间中的数据进行处理,查二纠一的算法基本可保证99%以上的故障诊断覆盖率。为尽可能保证安全性,对于复杂MCU、尤其是汽车电子控制中使用的核心控制MCU,甚至设计为查三纠二的ECC算法。常规MCU,其内部存储体容量有限,地址译码电路所进行的译码处理位宽较少。相较常规芯片不同,车规级核心控制MCU的全芯片中,使用了大量的Flash和SRAM等存储体,其存储体控制器地址译码电路涵盖地址区间较大,故控制器译码电路失效率随之增加。因此对于高安全需求的MCU,其存储体ECC方案有所不同。在生成校验位时, 将“写地址”与“数据”一起拼位生成 ECC 校验码, “数据+校验码”一起存于存储体中,写地址本身不存储。数据读出校验时,“读地址+数据+校验码”一起校验。 此设计方案在不明显增加设计成本的情况下,可检测地址译码逻辑单比特失效。

图4:高安全性MCU中的ECC校验。

控制器对存储体的控制效果,体现在正确地址和正确数据的存取。当控制器中地址译码电路故障时,可导致使用错误的地址读取该地址中的数据,而该笔数据本身的ECC校验码正确,无法通过常规ECC检查,最终MCU获得错误数据,造成系统故障。包含地址信息的ECC方案,基于存储体和控制器最终的存取效果,针对数据和地址两个关键点,对整体进行安全控制。

ECC码的独立存储

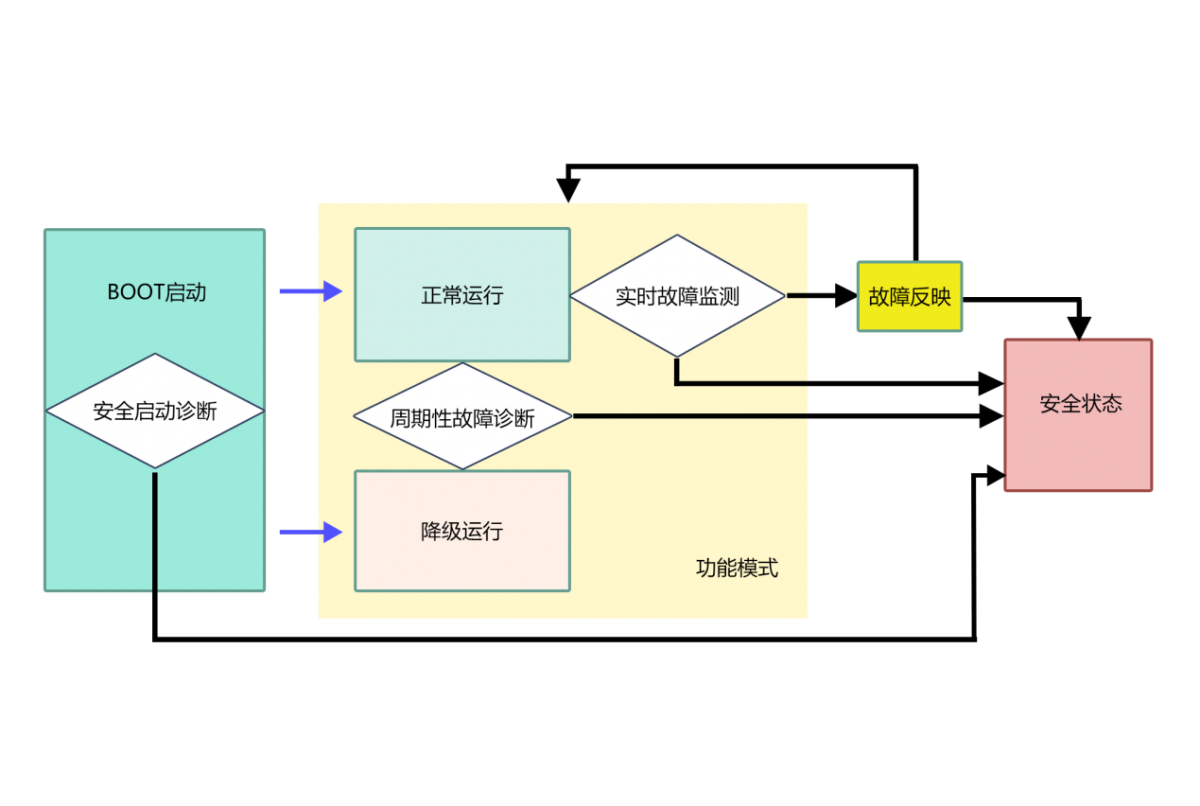

另一种有效的安全方案,是将本身的数据和ECC码使用独立的存储体进行存储。MCU芯片中SRAM作为数据缓存,在系统集成过程中会例化多个存储空间的SRAM模块,而不是统一放在一个巨大地址空间的SRAM接口中,这样有效保证多主机进行数据访问处理的高效性。因此ECC码的独立存储方案,尤其适用于SRAM的功能安全设计实现。

图5:利用数据和ECC码的独立存储来改善功能安全。

以SRAM而设计实现为例,每一笔数据生成对应ECC后,按相同的地址,分别存储数据的SRAM和存储ECC码的SRAM。MCU芯片发出读地址读取某一笔数据时,同时将该地址对应的存储ECC码的SRAM中对应该数据的ECC码读出,并通过ECC校验模块进行校验。当地址译码模块译码故障时,实际上用同一地址读取的数据和ECC码会发生不匹配的情况,最终导致ECC校验时发现ECC码错误。因此此时的地址译码模块的故障将以ECC数据校验错误的形式反馈,并不区分是存储体的故障还是地址译码电路的故障。在实际系统层级功能安全应用时,将存储体及控制器看作整体,安全响应最终是以数据错误的形式表现,有助于提升高层级处理的效率。另外的,ECC码被分成两个物理SRAM存储区域,这种方案提供了物理上SRAM存储区域和控制模块,也有助于降低物理多位故障导致逻辑多位故障的概率、共因失效概率和地址译码模块瞬态干扰导致的安全机制失效的概率。

ECC校验功能的诊断

存储体ECC技术方案作为防止存储体及控制模块发生单点故障的安全机制,需要采取相应技术措施来探测、识别或诊断其本身的问题,尽量减小潜在故障的概率。虽然ROM、SRAM、EEPROM和Flash存储体数据在MCU芯片正常工作过程中均可受到ECC校验的保护,但不同类型的存储体其实际工况不同,因此对于ECC编码和校验模块的诊断措施也有区别。

图6:ECC编码校验功能方框图。

在BOOT启动阶段和功能模式运行阶段,SRAM和EEPROM都可进行数据访问,且MCU芯片应用过程中,数据可实时修改。对于SRAM和EEPROM的功能特性,其ECC校验模块可通过实时故障注入的方式进行诊断。故障注入开启后,MCU可通过程序读取SRAM和EEPROM的数据和ECC校验码,并将数据段通过注入修改,连同ECC码送入ECC校验模块,可诊断ECC校验模块是否可正确检测到ECC单比特错误、多比特错误和单比特纠错功能。

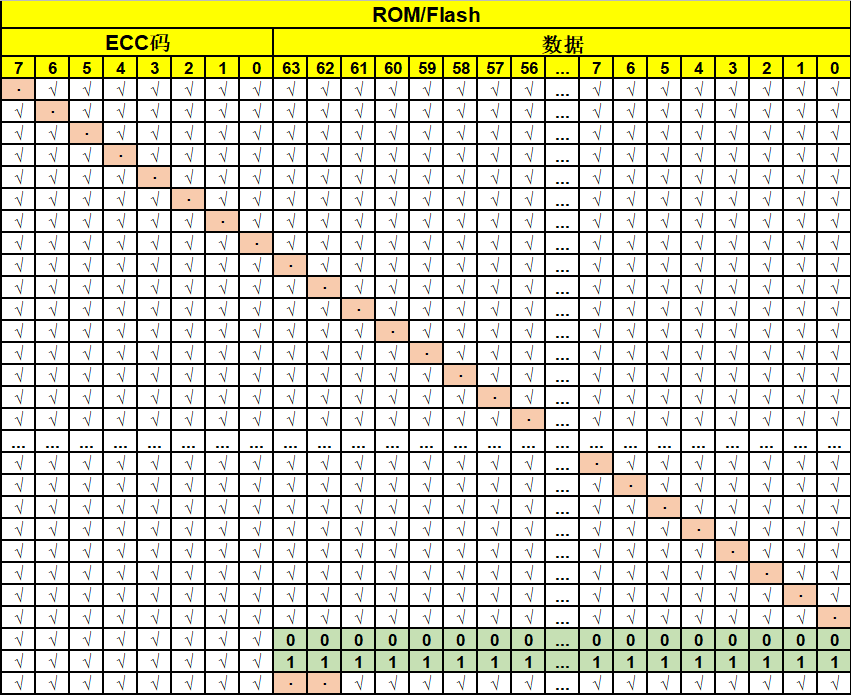

故障注入方案需要ROM或Flash中软件程序正确执行,因此难以用于诊断用于存储软件程序代码的ROM或Flash的ECC校验模块。对于ROM或Flash的ECC校验功能的诊断,可以通过在ROM或Flash存储体中建立ECC测试区域,并事先将用于ECC校验功能诊断的测试数据编程到ROM或Flash中。该区域根据实际的ROM或Flash的数据位宽,遍历单笔特错误,全0数据、全1数据,双比特错误、多比特错误的情况。当进行ECC诊断时,程序主动读取该测试区域的数据,ECC校验正确的情况下将触发ECC错误正常响应。

图7:ROM或Flash存储体中的ECC测试区。

其它关联协作技术

MCU芯片中实现存储单元功能安全可结合其它技术方案相互协作,提高系统的可靠性和安全性。在线MBIST通过测试引擎生成特定的测试模式来激励存储体,然后读取和比较存储器的输出数据,以验证存储器的功能和可靠性。测试模式可以包括不同的数据模式、存储器访问模式和写入/读取序列等,可快速检测存储器中的故障,并提供准确的测试结果。另外,MCU芯片可采用MPU来保护存储体,用于限制非法访问。MPU可以设置存储器的访问权限和地址范围,确保只有经过授权的程序才能读取和写入存储器中的数据。通过MPU,芯片能够有效防止恶意攻击和非法访问导致的信息泄露或篡改。此外,MCU芯片对存储体中数据还可使用数据E2E校验来验证数据的完整性,通过在数据传输的起点和终点分别添加校验码,检测数据在传输过程中是否被篡改。

实现存储体单元的功能安全,从合适的技术层级和功能层级进行分析,考虑安全机制的技术结合和措施的共同作用,评估安全方案在实现功能安全等级目标的适应性,用相对低的成本以达到合适的诊断覆盖率和安全效果,提高芯片的可靠性和安全性,确保系统能够有效防范单点故障和潜在故障的风险。

本文为《电子工程专辑》2023年9月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅

- 功能安全技术总结的很全面!