I3C可能很快就会取代I2C而成为中低速率串行通信的行业标准,并成为转换器和传感器等嵌入式设备中所使用的主要接口。在许多新I3C主从设备正在面世的同时,未来I2C可能还会继续使用。正因为如此,工程师在系统中可能会遇到I3C与I2C混用的情况。

此时,也许有工程师会怀疑,I2C设备能否在I3C总线上工作?简而言之,答案是肯定的。但是,确实也有一些后向兼容性方面的限制。在这些限制中,最复杂的是时钟延展。

I3C和I2C之间的差异

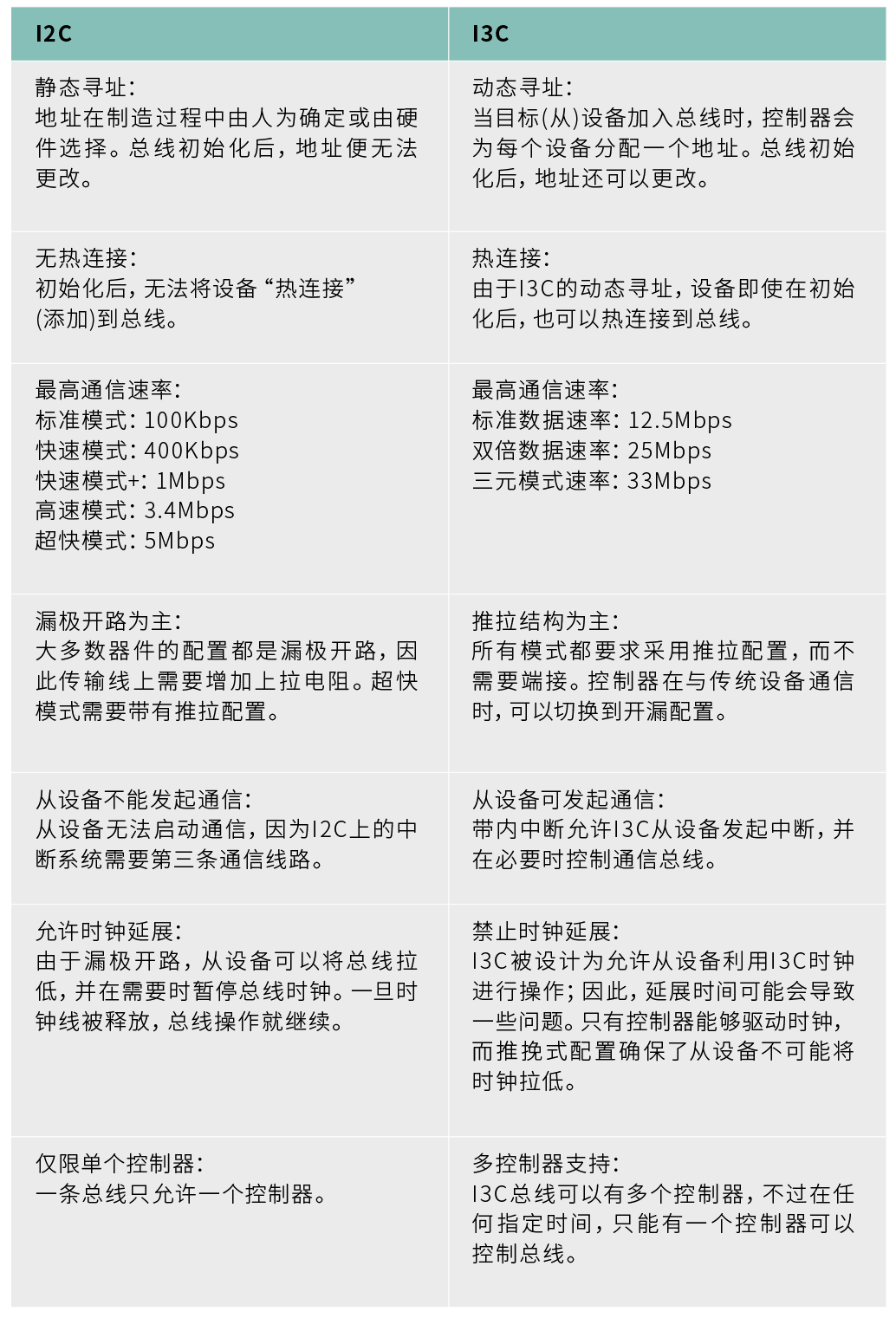

I3C是由移动产业处理器接口(MIPI)联盟创建的,初衷是为了克服I2C的许多不足。但这两个协议确实有很多不同之处,表1中对这两种协议进行了比较。

表1:I2C和I3C的比较凸显了这两种通信协议之间的差异。本文资料来源:TI

尽管与I2C相比,I3C有许多差异和优势,不过MIPI联盟还是尽量使I3C向后兼容I2C。这意味着两种协议的控制器和目标设备可以在同一总线上共存, I2C和I3C能够混用。

I3C向后兼容性的局限性

虽然向后兼容性是新协议开发过程中的主要目标,但I3C并非完全向后兼容I2C。一些显著的区别如下:

•Glitch滤波器

Glitch滤波器,有时被称为毛刺滤波器,用于滤除通信总线上的各种无用噪声。I2C设备在串行数据(SDA)和串行时钟(SCL)线上采用这类滤波器,可以防止对数据和时钟的干扰。故许多I2C设备已经在每条串行线上内置了50ns的毛刺滤波器。

由于I3C支持更高的通信速率,故没有在I3C中内置50ns毛刺滤波器。根据I3C规范,所有传统I2C设备都需要采用50ns毛刺滤波器。如果I2C设备没有内置该滤波器,则需要在外部利用分立元器件设计一个滤波器。

•有限的速率模式

在I2C协议中,具有时序和最大通信速率各不相同的几种速率模式。例如,标准模式支持高达100Kbps的比特率。为了使I2C能够在这些速率下正常通信,就必须遵守相应速率模式下的时序规范。

每种速率模式下,对设置时间、保持时间、上升时间和下降时间等参数都有最基本的要求。I3C并不支持I2C提供的所有速率模式。仅支持其中的两种速率模式,分别是快速模式和快速模式+。

为满足这一要求,I2C必须工作在这些速率模式下。当I3C控制器与I2C目标设备通信时,控制器将调整总线速率,以适应这类较慢的通信。只有在与I2C目标通信时,I3C控制器才会减慢总线的速率,而与I3C目标通信时,总线速率则不会降低。

•时钟延展

当设备之间进行通信时,可能会出现这样一种情况,即当一个设备要读/写数据时,要传输的数据尚未准备好。在这类情况下,一些I2C设备会利用一种称为时钟延展的方法来暂停时钟(注意,并非所有I2C设备都支持时钟延展),从而允许更多的时间来满足某些时序要求。例如,对于I2C来说,进行通信和模数转换(ADC)采样时,必须采用单独时钟。而I3C的操作中,所支持设备完全独立于SCL时钟,故I3C规范禁止采用时钟停滞。因此,为了与I3C总线兼容,支持时钟延展的I2C设备必须在无延展的时钟频率上工作。

时钟延展深入分析

I3C向后兼容的前两个限制很容易解决:即添加毛刺滤波器或改变通信速率,即可满足这些要求所需。然而,时钟延展方面的需求则更为复杂。由于I2C是漏极开路,因此在I2C中,可以简单地将时钟线拉低,并将其保持在低电平,以提供必要的时间,直到所请求的数据准备好为止。而当时钟线被释放时,控制器继续驱动时钟,并使通信恢复正常。

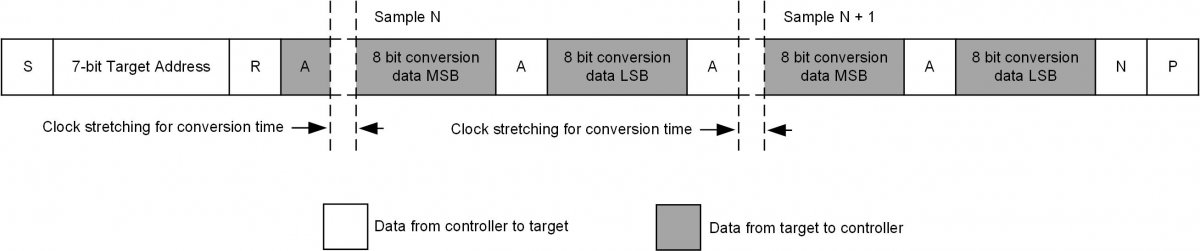

仍以ADC为例。ADC对获取数据的转换需要一个最小时间,称之为转换时间。如果转换时间超过启动读取消息确认(ACK)与下一个时钟沿之间的时间量,则ADC将需要更多的时间来完成转换。在这种情况下,ADC通过将时钟拉低来暂停时钟,直到转换完成。ADC然后释放时钟,并在下一个时钟边沿开始传输转换数据。

图1所示为一个12位ADC转换数据的I2C消息传输示例。请注意,时钟延展发生在每个数据块发送之前,以便留出额外的时间来完成模数转换。此外,支持时钟延展的设备,可能不会在所有时钟频率上都进行时钟延展。因为时钟延展是一种用于满足最小时序要求的方法,所以,可以将时钟减慢到无需延展即可满足时序要求的程度。较慢的时钟使设备有更多的时间来获取请求的数据,从而没有必要再进行时钟延展。

图1:I2C时钟延展条件下的ADC转换数据传输。

如何确定时钟延展的时间

确定I2C开始时钟延展的频率,对于确保其在I3C总线上的正确运行非常重要。数据表可能没有明确注明时钟延展的起始频率。不过,根据数据表中提供的其他信息,工程师可以计算得到此阈值。

以ADS7142为例,它是一个12位逐次逼近寄存器型ADC,其工作独立于I2C时钟。数据表指出,当转换时间大于SCL低电平时间时,将产生时钟延展。为了简化计算,假设时钟占空比为50%,该值位于快速模式的范围内。

根据这些信息,可以得到:

tCONV=转换时间

TSCL=I2C时钟周期

如果tCONV≥1/2 TSCL,有时钟延展

如果tCONV<1/2 TSCL,则无时钟延展

数据表还规定,当在手动模式下配置自动排序时,转换时间为1.8µs。因此,工程师可以计算设备开始时钟延展的频率:

1.8μs≥1/2 TSCL

3.6μs≥TSCL

1/3.6μs≥1/TSCL

277.7kHz≤fSCL

fSCL≥277.7kHz

基于这些计算,ADS7142 ADC的时钟延展将出现在277.7kHz的时钟频率上或更高。因此,为了在I3C总线上成功通信,在与ADC通信时,必须将时钟频率配置到低于277.7kHz。

I3C总线上的时钟延展

为了验证上述计算,将ADS7142连接到用于读取转换数据的I3C控制器。模拟电源电压为3V,将ADC的输入连接到1.52V,所产生的转换代码约为0x81B。分别在高于和低于阈值的时钟频率上对ADC进行了测试,以便对功能进行检查,并对计算结果进行验证。

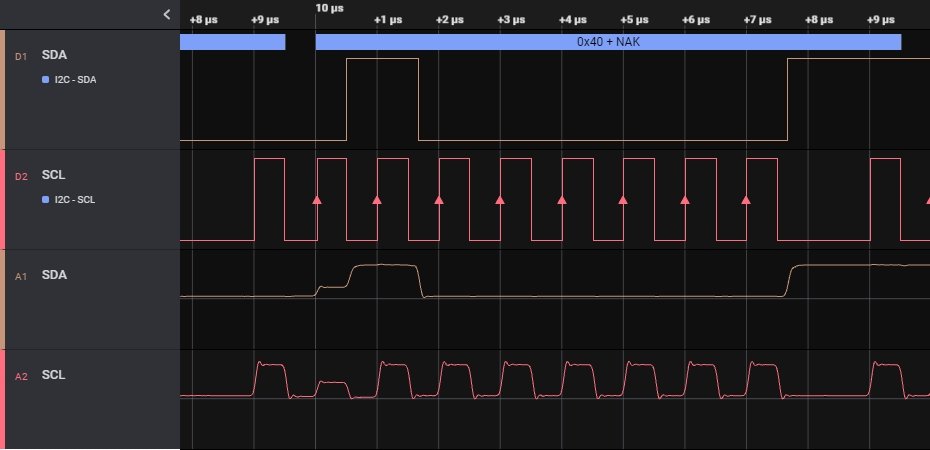

图2所示为ADC在I3C总线上发送的消息,其中包含两个12位转换,时钟频率高于时钟延展阈值(500kHz)。在该速率上,设备将尝试在传输转换数据之前进行时钟延展。如图所示,转换的第一个字节发送是正确的,而转换的第二部分就不正确了,且控制器不发送传输确认(NAK)。

图2:选用500kHz时钟时I3C总线上的ADC测量快照。

为了进一步研究,对传输过程中的模拟电压电平进行了观察。图3更详细地显示了当ADC试图在I3C总线上进行时钟延展时发生的情况。底部的两个波形是SDA和SCL的模拟测量值。时钟脉冲1是来自先前消息的ACK。时钟脉冲2是转换数据传输的第一个时钟脉冲。

图3:I2C目标设备试图在I3C总线上进行时钟延展时发生的情况。

请注意,这个时钟脉冲的模拟测量值大约是其他时钟脉冲振幅的一半。这就表明,ADC试图将时钟拉低,而与此同时,I3C控制器则将时钟驱动为高电平。控制器能够克服目标影响并继续驱动时钟,然后是NAKed消息,以指示目标违反了I3C协议。

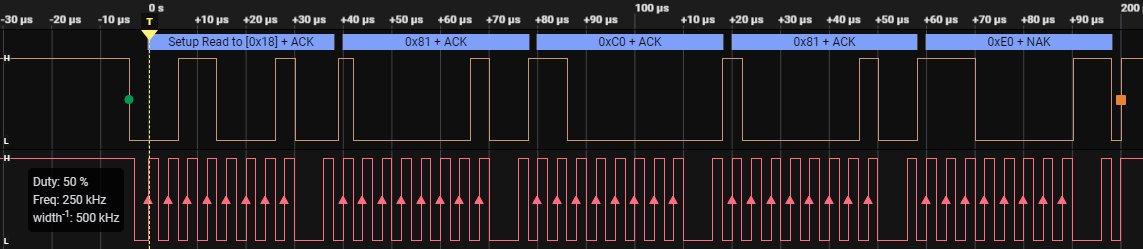

接下来,又在低于时钟延展阈值的频率上,对该设备进行了测试。图4显示了时钟速率为250kHz时的I2C消息。在这个时钟速率上,设备将不会出现时钟延展。这两个转换都产生了预期的代码,并且每个消息都得到了确认。该测试表明,当ADC在无需时钟延展的时钟频率上运行时,其在I3C总线上可以正常工作。

图4:时钟为250kHz时I3C总线上的ADC测量快照。

正确理解I3C向后兼容性

尽管I3C越来越流行,不过I2C仍是事实上的标准,只是两种协议混用的情况将变得更加常见。在这种情况下,允许工程师继续使用熟悉的I2C协议,同时也允许使用较新的I3C,以这样一种方式设计系统是有益的。

这就是充分理解I3C向后兼容性的局限性变得尤为重要的地方。虽然I3C不允许时钟延展,但I2C设备可以在I3C总线上通信,只要被配置到不发生时钟延展的速率即可。在I3C总线上使用I2C设备可能非常有益,因为这样做可以保持I2C协议的简单性,同时有助于实现更多经得起未来考验的设计。

(参考原文:The I3C compatibility with I2C and clock stretching)

本文为《电子工程专辑》2023年8月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅