今年SEMICON China展会上,“先进封装”真的是个热门话题,我们接触的几家半导体制造与封测设备上游企业,普遍在谈fan-out先进封装技术。

前不久我们刚刚撰文谈过fan-out扇出型封装类型——有关什么是fan-out,以及快速浏览从传统封装到先进封装的发展史,建议首先阅读这篇文章。

Fan-out在消费电子设备上,最知名的应该就是iPhone的AP SoC了——苹果基于自家手机产品的高利润与高出货量,相比其他手机AP SoC更早采用台积电InFO(integrated Fan-Out)先进封装工艺。不过实际上,fan-out有两个不同的大类,分别是wafer level晶圆级的,以及panel level面板级的。

而iPhone的AP SoC属于前者,我们此前讨论比较多的也都是前者。事实上,后者也有典型代表:2018年年中,SEMCO(Samsung Electro-Mechanics)推行首个panel level fan-out产线,用于三星的智能手表,将AP和PMIC放到了一起——既然是fan-out,对应的就有了RDL(redistribution layer)层,这一例RDL有3层,背面层的线宽、线距分别是7μm-8μm。

前不久的SEMICON China展会上,我们特别采访了Manz集团亚洲区研发部协理李裕正博士,聊了聊panel level fan-out的未来。借着这个机会,顺带也做一部分相关fan-out先进封装技术的科普。

Manz集团亚洲区研发部协理 李裕正博士

最初的降本增效预期

翻看5年以前谈Fan-Out Panel Level Packaging(以下简称FOPLP)的技术文章,会发现一件有趣的事。一方面是最初一部分人认为,FOPLP面向的应用和Fan-Out Wafer Level Packaging(以下简称FOWLP)是一样的。而随着时代与技术的发展,由于FOPLP有着显著更高的材料与面积利用率,而且还能提升生产吞吐量,未来是有机会逐渐替代FOWLP的。

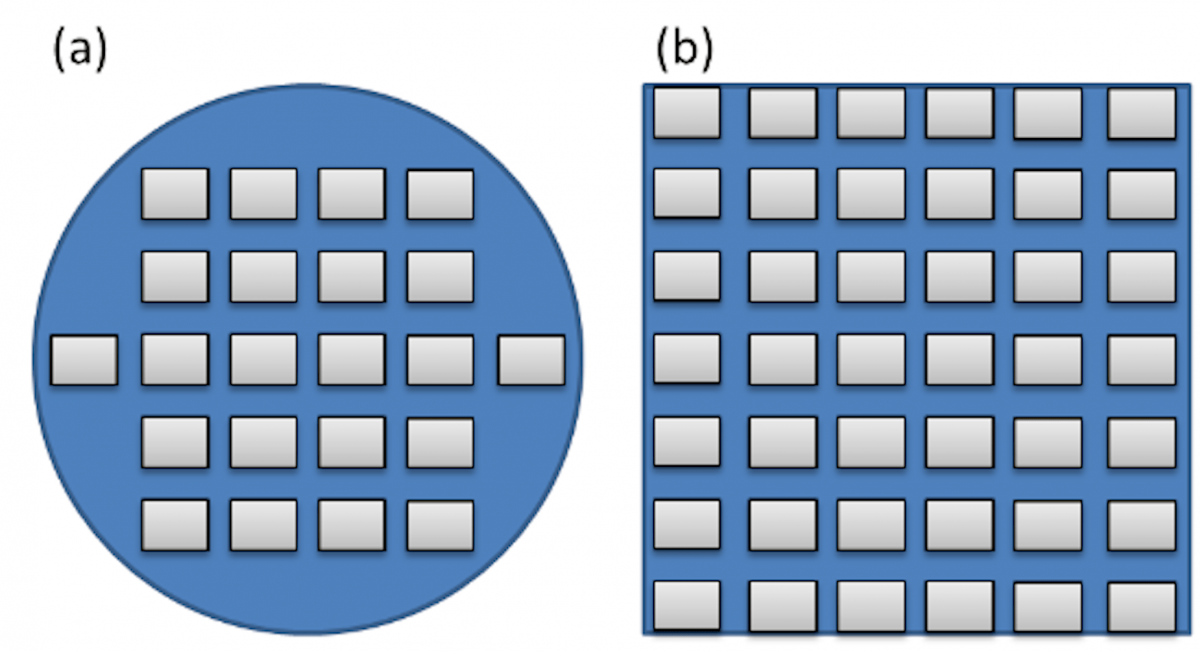

最初有这样的设想原因也很简单。从fan-out封装的原理来看,是在一片wafer上的die都做好之后,先将这些die切好,然后用pick-and-place系统,将这些die再放到一片新的carrier载体上——这个载体,对于FOWLP而言就是像wafer一样圆形的环氧树脂模具化合物(epoxy mold compound),或者行业内常称其为reconstituted wafer。

这也是WLP这个词里面wafer level的来由——载体wafer也是类似差不多200mm或300mm的圆形形态,这部分后续也用来做RDL层——RDL层的存在,是这一类封装技术与flip-chip芯片倒装的最大差异之一。实际上,RDL也是Manz(亚智科技)这家公司的着力点所在。

而对于FOPLP而言,在fab做好的die,切下来就不是放到载体wafer上,而是放到载体panel上——所以叫panel level。这里的panel,与前述wafer最大的差异包括,形状变成了方形,与此同时面积可以增大——如此一来,切割后的芯片die,放到panel上,就有了更高的面积利用率,且一片panel可以容纳更多的die。

FOWLP与FOPLP,来源:日月光

来源:STATS ChipPAC & Rudoph Technologies

前两年STATS ChipRAC和Rudoph Technologies出过一篇paper,特别提到了,相比于300mm的wafer,一片500x500mm的panel可以处理的die数量,是其4.54倍;而如果把panel做到600x600mm,则吞吐又扩大到了wafer的6.5倍。那么显然对于fan-out封装而言,达成了高很多的生产效率,而且也能带来更低的成本。

去年9月,Manz甚至还宣布了克服翘曲(warpage)的挑战,打造业界最大的700x700mm面板,“再创面板级扇出型封装生产效率的新里程碑”。这对FOPLP而言,的确是大事件。

但实际上,这两年市场已经不再将FOPLP视作FOWLP的替代品了。上述有关panel level的优势的确是存在的,但panel level本身也存在一些短期内很难克服的技术障碍。

李裕正博士在对谈中就提到,panel level和wafer level两者并非谁取代谁的关系:“我认为它们是对应于不同的市场。wafer level还是有细线宽/线距、解析度在良率方面的优势,毕竟做的时间早很多。”“从Yole之前的市场报告来看,fan-out大概只占到先进封装年度营收的1/10左右,而panel level又只占fan-out的1/10。”

就我们所知,FOPLP遭遇的困境有几点,首先是标准的不统一:panel尺寸的标准。这个领域在发展过程中涉及到相当多的panel尺寸,如300x300mm,457x610mm,510x515mm,600x600mm,当然还有我们看到Manz最新的700x700mm。李裕正就举例提到不同的尺寸会提供给有对应需求的封测厂/IDM客户。

但标准不统一造成的很大问题就是设备供应商无法简单抉择,封测厂/IDM也会开始观望。因为绝大部分市场参与者都没有那么多资源来支持所有的panel尺寸,且标准分散就意味着客户基数的分散。像这样的技术要做起来,都是需要走量的,如果没有量做支撑,对应的技术自然难以发展。

其次是大尺寸panel面临的一些实际技术问题,比如说翘曲(warpage)、5μm-5μm(线宽-线距,line-space)及以下高密度RDL的技术挑战。因为从wafer level到panel level,并不是简单把工艺做等比例的调整就好,包括pick and place、die bonder之类的问题;如何处理大型panel,以及对应产生的warpage,以及一致性、精度等问题,工艺控制工具都面临挑战;检测量测技术与wafer level也存在不同等等。

也因为如此,抛开市场不谈,FOPLP要实现更高的分辨率,更小的线宽线距,在技术层面的难度会非常大——所以当前行业也更倾向于将FOPLP放在线宽、线距大于FOWLP的定位上;何况如李裕正所说,FOWLP发展和起量的时间也更早。

所以在CapEx固定成本问题上,建起一条FOPLP产线的费用可不低,收回成本自然需要量来做支撑。这里还有个问题,就是对于大型panel而言,小批次的lots就意味着材料与资源的浪费。则“起量”在FOPLP的天平上会是更重的砝码。

另外就是FOWLP面临的技术问题,FOPLP也都需要面对。前面提到的翘曲问题对FOWLP是个麻烦,而FOPLP的大panel应对起来显然更麻烦;还有像是die shift之类的问题,恰巧最近采访另一家上游供应商ERS时,ERS多少也向我们提起过——这家公司实际上也做FOPLP相关的设备。

寻找新的定位和应用

FOPLP在实际发展中遭遇的问题,应当是这一领域市场参与者调整发展战略的关键。“Panel level最初在投入的时候,厂商都没什么经验,技术也没那么成熟;加上标准不统一,2016年以后,一些厂商就慢慢发现问题。”那么FOPLP的机会又究竟在哪儿?

“至少目前在中高阶的IC封装上,(FOWLP)看起来还不成熟。而中低阶应用的量非常大。”李裕正说,“不少中低阶应用在用QFN封装,或者wire bond。这些技术很成熟、成本也低,毕竟如果封装成本很高的话也进不了这些应用领域。”

“但我们慢慢看到,比如车用电子——从油车变电车,电车要发展ADAS、自动驾驶。车里的电子元件越来越多,IC也越来越多。这些IC过去都用wire bond来封装,现在会慢慢看到发展瓶颈。”李裕正所说的瓶颈,是指性能、能效、发热多方面的。

“包括功率IC、第三代半导体,不同应用对功率密度(power density)的要求一直在提高。用QFN、wire bond,发热、性能表现都不是那么好了。”

“那么很自然,就需要‘往上看’还有哪些技术可以用,包括线路路径要缩短、导电性更好。”Wire bond引线键合“往上”的先进封装,自然就主要包括了flip-chip芯片倒装,以及FOWLP和FOPLP。再往上就是成本更高、基于interposer的2.5D封装了。

基于成本方面的考量,“panel level是很有竞争力的技术,每单位面积成本一定比wafer level要低,实际上也比flip chip更低——是存在成本优势的。”

在此我们特别问到李裕正博士,FOPLP为什么能做到比flip chip芯片倒装更低的成本,毕竟前者相较后者新增RDL层无论如何都存在工艺步骤增加。李裕正回答说:“一是fanout封装面积缩小了(所以单位面积成本变低);其次flip-chip的BT板(bismaleimide triazine substrate)没有想象中那么便宜——尤其如果BT板要做10μm-10μm解析度,良率还很低,成本自然会上升。”

“相对的,如果是10μm-10μm的fanout,相比于20μm-20μm的BT板,前者可能(互联线路)只需要两层就搞定了,而后者需要6、7层。而且BT板还很厚,如果是40μm,上下分别加20μm,总共80μm;但对于fanout的RDL层而言,可能30μm就搞定了。”更薄的封装对散热也有显著好处。

“甚至前年Yole发布有关fanout的报告,还有厂商宣布在不考虑良率的情况下,panel level fanout的成本可以比QFN再低个20%——当然这个数字是指双方良率相同的情况下。”

虽然20%听起来让我们有些惊讶,该数值应该预设了一个前提条件,即FOPLP达成了对应量的量产预期,且技术真正步入到成熟阶段;而且没有加上CapEx的前期成本投入;但这个数字多少还是让人看到了FOPLP的市场希望的。

“其实目前panel level市场营收相比flip chip还是很低。所以我们只需要吃下flip chip 10%的市场,就相当于把fanout的营收翻倍了。”李裕正在谈到FOPLP的市场机会时笑言。

我们总结,这个思路是FOPLP的市场玩家,期望在技术走向成熟、成本更低,以及很多应用在传统封装技术下表现出效率、性能的瓶颈时,FOPLP可以吃下更多的市场。如此也以成本优势,避开了与FOWLP的正面竞争。

现阶段在李裕正看来,功率IC——诸如SiC、GaN等,以及RF射频为代表的芯片封装都非常适合采用FOPLP技术。在垂直市场上,汽车电子尤其被看好——李裕正多次谈到了这部分市场。

功率IC和RF射频系统应当是最具代表性的应用方向。对于RF射频系统而言,“RFFE的元件集成度比较高,传统封装方案一颗一颗摆在载板或PCB板上,模组是比较大的、传输距离远、也耗电;而fanout显然能够解决这些问题,那么panel level成本优势就会体现出来”;

功率IC更好理解,“电车对功耗越来越敏感,要做省电、性能又好的IC,就需要用到相对高阶的封装方式——在良率一样的情况下,成本最低的就是panel level fanout”。事实上,李裕正告诉我们现如今移动市场的大部分PMIC都已经在用fanout封装了,就是功耗敏感的原因,“fanout封装的IC传导路径短,互联性能整体表现会比flip-chip更好。”

“我们的技术平台建立之后,就可以抓住新的市场机会。对于这些新的市场而言,传统封装已经无法满足要求。”在李裕正看来,FOPLP在未来的发展中,是可以真正量产5μm-5μm的工艺水平的,用以满足更多中高端应用的需求。虽说“panel level现在是大约>10μm的程度,跟BGA的解析度差不多”,但基于潜在成本优势,FOPLP的机会仍然很大。

有关目标客户和解决方案

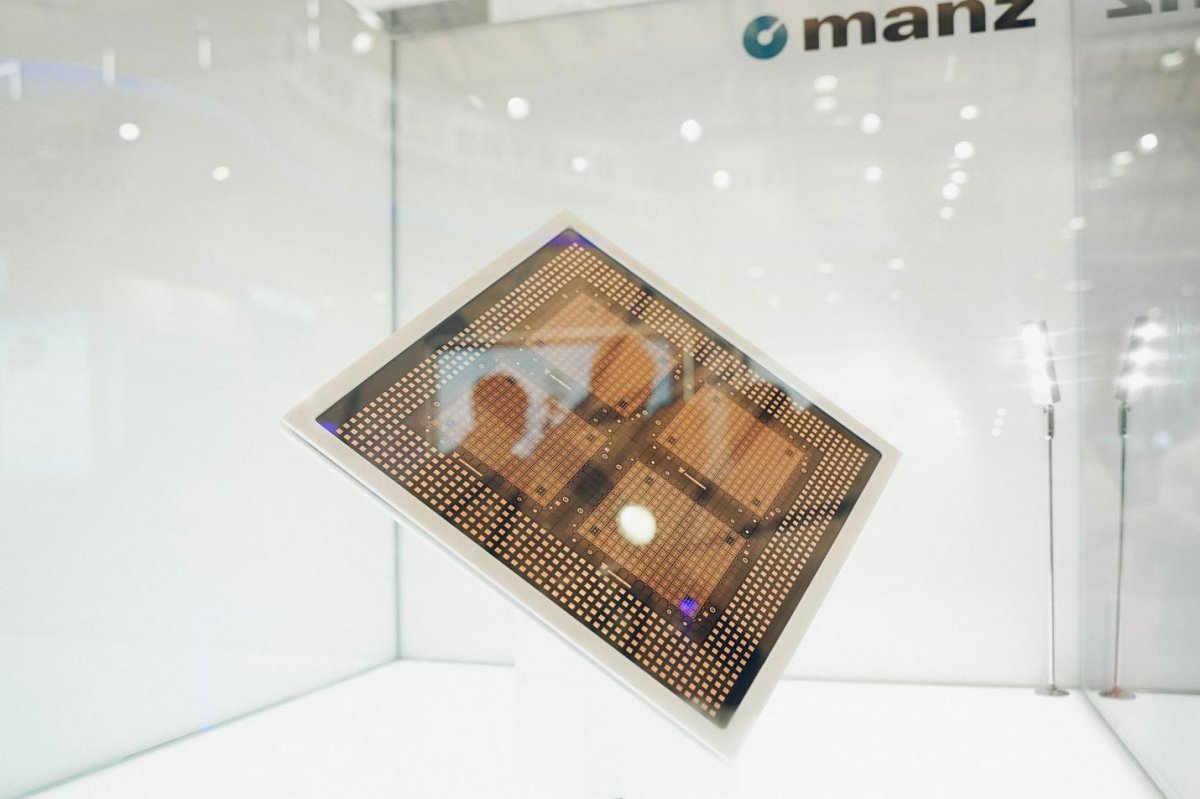

最近Manz开始“协同制程开发、设备制造、生产调试到售后服务规划,实现具可靠性的板级封装FOPLP整厂解决方案”,这里的关键词是“整厂解决方案”。

李裕正说向下游客户提供的是turnkey solution,“从头到尾”的解决方案。其中包括了Manz本身不做的设备和流程,自然也有Manz拿手的部分比如电镀设备,“我们和那些有制程技术know-how的solution provider一起,和上下游厂商共同合作,解决技术问题,真正做到turnkey solution。”在我们看来,这对FOPLP的发展会有非常大的帮助。

“当然如果客户要买单独的设备,我们肯定也不会拒绝,不仅是为了营收,也对技术、行业的发展有促进作用。”

有关产线的问题,在和李裕正的对谈中,我们也聊到了打造FOPLP产线的CapEx固定成本投入问题。因为基于设备的可复用性低,像台积电这样已经构建起FOWLP封装生产线的厂商不大可能转投FOPLP。李裕正坦言,原本在做FOWLP的厂商短期内可能不会考虑FOPLP,这与成本、利润、产能分配等方面的问题都有关。

“这几年摸索下来,我们认为应该要转换一下思路。”所以Manz现如今主要考虑那些还没有做先进封装基础设施的客户。

比如“在车用领域,我现在对IDM厂商有信心。”李裕正在谈目标客户时举例说,“很多IDM可能就只是做wire bond和QFN——这些传统技术在提升上已经遇到了瓶颈,正在寻求新的技术方案。”“flip chip成本还是高了。而且前两年疫情期间出现了基板短缺、成本上升的状况,这对我们而言也是机会;部分客户就会去评估效能和成本。”FOWLP成为一个很不错、可发展的突破方案。

总结起来,除了FOPLP将部分替代原本更低端包括wire bond引线键合在内的传统封装方案——尤其在有更进一步性能、散热、效率需求的应用上;“大家都在往前走,wafer level fanout其实也需要和更高阶的interposer竞争;那么我们继而也要往前走,可以吃下一部分原本可能属于wafer level fanout的市场;未来的市场机会很大。”

在李裕正看来,FOPLP虽然“不能说它完全标准化,但已经在慢慢收敛制程”,“在投入厂商逐渐增加的情况下,材料、设备的支持各方面都在增加,成本也在慢慢下降,良率在提高。”虽然他没有列举FOPLP上下游市场参与者具体的行为动作,不过在我们看来,Manz本身这两年的投入和动作都已经足够说明问题了。

除了前文就已经提到这些年还颇具标志性意义的打造业界最大700x700mm生产面积的FOPLP封装技术RDL生产线、持续投入开发关键电镀设备,这次参加SEMICON China也同时宣布两项技术上的突破:

其一是RDL层的镀铜厚度达到100μm以上,让封装体积轻薄化的同时,保持导电性、电性功能与散热性;其二是“开发大于5 ASD的高电镀电流密度规格,快速增加镀铜的速度,提升整体产能”。Manz在新闻稿中提到,这些技术突破尤其为“车载芯片提供了最佳生产解决方案”——反复提到汽车,看来对汽车市场是真的很看好。

前不久Manz对这些已经有较为详细的信息发布,也包括作为RDL环节的设备与解决方案供应商,打造FOPLP的整厂解决方案;以及达成92%电镀铜均匀性的技术努力(李裕正在采访中就特别提到大面积panel的均匀性非常难控制);以及尝试达成最小5μm-5μm制程规格等等,前文多少都有提及,都是在为FOPLP生态的持续进步添砖加瓦。

“我想今年(市场)会有比较明显的结果。一旦有厂商宣布(FOPLP的)规模量产,我们的技术就有机会变成标准的技术,有标准的流程、标准的设备。”李裕正很有信心地谈到,“其实大家对FOPLP都很有兴趣,只是在投入前会相对谨慎。”我们可以等等看随着汽车电子、新能源等市场的大热,FOPLP能否如Manz的预期般崛起,以及其走向究竟会是如何。