随着数据时代的到来,AI、大数据、云计算等技术不断发展,催生了更大容量固态驱动器和更快访问时间的需求,推动了3D NAND市场的竞争。

2023年初,三星制定了开发新一代3D NAND的计划:2024年推出的第九代3D NAND有望达到280层;第十代3D NAND有望跳过300层的区间,达到430层,预计将于2025-2026年推出。

图源:铠侠

近日,三星存储业务高管参加了电子工程师协会2023年夏季会议,表示2030年V-NAND可以叠加到1000多层。可以说,随着三星、美光、SK海力士等存储大厂纷纷将3D NAND层数提升至200层以上,层数之争亦有愈演愈烈之势。

3D NAND层数之争

2007年,随着2D NAND达到其规模极限,东芝率先提出了3D NAND结构概念。2013年三星则率先推出了其所谓的“V-NAND”,也就是3D NAND。

3D设计引入了多晶硅和二氧化硅的交替层,并将浮栅交换为电荷陷阱闪存 (CTF),区别在于FG将存储器存储在导电层中,而CTF将电荷“捕获”在电介质层中。这种3D设计方式不仅带来了技术性能的提升,而且还进一步控制了成本。

此后,三星不断更新技术和扩增产业线,10年间推出了数代产品,以维护自己在NAND闪存市场的地位。其中,2020年,三星推出了176层的第七代“V-NAND”,其采用了“双堆栈”技术,不是一次性蚀刻所有层,而是将它们分成两部分,然后一层一层堆叠。

据悉,三星第七代V-NAND相较于与第六代的100层,其单元体积减少了35%,可以在不增加高度的情况下将层数增加到176,同时还可以降低功耗,使效率提高16%。

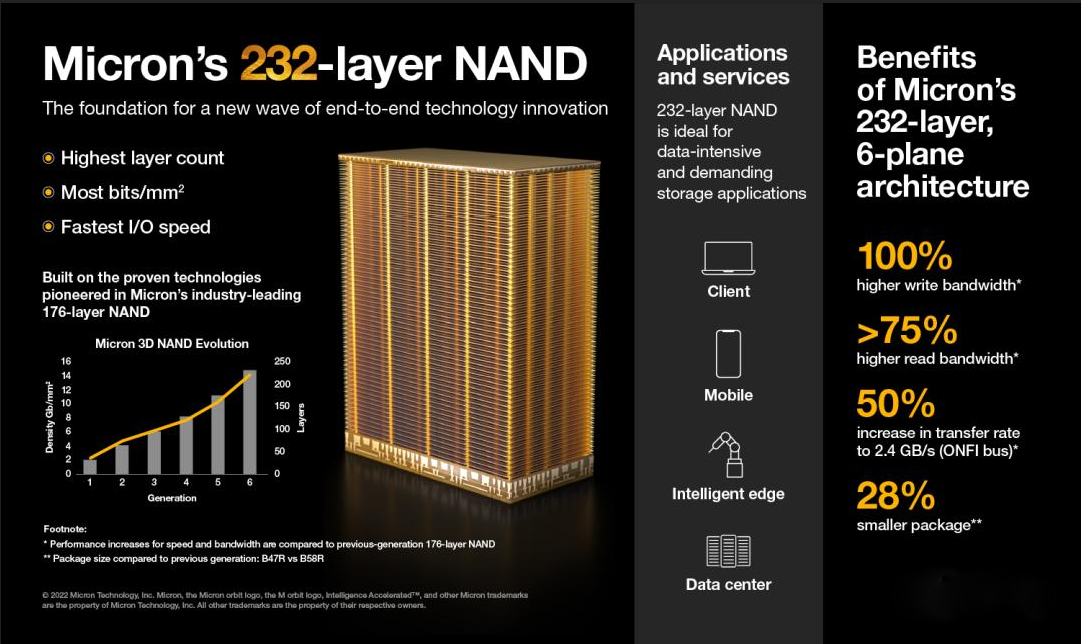

2022年7月,美光率先推出全球首款232层NAND。值得一提的是,美光发布的232层3D闪存芯片也采用了三星第七代一样采用“双堆栈”技术。即将232层分成两部分,每个部分116层,这些层的堆叠是从一个深而窄的孔开始,通过导体和绝缘体的交替层蚀刻。然后用材料填充孔并加工形成器件的比特存储部分。蚀刻和填充穿过所有这些层的孔的能力是该技术的关键限制。

图源:美光科技

今年5月,有消息称,铠侠和西部数据计划在2023年VLSI技术和电路研讨会上展示3D NAND技术创新,寻求实现8平面的3D NAND,以及超过300层的3D NAND。据提供的论文资料,为实现这一目标,两家公司计划采用金属诱导横向结晶(MILC)技术,即通过MILC技术,在超过300层的垂直存储孔中,形成14微米长的类通心粉硅通道。据报道,这种实验性3D NAND还利用尖端的吸镍方法消除硅材料中的杂质和缺陷,从而提高单元阵列性能。

而三星此次又提到了2030年将出现1000层闪存,势必引发储存大厂在3D NAND时代的技术竞赛。未来,NAND闪存堆栈层数也将犹如摩天大楼一样越来越高。对此,三星高管表示,正因为V-NAND的存在,延续了NAND的历史,是韩国国家创造技术和生态系统的少数成功事例。

3D NAND制造挑战

毫无疑问,尽管3D NAND未来发展方向是堆栈添加更多的层,但NAND层数的竞争将对制造工艺和投资带来更大的风险。

三星高管也表示,为了推动1000层的NAND技术,就像建设摩天大楼一样,需要考虑坍塌、弯曲、断裂等诸多稳定性问题,此外还需要克服连接孔加工工艺、最小化电池干扰、缩短层高以及扩大每层存储容量等挑战。

从理论上讲,堆叠1000层以上的NAND是可行的,但需要解决堆栈过程中的蚀刻问题,即必须蚀刻具有非常高纵横比的非常深的孔。尽管蚀刻技术在不断进步,但一次性蚀刻更深的孔具有很大的挑战,也无法提高蚀刻速度。而以沉积和蚀刻为主的工艺流程也堆栈如此多层数的话,将无法降低成本。

除了蚀刻之外,还需要用非常薄的介电层上下均匀地填充这个孔,而沉积几纳米的层并不容易,仍然具有挑战性。

另外,在堆栈如此多的层之后,还需经过蚀刻/沉积/清洁/热循环等工艺,比如在局部钻孔之后,整个堆栈中会切出一个非常深的沟槽,可能会导致局部和全局压力,相当于一个非常高的摩天大楼切成两座之后,可能出现倒塌的现象。

还有,将如此多的材料相互叠放并切割不同的图案,会产生全局应力并导致晶圆翘曲,将导致无法处理。

对此,三星的解决方案是创建极薄的层。不过,今年6月,TEL宣布,已开发出一种用于存储芯片的通孔蚀刻技术,可用于制造 400层以上堆叠的3D NAND闪存芯片。同时,TEL表示,该技术首次将电蚀刻应用带入到低温范围中,并创造性地发明了具有极高蚀刻速率的系统。这项新技术可以在短短33分钟内完成10微米深度的高纵横比蚀刻,与此前的技术相比耗时大幅缩短。

当然,蚀刻工艺在一定程度上得到优化和解决,但极高层数的3D NAND还有很多技术瓶颈有待突破。