有关Intel的IDM 2.0计划,过去一年我们也谈得挺多的了。大部分关注Intel的同学应该都知道,IDM 2.0的核心思路涵盖更积极地对外提供foundry服务、部分芯片的制造交给第三方foundry进行,以及坚持Intel的IDM模式不变。

去年3月份,我们也大致谈论过Intel的foundry业务能够给Intel带来的价值,包括旧工艺的资源转化和复用、原有制造资产的寿命更久、尽早实现较高的产能输出和工厂利用率等。

不过IDM 2.0大框架还是很抽象,比如说foundry尤其是先进工艺对外代工与否,除了更赚钱,还有什么价值;以及foundry一定程度的“独立”对Intel的芯片设计又有什么实际作用。前不久在面向投资者的webinar上,Intel更多地谈到了把foundry制造,与设计一定程度“解耦”的逻辑,在我们看来对理解Intel的未来发展很有价值。

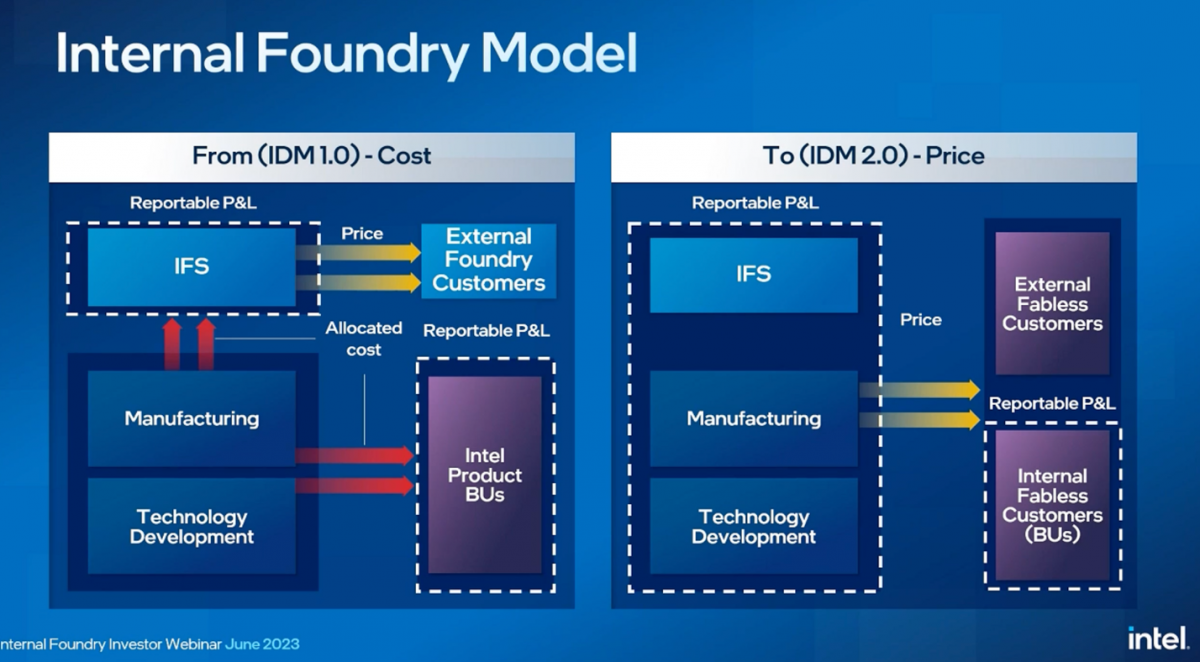

在这次的投资者webinar上,Intel表示包括Intel Foundry Services在内的制造业务,将单独汇报盈亏;也就是单独核算,并不是真正的“拆分”。Intel不是直接把设计业务和foundry业务简单地切分开。Intel方面表示,产品和制造业务的融合还是有很大价值,比如说内部团队合作,且内部团队作为新工艺的“0号客户”,能够为外部合作方降低工艺节点的潜在风险,也有利于快速提量,所以没有必要将业务单纯地一分为二。

那么这样的“解耦”或者叫“内部foundry模型”,真正产生的价值又有哪些呢?

从IDM 1.0到2.0

仿佛在HPC领域坚持IDM的主要市场参与者已经十分罕见了,连三星的LSI设计和foundry业务都剥离得很开。尤其HPC方向的IDM,会构成巨大的风险,毕竟尖端制造工艺无论是难度还是投入,都不是过去可比的。

不过IDM也有自身的一些优势,比如对于fabless + foundry的模型来看,fabless和foundry毕竟还是不同的公司,则数据共享等问题会存在限制;另外如Intel作为IDM,从直觉来看,芯片产品的最终价格有成本优化的空间,利润也能做得更高。

但是,Intel给出了一份预期数据,即假定现行foundry+fabless双方构成同一家企业,则相比于Intel,可达成的毛利率(gross margin)差异。前者到2022年会有>20%的领先,这跟我们的“直觉”判断是很不一样的。

从Intel的数据来看,在14nm以前,Intel还的确在毛利率上有优势,但后续剪刀叉形成,大约是在2017年,尖端制造工艺往10nm/7nm转向之际。Intel在制造工艺上落后于台积电这样的竞争对手以后,Intel的更多问题也暴露了出来,包括各种低效的资源配给方式。制造工艺的落后在此仿佛成为IDM模式优势变弱势的转折点。

SemiAnalysis在最近的分析文章中说,由于更低的工具利用率和更糟的良率,若要达成相同的产能输出,Intel是要用上更多的fab空间的。这就很大程度地表现出了低效。而且Intel的设计团队实际也某种程度上存在效率低下问题:相比于AMD处理器,达成相似的性能,需要更多的晶体管——而且在新架构量产前,还总是浪费更多的fab资源,和更高的设计成本。这些后文会提及。

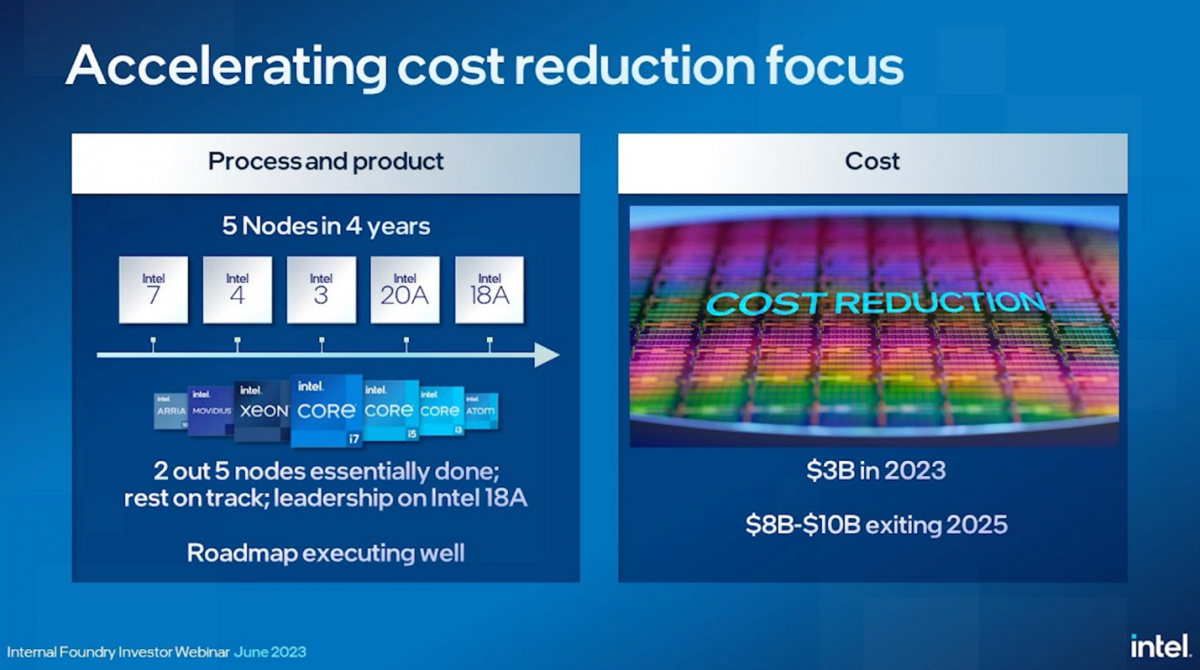

从表象上来看,首先需要解决的问题,当然就是尖端制造工艺技术得跟上。所以Intel提出了4年完成5个工艺节点的目标:就前不久PowerVia技术的阶段性汇报来看,我们认为Intel要按计划在2025年赶上台积电,应该是可以做到的。但光解决尖端制造工艺的技术问题,实际上是不够的——要不然也不需要提什么IDM 2.0。

这样的大环境下,包括尖端制造工艺的资本密集度显著提升,chiplet时代到来导致不少旧工艺价值的提升,以及Intel在尖端制造工艺上开始落后于竞争对手,于是Intel开始寻求IDM 2.0的改变——着力于解决IDM低效的问题。

从IDM 2.0的大框架来看,更积极地对外提供foundry服务本来就是提升资源利用率的方案,而芯片设计部分给到外部foundry厂亦如是。但这还不是全部。

IDM的一些低效轶事

似乎在我们的理想臆测里,IDM是设计、制造两个团队的和谐搭配,工艺还能根据设计来做适配,一切都应该挺美好的。但实际情况却经常不是这样。举个例子,关注Intel CPU各项参数的读者应该知道stepping步进这个概念。不过这里所说的步进是量产之前的stepping。

在芯片设计完成之后,将设计发给fab,设计转为光掩模(photomask),并通过一大堆的工艺步骤来造测试芯片......设计方拿到返回的测试芯片以后,还需要去检查、发现问题,并对设计再做调整。Stepping是指每次迭代:每次迭代后的版本设计发往fab,都需要对测试芯片重新构建光掩模。

据Intel CFO(首席财务官)David Zinsner所说,以前Intel的设计团队想做多少次迭代,就做多少次迭代。比如面向数据中心的Sapphaire Rapids芯片据说经过了12次stepping——相比较来看,AMD这边类似定位的Bergamo、Genoa就只需要2-3次stepping。那么像这样一个过程,就存在成本的大量增加,同时time-to-market也延迟了。这可能就是IDM的“任性”表现之一吧。

SemiAnalysis说他们听过一个传言,有一次Intel某设计团队还没先做好完整的仿真验证,就很任性地把设计发给fab,然后跑hot lot来测试bug——当然这只是个传言,真假未知,大约是为了体现原本IDM 1.0运营模式中的低效的。

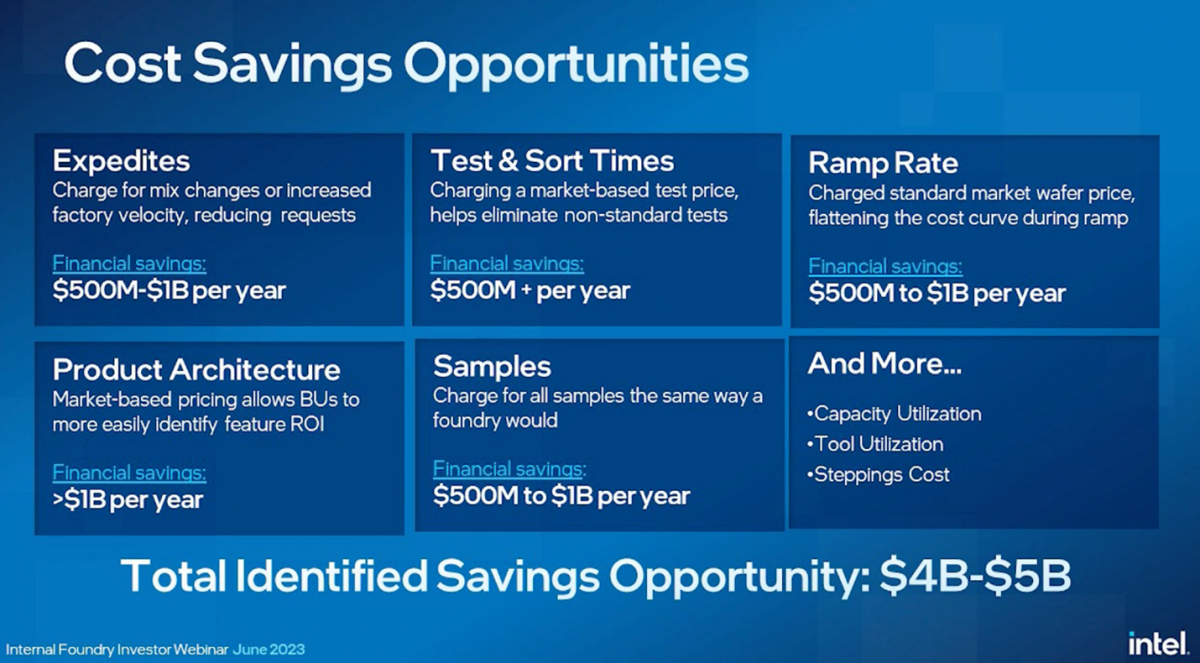

Intel期望减少出样和stepping的次数,方案是要给钱——设计和产品业务部门需要为这样的操作支出费用,这样就能节制他们的stepping行为。不过据说Intel的设计团队多年前就开始转向更加行业标准的设计技术方法了,虽然可能这个过程转变仍然需要时间。

Intel方面表示,这个改变每年能够节约5-10亿美金。

同类改变再比如hot lot相关的。一般同批次处理wafer就叫lot,这些wafer依次由某个生产工具处理过之后,再发往下一个工具。所谓的hot lot可以理解为“插队”的批次,就是给某批wafer以优先级,更快地做处理。

对于某些新工艺步骤或工具做验证,或者是以新的设计与技术做测试芯片,搞hot lot也很正常。但据说此前设计团队也是想怎么安排hot lot,就怎么安排,不考虑工具利用率和成本的问题。

很容易想见,随便跑hot lot就是会降低整体的生产利用率。那么很自然地,Intel现如今的方案是,芯片设计若要跑hot lot,需要和常规模式一样付钱,自然也就能更好地解决这个问题。Intel认为,这样的举措同样能够每年节约5-10亿美金。

还有个典型的成本节约环节体现在测试、sort、bin上。此前我们也撰文谈过所谓的“binning”流程。除了常规的可靠性、耐久性测试,还像“binning process”这样的测试需求,是基于芯片制造总有良率差异,对于CPU、GPU这种设计和制造难度、成本都比较高的芯片而言,即便最终造出来的某些芯片存在问题,如某个区块不可用或者电特性并不理想,也仍然可以通过测试分组、binning的方式,来划归成不同的产品SKU出售。

Intel在测试、sort、binning方面有着高度定制的工具和流程,原本在技术上可能是存在优势的。但这次Intel特别提到,相比于竞争对手,Intel的测试时间会显著更久,甚至会长2-3倍的时间。从最终成果来看,起码近代的Intel处理器,相比竞品在产品可靠性上也并未因此表现出多大的优势。

那么直接针对测试、sort、binning收费,也能让对应的业务团队在测试策略上有所收敛,每年再节约大约5亿美元。感觉这些举措也的确是对设计与制造某种程度的解耦,显著提高资源利用率。

甩锅更有难度

HPC领域做IDM模式还有个客观缺陷,就是产品的某些问题,很难去追溯到底是谁的“锅”,权责很难做到明晰,起码无法把问题追究到个别团队和业务单位。比如最典型的CPU的性能、效率、成本,如果数字不够理想,那么究竟是谁的问题,在业务结合紧密的情况下,就会很难真正搞清楚。

换句话说,比如原本是设计团队的锅,架构层面就低效,那么这个关键问题在原本IDM 1.0模式下,极有可能被全局隐藏。IDM 2.0模式是在同时有外部设计客户做比照,以及“内部foundry模式”和权责进一步分清以后,将最终的问题更清晰地摆到台面上的。起码设计团队要把锅甩给制造业务,难度就大很多了。

其实在这一例中,上述举措在节约成本的同时,也某种程度扭转了设计团队的任性作风:因为如果“甩锅”更难,且无法随意跑hot lot、任意stepping和测试,则必然要在架构、成本之类的问题上,在前期设计阶段就多下功夫。Intel认为,这能带来每年10亿美元的节约,因为设计团队会更谨慎地去审视某些特性是否值得花在die size上。

SemiAnalysis说此前Intel设计团队会无视各种限制,比如说制造吞吐量,还有reticle尺寸等问题。而这些在台积电这种专职foundry业务的制造厂这边是不会发生的,这对客户都属于常规。

最后值得一提的是作为foundry的良率和产能问题——这和过去尖端制造工艺都面向内部的情况就很不一样。据说台积电的7nm、5nm工艺都是在6个月的时间里就从0WPM达到50000WPM(晶圆/月)的。而Intel以前的历史看起来就没有这么顺利,Ice Lake和Sapphaire Rapids的起量速度就很慢。

这次Intel表示会在工艺节点的生命周期内,收取内部的"flat wafer price",以期加速新产品的产能爬坡速度。虽然我们不知道具体在财务上,这笔账是怎么算的,不过Intel也表示这么做既能每年节约10亿美元,而且能提升产品上市的速度。

还有就是作为面向内部的foundry服务,也需要收取产能占用、锁订单的费用——Intel表示在此之前设计团队想改forecast都是随时随地的...这么看来,设计与制造的部分解耦,略有点儿内部市场化的意思。制造业务不会再像过去那样各种迁就设计团队了。这么做自然也增加了制造业务的工具利用率,因为面向内部和外部都能做更好的生产规划了。

基于我们对Intel产品路线图的观察,先进制造工艺、先进封装技术悉数抛出,CPU之外的产品也开始全面布局,前沿技术研究也在持续,势头还是相当好的。只不过我们预计今明两年对Intel而言,仍然会是难熬的两年。

先进制造工艺的追赶,以及以酷睿Ultra CPU为代表的处理器,开始全面采用chiplet与先进封装技术,技术布局水平也全面优于AMD这样的竞争对手,固然对长期发展非常有益;但我们认为这些很难在短期内造成昔日绝对优势的局面,则在强敌环饲的现在,也就做不到轻易破局。

不过规划和方向都已全面到位,不再是2年前阴霾密布的窘境。IDM 2.0在我们看来,的确是Intel中长期内“重回王座”的关键。Meteor Lake、Sapphaire Rapids破不了局没关系,因为这些产品都是为下一代技术打头阵做准备的。