过去数十年里,英特尔一直是硅晶体管技术(用于经典计算机)主要先驱之一,最近几年又开始战略性布局量子计算了。近日,基于数十年的技术积累,英特尔发布了12硅自旋量子比特的量子芯片Tunnel Falls,其为英特尔迄今为止研发的最先进的硅自旋量子比特芯片。

当前,很多企业和研究机构都加快了量子计算方面的研究,但英特尔在量子计算竞争中最大的优势应该是利用硅晶体管构建高性能计算模块方面的能力。最近几年,英特尔也在研发自己的量子芯片,而且走的是硅自旋量子技术路线,且使用传统的CMOS半导体工艺就能生产。

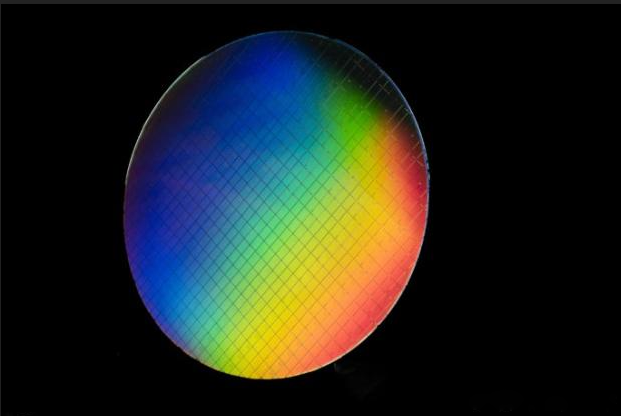

(图片来源:英特尔)

据悉,Tunnel Falls芯片是在英特尔300毫米晶圆产线上制造的,利用了英特尔领先的晶体管工业化制造能力,如极紫外光刻技术(EUV),以及栅极和接触层加工技术,具有95% 的晶圆良率,每块晶圆实现超过2.4万个量子点,用于量子技术研究。该芯片的推出也意味着硅自旋量子比特芯片在商业化量产上又近了一大步。

量子计算是一种遵循量子力学规律来调控量子信息单元进行计算的新模式。相对于经典计算机的比特位(bits)来说,量子比特的处理速度更快,更适合于高速数据搜索,也将进一步完善网络安全,其被人们寄予厚望。

量子计算机之所以具有极大应用潜力,主要在于和传统计算机的二进制相比,其比特都有 0 和 1 的状态;但是量子计算机还存在一个 0 和 1 之间的任意线性组合,属于一种像 “薛定谔的猫” 一样的叠加状态。如果将多个量子比特放在一起,这些叠加状态之间又互有关联,就能存储和计算更多的数据。

简言之,多个量子比特在某一次操作之后不是仅代表多个比特 “0” 和“1”的一种组合,而是可以代表所有可能的态。这样在运算的时候,采用量子比特则是把所有态一起计算,可大大加快运算速度。而如果还能进一步让量子比特超越 “面对面” 的距离进行联系,则可能更大程度增加量子计算机的潜力。

目前,很多科技巨头以及研究机构的量子计算机原型的量子比特,都是由超导电路技术制造的,但硅自旋量子比特的大小与一个晶体管相似,约为50x50纳米,比其它类型的量子比特小100万倍,并有望更快实现量产。

英特尔认为,硅自旋量子比特比其他量子比特技术更有优势,因其可以利用先进晶体管类似的生产技术。而在硅自旋量子比特中,信息(0/1)被编码在单个电子的自旋(上/下)中。很多技术专家也认为:从长远来看,基于硅的量子比特更有前途。

在2022年3月的美国物理学会会议上,英特尔透露了公司的量子战略计划并指出,相比超导量子比特,自旋量子比特有着显著优势,例如每个量子比特的裸片面积缩小了几个数量级。这也在英特尔此前的研究成果中得到了验证:实现了在单个300mm的硅晶圆上集成了超过10,000个硅基自旋量子比特阵列。

据此前介绍,英特尔采用的是先进的标准EUV(极紫外)光学光刻、等离子蚀刻、CMP(化学机械抛光)以及大规模193nm光刻工艺构建硅基自旋量子比特芯片。经过在制造设施中不断优化晶体管制造工艺和步骤的多年经验,英特尔的先进制造方法已具备了高产量、高精度、低污染、高匀度、高再生性优势。

英特尔全栈式量子计算系统规划图(图片来源:英特尔)

据悉,在硬件开发之外,英特尔还在软件方面作了相关的规划,即在量子计算的布局上,其在努力实现全栈式路线,包括自研软件开发工具包(SDK)、带有基于LLVM架构的C++编译器和系统软件工作流程,旨在高效执行经典/量子变分算法。

下一步,英特尔将持续提升Tunnel Falls芯片的性能以及量产可能性,同时与量子软件开发工具包(SDK)整合在一起,集成到英特尔的量子计算堆栈中。而基于Tunnel Falls的下一代量子芯片,预计英特尔将于2024年发布。