自从第一只晶体管发明以来,在半导体世界著名的“摩尔定律”指导下,集成电路(IC)设计的复杂性已经提高了10亿倍。这种不断扩张的一个重要因素,就是数字设计流程的不断发展。

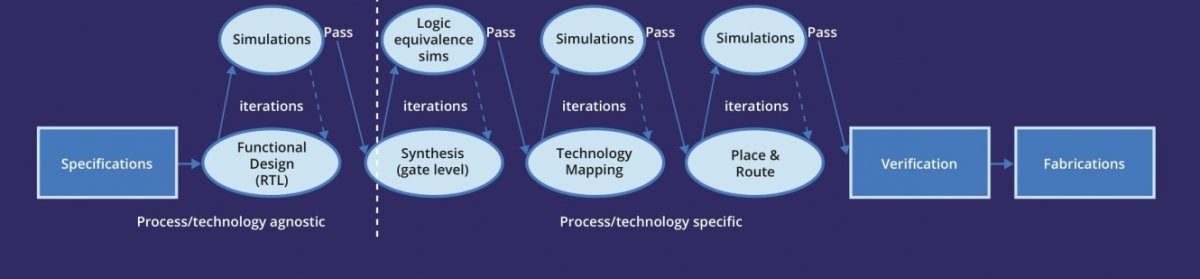

现代的数字设计由多个步骤组成,下面是一个简化的流程。

图1:包含多个步骤的数字设计流程。来源:Agile Analog

数字设计最初是以一种与工艺无关的方式进行的,主要指导因素是可能的逻辑深度及其对可实现性能的影响。因此在不同的工艺节点之间,有很好的设计可移植性,且不会影响验证质量。随着设计捕获抽象水平的提高,用于在流程各个阶段检查一致性及符合性的全面设计工具流程和验证方法得以改进,使设计师的生产力有了极大的提高。

伴随着验证和签字确认工具的改进,数字设计过程也越来越自动化,可以直接产生复杂的、高质量的、一次即正确的IC,不用依赖硅片确认来验证。

尽管数字设计是独立于工艺的,但从综合到布局布线的整个设计实现,都要充分考虑目标工艺节点,并贯穿于各种模型和签字确认过程。事实上,同样的设计,可以用非常不同的方式实现,并且可以专门针对特定的工艺特征进行优化。

与工艺无关的数字设计,允许在公司内部进行跨项目和跨产品代的完整IP复用。这是数字IP商业模式多年来不断发展和繁荣的一个关键原因。虽然数字设计与工艺无关,但其实现工艺流程却与特定工艺有关,从而允许公司在复用数字设计的同时,能够紧跟最新一代的半导体制造工艺。

在过去的三十年里,数字设计流程已经得到了验证、改进和优化,因此即使是采用最先进技术节点的设计,也有望第一轮就获得成功。

模拟设计流程

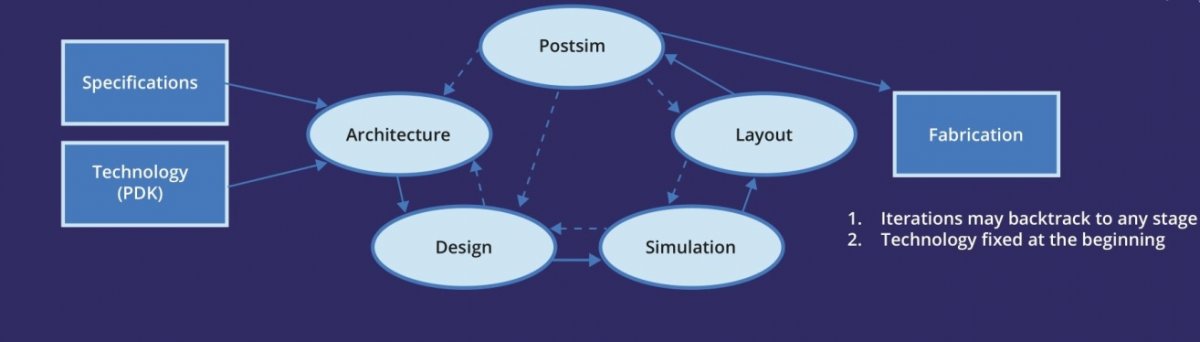

然而,模拟设计的流程则有很大的不同。

图2:模拟设计流程是由几个周期组成的循环迭代,与“线性化”数字设计流程有很大的区别。来源:Agile Analog

虽然模拟设计流程和数字设计流程之间存在可比性,比如,模拟流程中的“架构”与数字流程中的“功能设计”相类似,而模拟流程中的“布局”"则与数字流程中的“布局和布线”相类似,但两者之间还是有着明显的区别。

首先,模拟设计流程是由多个周期组成的循环迭代,这一点就有别于“线性”数字设计流程。根据模拟电路模块的复杂性、电路设计师的经验、技术节点的专业性以及许多其他因素,设计流程会在模拟设计流程的某些循环中反复迭代,比如在布局和后仿真步骤之间,通常就要反复多次。

有些时候,会出现所选择的架构在物理层面无法满足电路指标要求的情况,这时就只能从第一步重新开始。简单地说,完成一个模拟电路所需的时间和精力都只能是大概估计,其不确定性还会随着设计复杂性的增加以及所用技术的变化而增加。

其次,模拟IP的技术或工艺节点是在设计之初就决定了的。用于架构研究和设计的可用器件、用于仿真的模型板、布局规则和金属R-C模型等都是与特定工艺有关的。如果项目决定改变工艺节点,甚至修改可用的工艺选项,那么整个模拟设计往往必须从头开始。

最后,对于模拟设计过程的每个步骤,都很少用CAD自动化设计。虽然针对每个设计步骤都有优异的EDA工具,但不同的模拟电路模块都有不同的设计方法,其仿真与电路、工艺和应用都有关,布局则是完全自定义的。

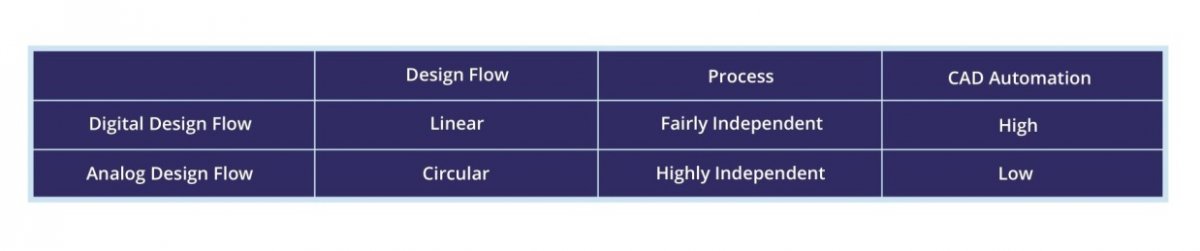

表1总结了模拟和数字设计方法的主要区别,这些区别正是模拟设计需要花费更多时间、不容易进行工艺升级、与数字设计相比还具有排他性的原因。

表1:模拟和数字设计方法的主要区别。来源:Agile Analog

模拟IP的创建

怎样才能造就一个好的模拟IP?更具体地说,创建一个好的模拟IP需要什么条件?

首先,需要选择一个好的电路架构,它必须是稳定的、健壮的、适合大规模生产的。

晶圆代工厂的最新工艺开发套件(PDK),可以为仿真提供前端(晶体管、变容管和二极管)和后端(电阻、电容和金属)模型,其中为设计规则检查(DRC)、基于原理图的布局(LVS)以及寄生参数提取提供了各种命令文件。现在许多大型代工厂的PDK,在模型和物理硅片之间都有非常好的相关性。用户要做的所有事情,就是完成正确的PDK安装和选择合适的工艺选项。

在要求的工艺、电压和温度(PVT)条件下,进行彻底的行为仿真和详细的电路仿真,可确保电路按照预期运行。电路版图工程师需要了解电路设计知识,了解工艺对模拟性能的影响,并对每条走线的细节加以高度关注。

上述工作需要一个由经验丰富的、具有多领域知识的电路设计师和版图工程师组成的资深团队。例如,一个模拟电路设计师,需要对布局规则和布放指南、以及工艺对电路性能的主要影响有一定的了解。同样地,版图工程师需要能够明确理解对每条走线的关键要求,无论这条走线是用于电源、一般信号还是敏感信号。

有了良好的电路架构、精确的PDK、全面的仿真、详细的布局,并由经验丰富的团队来执行模拟设计流程,通过设计流程的迭代轮次就会最少,所交付模拟IP的高质量就有了保障。

经过硅验证的IP

优秀的模拟设计团队十分稀缺,很难见到,故高质量的模拟IP也很罕见。这常常导致IC设计公司质疑某个模拟IP是否经过“硅验证”,或者要求模拟IP必须经过“硅验证”才有资格使用。那么,直击我们灵魂的问题就来了:“什么是硅验证?”,“经过硅验证就一定是IP质量的最好证明吗?”

“经过硅验证的”IP的一般定义,是指在硅片上实际制造的、并对其功能进行了基准测试的IP,因此成为经过了“硅片”实际验证的IP。一旦某个IP经过了硅验证,它就获得了可信度,人们就相信这个IP能在生产的芯片上按照预期工作,并且在相同的工艺技术条件下,具有相同的布局。然而,这样的硅验证只是对设计的单点(或几个点)确认,通常基于预先定义的参数,并在特定的电压和温度点进行了测量;换句话说,仅仅是IP功能的一个“样本”而已。

这个“经过硅验证的”IP是否具有“生产质量”,是在该IP的制造使用之前就已经决定了的。需考虑的因素包括:所选择的架构、仿真的全面性和所覆盖的设计偏僻案例、在布局方面所付出的努力、以及在开发过程中的验证等等。换句话说,一个经过“硅验证”的IP,仅仅是一种理智的检查,只能证明IP开发流程“看起来”是“没问题的”。这似乎并不是质量的充分证明。

一些“经过硅验证的”IP,是从生产芯片中提取的IP,或由其他被授权者在成功生产中使用的IP,它们经受住了现实世界中各种条件下的大批量测试。这些IP的质量当然是可信的。然而,这些IP是专门为采用特定工艺节点的特定产品设计的。针对采用不同工艺节点的项目,需要进行工艺移植,则其“硅验证”状态将会失效。即使在新项目采用与硅验证IP完全相同节点的情况下,该IP也可能在性能或面积方面无法满足要求。

举例来说,PMOS驱动器件占整个LDO面积的50%以上;因此,一个“经过硅验证的”LDO,对某个需求而言往往是过度设计的,占用的硅片面积比必要的要多。其尺寸也是固定的,所以其他元件需要配合这个IP的尺寸。虽然也可以对这些经过硅验证的IP进行修改,但对于每个实例而言,往往都需付出很高的额外资金成本(动辄几十甚至数百万美金)和时间成本(长达1年),有时候这些成本甚至高得令人难以承受。况且修改本身也会导致原始IP的“硅验证”状态失效。

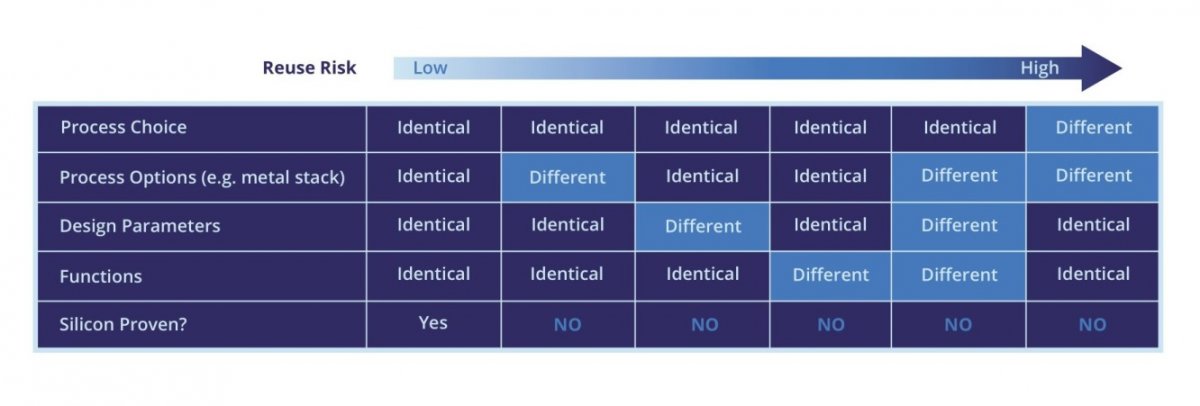

工艺选择、工艺选项、具体设计参数和功能,都是决定IP “硅验证” 的有效性因素。从表2可以明显看出来,“硅验证”在IP复用中是非常少见的。

表2:这些数据表明,“硅验证”在IP复用中是很少见的。来源:Agile Analog

总之,“经过硅验证的”IP,是与某些具有明确性能的工艺相联系的,只是在设计参数的某些特定点上得到了验证。它们可能不符合人们的具体需求,而对IP的修改很可能会使其“硅验证”状态失效。模拟IP的质量仍然基于前面所提到的标准,即:良好的架构、精确的PDK、全面的仿真、有经验的设计团队,以及将所有这些质量点联系起来的严格设计流程。

(参考原文:Analog IP: Why silicon-proven is not what you think)

本文为《电子工程专辑》2023年7月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅