一直以来,NAND这种存储技术的成功与其不断扩展密度和成本的能力有关,也是其技术发展的主要驱动力。但毫无疑问,NAND闪存向三维的发展应该是最具有代表和方向性的创新。

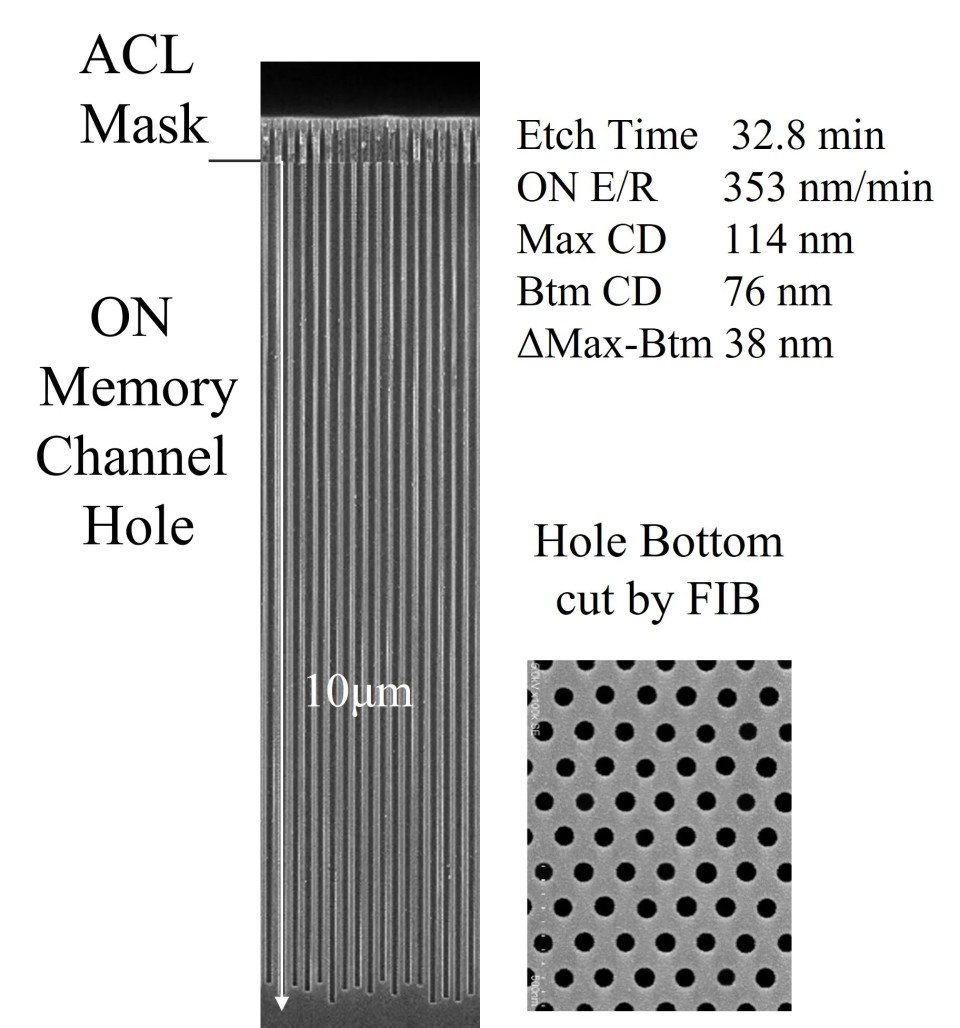

近日,半导体设备巨头厂商TEL宣布,其成功开发出一种存储芯片通孔蚀刻技术。这项创新技术可以在短短33分钟内完成10微米深度的蚀刻,与此前的技术相比时间大大缩短。据悉,研究团队开发的新工艺,首次将电蚀刻应用带入低温范围,并开创性地发明了具有极高蚀刻速率的系统。

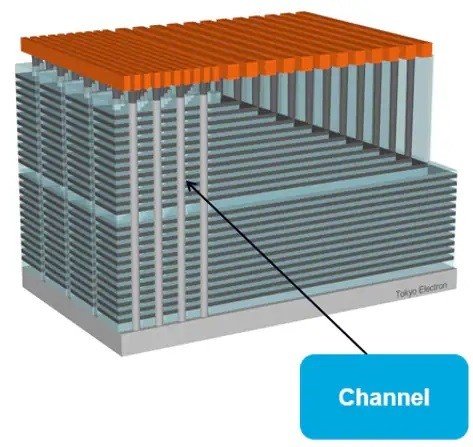

3D NAND闪存是一种把内存颗粒堆叠在一起解决2D或平面NAND闪存限制的技术。这种技术垂直堆叠了多层数据存储单元,具备卓越的精度,可支持在更小的空间内,容纳更高的存储容量,从而有效节约成本、降低能耗,以及大幅度地提升性能。

当前,晶体管尺寸微缩遇到物理极限挑战,逐渐面临技术瓶颈,达到发展极限。为了在维持性能的情况下实现容量提升,3D NAND成为发展主流。而TEL称,该技术的应用有助于制造更高容量的3D NAND,可用于制造400层以上堆叠的3D NAND闪存芯片!

图1:蚀刻通孔的横截面、纵截面 图源:TEL

图2:通孔用于3D NAND的示例 图源:TEL

整体来看,3D NAND未来的发展主要聚焦两个方向:一是增加层数;二是提升密度。因此,在增加NAND层数的同时,业界也需提升密度。铠侠技术执行官柳茂知也曾指出,“存储密度是王道,因为密度就是成本。但3D NAND的层数并不等于密度。如果层度比较厚,那么整体密度也不会高。如果存储器孔间距较长,则横向密度不高。”

TEL此次推出用于制造400层以上堆叠的3D NAND的技术,将推动业界继续加大3D NAND技术节点的升级,即堆叠层数的增加,推升激发刻蚀设备需求的增长。在存储应用中,刻蚀设备和薄膜沉积设备已成为最核心设备。而TEL正是相关类别设备的重要供应商,预计将受益于3D NAND的技术的迭代升级。

值得一提的是,最近SK海力士也宣布,已开始量产238层4D NAND闪存,并正在与生产智能手机的海外客户公司进行产品验证。由此可见,当前NAND技术的竞争越来越激烈,在400层以上堆叠的3D NAND的技术出现之后,预计这种增加层数的趋势将在未来几年继续下去。