有个挺有趣的现象,当我们在说摩尔定律停滞的时候,常规辩驳思路总是谈封装层面的3D堆叠;或者器件层面的3D折叠(CFET)。“3D”这个词对应的当然应该是“2D”,换句话说是从平面结构转向了立体结构。因为东西一旦折起来,不就省了空间、延续了摩尔定律吗?不过在3D发展同期,我们还在频繁地提2D——2D材料。这是什么?

前不久Intel的技术展望,和去年年中未来晶体管的介绍中,我们都提到过2D材料。2D材料事实上也的确是IEDM这种顶会近些年的大热门——基本可以确定的是,2D材料有较大概率成为未来芯片尖端制造工艺的标配,成为某种形态的计算设备被普罗大众所使用。

而且实际情况是,2D材料可能并没有我们想象得那么遥不可及,多少也有点眉目了——不止是去年Intel在IEDM上展示的,将2D材料用到了GAAFET晶体管上;还在于某些旧工艺的BEOL已经在尝试2D材料了,主要是MEMS、射频、光电transceiver之类。毕竟这些器件可能不像晶体管那样有着那么严苛的质量需求。

据说2D材料能够极大提升这些应用的性能。德克萨斯大学奥斯汀分校已经搞出了2D材料的RF开关器件原型;硅光方向上,transceiver的各种元器件在2D材料的加持下,可以实现单片化 - 像modulator这种器件还能大幅降低驱动电压,诺基亚、爱立信之类的企业都在朝这样的方法努力...

那2D材料究竟是个啥?对晶体管而言意味着什么?恰逢上个月,SemiAnalysis两名作者联合创作了《晶体管的未来》一文,这篇文章的核心就是在探讨2D材料,我感觉其中有存在相当价值的部分可做分享;而且因为过去大半年的工作比较忙,都在研究最为商业的产品和方向,对于技术的关注少了很多。借此机会,本文尝试谈谈2D材料相关的这种晶体管未来。

既然谈到晶体管,其最终构成的还是芯片。芯片设计与制造,是将晶体管、器件、互联构成大规模集成电路的过程。3月29-30日,AspenCore将在上海举办2023国际集成电路展览会暨研讨会(IIC Shanghai),同期举办的EDA/IP与IC设计论坛邀请到多家国内外优秀的IP供应商与IC设计企业发表演讲,欢迎点击报名参会。

与此同时,言及2D材料要率先应用于射频器件,那么与IIC Shanghai同期举办的射频与无线通信技术论坛自然也不应该错过。该论坛将邀请国内外领先的射频芯片、通信技术企业以及终端应用企业作相关主题分享,为产业链提供深度交流与合作的平台。

现在很热门的2D材料

近代晶体管发展的几个重要节点,不管是材料方面的,还是结构方面的大变动,无非就是因为晶体管在缩小的过程里,总是面临着形形色色的问题——说到底,工程上的种种变化,都是为了提升晶体管的性能和效率,包括降低漏电流、提升开关速度之类。

比如说Planar平面晶体管时代,尝试拉伸(strain)晶体管的沟道(channel),硅是铺在一层SiGe(锗化硅)上面的。由于上层硅的原子要和SiGe层对齐,硅层的原子之间的联结就会被拉伸。换句话说,硅原子分得更开,与电子移动产生干扰的原子力就会减少,那么电子迁移率能够大幅提升,晶体管的开关速度就变快了。

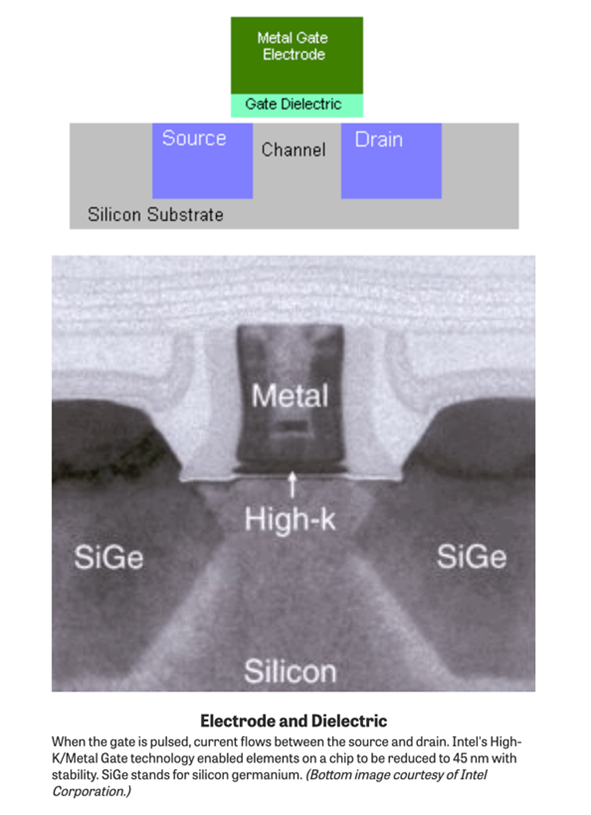

再比如说45nm时期引入的high-k高介电常数gate(栅极)——Intel每次回顾技术革新过往都会提到high-k。随着器件的微缩,gate dielectric(栅极介电层/绝缘层)的绝缘性也在变差,导致漏电流。传统的gate dielectric用的是一层二氧化硅——这一层就位于metal gate(金属栅)电极和沟道之间。而Intel的high-k技术,则是指把这一层换成基于铪的介电层。加上其他gate电极金属材料,也就有了high-k高介电常数的gate。

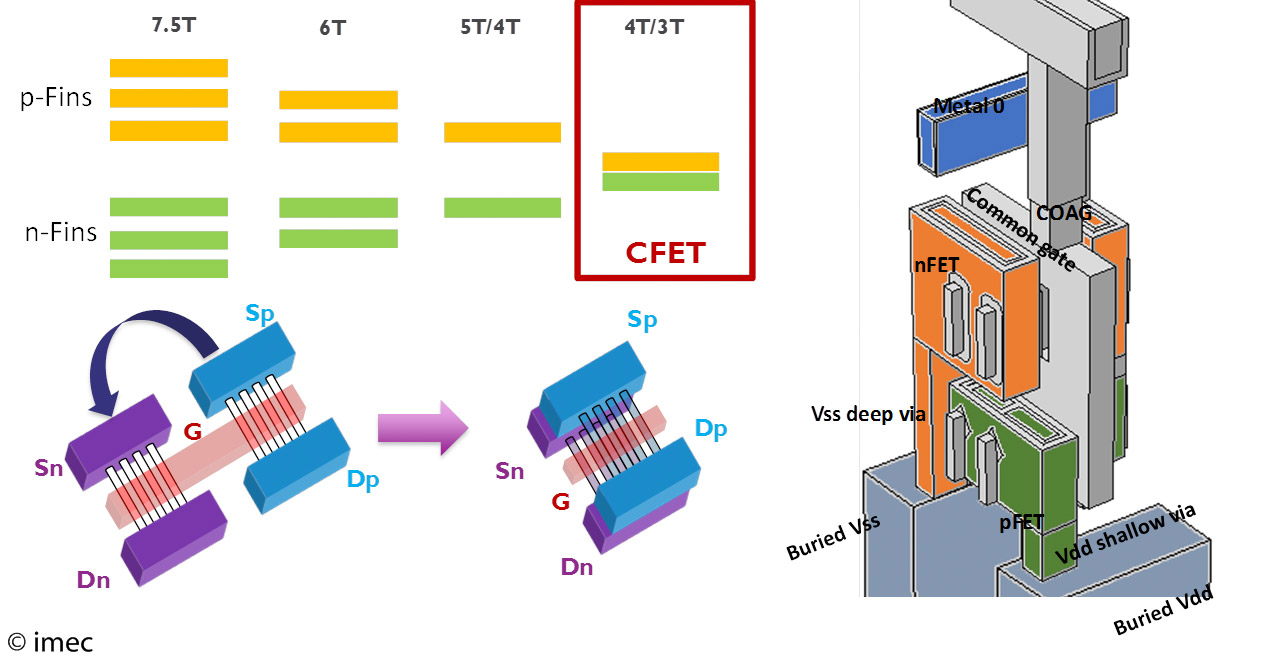

在器件结构方面,20nm时期的FinFET结构转变,以及到3nm/2nm时期器件结构即将转向GAAFET,都是众所周知的了。器件结构变化的本质也是类似的,就是随着器件尺寸的持续微缩,对于电流的控制难度在持续增大,所以必须在结构上做出一些革新。更未来向的一些结构变化,过去的文章里也介绍过。

在2nm之后,还是需要新材料寻求新突破的,因为随器件的持续微缩,像硅、锗这些材料中的电迁移率还会大幅下降。而接下来的解决方案可能就是2D材料。

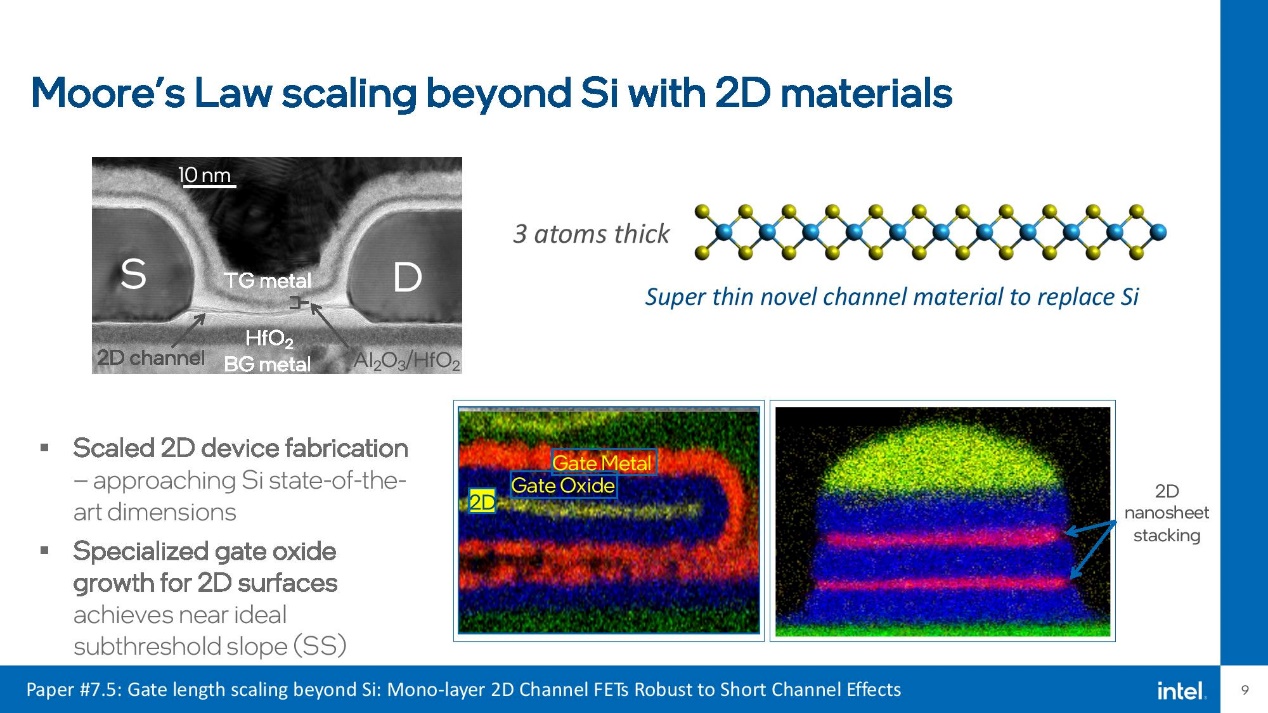

去年的IEDM大会上,Intel在演讲中谈到了几种未来向的技术,包括一种名为QMC的先进封装工艺,一种3D堆叠的FeRAM,还有就是2D材料。Intel展示的是把2D材料用到GAA结构晶体管的沟道上,实现低漏电和更加理想的开关表现,据说是往未来晶体管垂直堆叠迈出了很大的一步。

2D材料为什么会是未来?

“2D材料”这个名称中所谓的“2D”,应该是和3D晶体相对的;2D也就是薄到原子级厚度的一层。2D材料里面最知名的应该就是石墨烯了。石墨烯是一种以六角形格栅排列的单层原子物质。不过石墨烯是没有带隙(bandgap)的。

一般我们总在聊到第三代半导体的时候,会说“宽禁带”——这里的禁带差不多就可以理解为带隙。带隙指的是,激发一颗电子,从无法导电的价带(valance band),到能够导电的导带(conduction band)所需的能量。对于晶体管而言,有on开和off关两种状态,那么就需要明确的带隙来做区分。“宽禁带”可以理解为带隙很宽...所以石墨烯无法用作半导体材料——当然石墨烯掺杂后也有带隙,但仍然不够。

对于晶体管来说,现在聊得更多具有未来向的2D材料是TMD(transition-metal-dichalcogenide,二维过渡金属硫化物),具体的比如说MoS2(二硫化钼)、WS2(二硫化钨)、WSe2(二硒化钨)。TMD家族材料在<5nm的沟道厚度下,有着比较理想的带隙,电子迁移率也不错。

而且相比于传说中1D碳纳米管(carbon nanotube,CNT)这种现在看来仍然遥遥无期、面临巨大技术挑战的材料,2D材料会更加的近未来:至少就目前来看,制造上2D材料会相对更容易。

Intel对外宣传演示中的2D材料(MoS2)仅有3个原子的厚度,应用在GAAFET晶体管的沟道上,用于替代硅。IMEC的路线图上,传说中的3D折叠晶体管CFET结构,也有类似的解决方案,其中nFET和pFET的沟道都基于单层TMD。

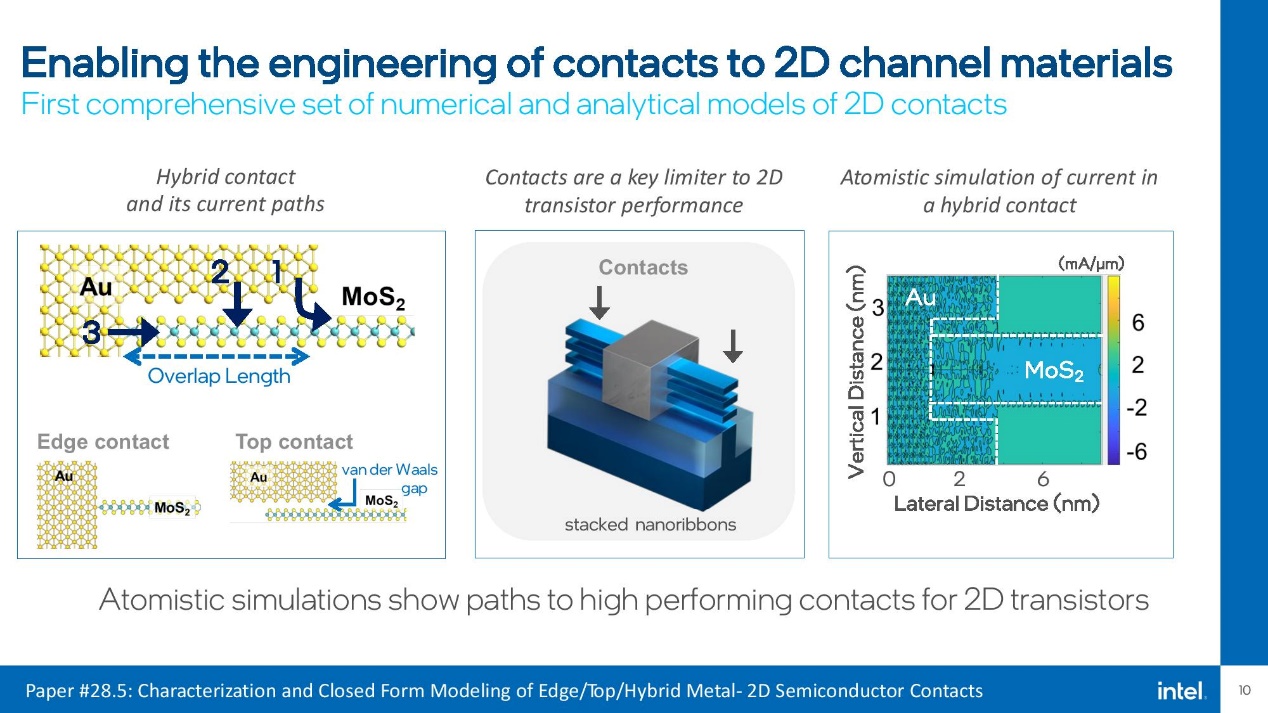

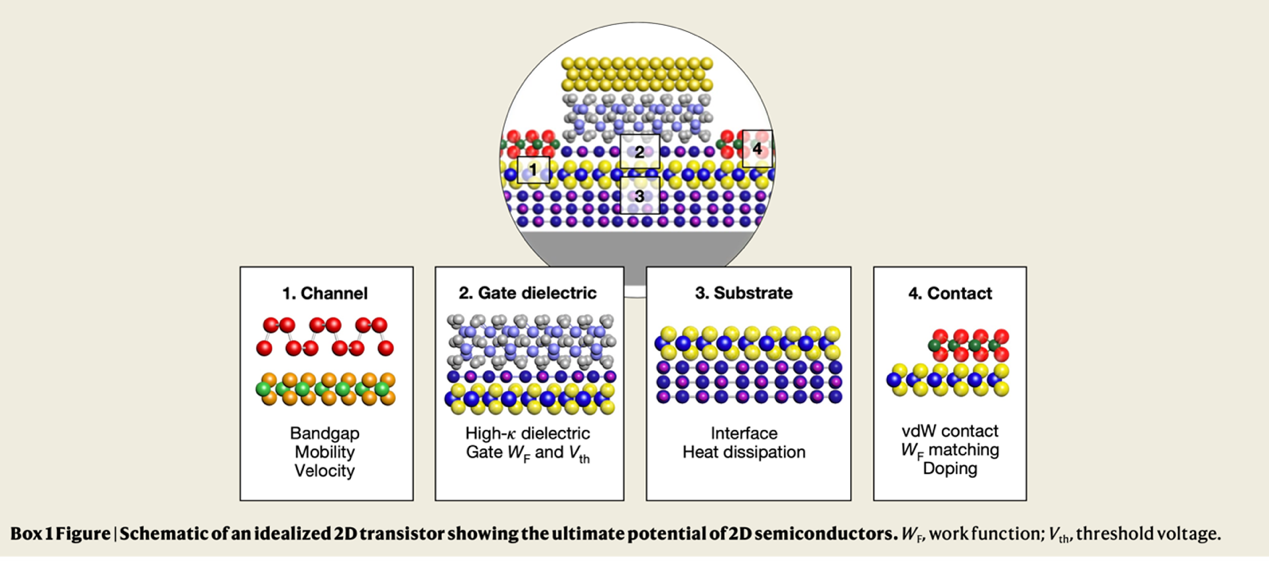

不过似乎相关“2D晶体管”不同“部位”的探讨,实则涵盖了沟道(channel)、前文提到的gate dielectric interface,substrate(基质)和contact,是更为全面的“2D”化。究其根本都在于提升器件性能。

对CFET有了解的同学应该知道,这种相对还略有点遥远的结构,是把pFET和nFET垂直叠起来——相比于很多人所知的3D封装,实则是在更低一级的器件层面就做3D堆叠。去年的IEDM上,北京大学的研究就展示了基于WSe2/MoS2的CFET,相比于传统的普通平面结构方案在性能上实现了8%的增长,以及44%的面积缩减。2D材料在这其中当然也是扮演着重要角色的。

好像在名称上就叫“2D CFET结构”——2D和3D在未来的某个时刻也就达成了和谐统一,既是堆叠、又是2D。

CFET达成器件层面的堆叠,在研发方面的一大挑战就在于源极和漏极的contanct(触点)上,包括选择互联的contact材料。台积电在一篇paper里提到了2D材料是理想选择。在材料挑选上,相关MoSe2(二硒化钼)沟道的,还在于达成理想逸出功(work function)和费米等级钉扎效应(pinning effects)的contact材料,似乎包含有锑和铂。

据说如此就能达成最低的接触电阻,pFET 0.75kΩ-μm, nFET 1.8 kΩ-μm。其中nFET实现了接触电阻72%的缩减,在2D沟道方面可能也是迈出了一大步的。另外,除了器件的接触电阻,为了降低阻隔电阻(spacer resistance),台积电的方案是,用钨氧化物(WOx)(对多层WSe2进行氧化),配合WSe2沟道作为低电阻的spacer掺杂,达成了总体更低的电阻。

SemiAnalysis另外在文章里谈到了2D材料用于dielectric interface,用hBN(氮化硼)作为封装层的MoS2方案,很大程度增加了器件的可靠性和寿命(可靠性主要体现在封装层,包括关断状态更稳定,以及介电层在后续处理过程中损耗更小),同时总体达成了最低的亚阈值摆幅(mV/dec, 这个值是衡量晶体管开启与关断状态之间相互转换速率的性能指标,mV/dec代表漏源电流变化十倍所需gate电压的变化量,越小就意味着开启关断速率越快)。这应该是普渡大学(Purdue University)去年发表的一项研究。

但巨大的挑战仍在眼前

既然2D材料这么好,怎么还不全面普及?当然就是走出实验室的这一步还缺点儿东西。2D材料一般通过CVD(化学气相沉积)生长获得。另外更近期的研究也可以用ALD(原子层沉积)方法。根据substrate和相关变量的控制,2D材料生长可以做成单层的或者多层的。

比如最为成熟的单层石墨烯,是在铜箔或者薄膜substrate上通过CVD方法生长的。不过生长存在的变数比较多,wafer-to-wafer的一致性很难达成。现有的技术会导致一些生产缺陷,比如说晶粒边界(grain boundries,一种面缺陷,是指晶体结构中周期性的排列规律被打破)。存在晶体缺陷的CVD石墨烯电子迁移率会产生巨大下降。晶圆或者材料的变量如果非常大,量测/检测也会变得很困难。这也是石墨烯市场始终不大的原因。

像MoS2、WS2之类的TMD材料发展阶段较之更为早期。AixTron(爱思强)和Oxford Instruments(牛津仪器)是目前仅有的,出售2D材料生长工具的OEM厂商。

除了生长之外,另一个技术难点是2D材料的转移(transfer)。 因为2D材料生长一般是在>600℃的高温下,在铜或者蓝宝石之类的substrate上完成的,那么后续就需要将生长出来的2D材料转移到最终的wafer上。据说现有CMOS制造工艺下,2D材料转移到硅器件wafer上的方法还相当低效。

常规的2D材料转移技术,包括对铜substrate进行湿法蚀刻(wet etching),然后用PMMA(聚甲基丙烯酸甲酯)把2D材料转移到目标substrate上。但在此过程中,PMMA会有残留在石墨烯表面,对材料的电属性也会产生影响。目前的2D材料转移方法,对于某些类型的应用(比如传感器/显示)是可行的,但就质量、吞吐率等方面来看,是无法满足CMOS生产需求的。

还有一种思路自然就是2D材料直接在硅上生长,问题就在于如何获得低温、高质量的生长解决方案。前文提到的ALD方法是可以用更低的温度来实现的,但吞吐是个大问题。另外据说像MOCVD(金属有机化学气相沉积)之类的方法,存在的各种缺陷也都是问题,主要是有机污染物、硫空位(sulfur vacancies)等。

所以高质量的生长流程,和高吞吐的转移流程可能还是应该分开、解耦——这在变量控制、工艺优化等方面也是常规思路。如此一来,生长和转移就可以异步进行,达成更大的产能。所以SemiAnalysis的专家整体还是更倾向于采用转移的方案,而不是在原有硅基上做生长,因为这在异构、堆叠、可配置性等方面都有优势。

从更具体的角度来看,前面举了一些实验室研究成果的例子。比如说北京大学基于WSe2/MoS2的CFET,面临的挑战主要都在实际制造方面。这项研究呈现的成果基本都是在现有fab框架下的生产制造,除了nFET的MoS2沟道是用湿法转移技术——前文已经提到了。可能干法转移在最终实现生产方面会非常重要。我们没有仔细去研读paper本身,或许前文提到的方案也有生产制造方面的考量。

Intel那边的2D FET是基于MoS2的转移,源极到漏极contact的长度25nm,和现在的硅工艺节点类似。测试得到的结果显示,器件的亚域值摆幅还比较理想。但Intel用的是ALD生长的dielectric牺牲层,然后去做转移,这会产生大量残留,源极和漏极contact都有MoS2剥离的问题。那么避免残留或者干式转移方法可能还是必须的。

北京大学的一篇paper中提到了WSe2 pFET,达成低接触电阻的方案,就是采用直接生长的方案。其中的工艺流程和在Si/HfLaO介电薄膜上生长是兼容的。问题是生长处理温度达到890℃(首个器件?),这在制造方面还是存在相容性挑战的。不过据说这项研究属于p型器件2D材料实现的巨大进步。

总的来说,2D材料对于行业的未来价值是毋庸置疑的,只不过真正实现2D材料的量产仍然存在重大挑战。上述绝大部分研究都采用湿法转移技术,把2D材料从生长substrate转移到最终的wafer上,就聚合物残留、低吞吐之类的问题阻碍了大规模量产。但从IEDM每年在2D材料上面发表成果的频次和数量来看,2D材料作为未来半导体行业的路径还是很清晰的。

感觉有个观点说得还是很对,就是电子、半导体的技术发展之路上,始终有人在说创新已经到头了,但在半导体制造领域,离子注入、high-k gate、EUV、FinFET、GAAFET都相继出现,并尝试解决问题,而2D材料也会成为其中的一份子。SemiAnalysis评价说2D材料如今正处在“valley of death(死亡之谷)”阶段,所以格外需要进一步的行动,以及跨行业与整个链条的协作和投入,包括OEM、foundry/fabless/IDM等等。

关注完未来技术,也不要忘记持续关注当下热门技术与市场进度。芯片设计与制造,是将晶体管、器件、互联构成大规模集成电路的过程。3月29-30日,AspenCore将在上海举办2023国际集成电路展览会暨研讨会(IIC Shanghai),同期举办的EDA/IP与IC设计论坛邀请到多家国内外优秀的IP供应商与IC设计企业发表演讲,欢迎点击报名参会。

与此同时,言及2D材料要率先应用于射频器件,那么与IIC Shanghai同期举办的射频与无线通信技术论坛自然也不应该错过。该论坛将邀请国内外领先的射频芯片、通信技术企业以及终端应用企业作相关主题分享,为产业链提供深度交流与合作的平台。