纳米环栅器件(GAA)是继3纳米以下及FinFET技术后,英特尔、三星和台积电等境外半导体巨头正投入巨资研发的最先进集成电路制造技术。长期以来,CMOS器件的多阈值(Multi-VT)调控是实现高性能、低功耗电路最优应用的关键技术之一。但堆叠纳米片GAA器件由于纳米片间空间(Tsus)严重受限,采用传统的栅金属功函数层膜厚调控以实现多阈值极具挑战。因此,新型多阈值调控技术及工艺集成是目前先进GAA器件集成中的研究重点。

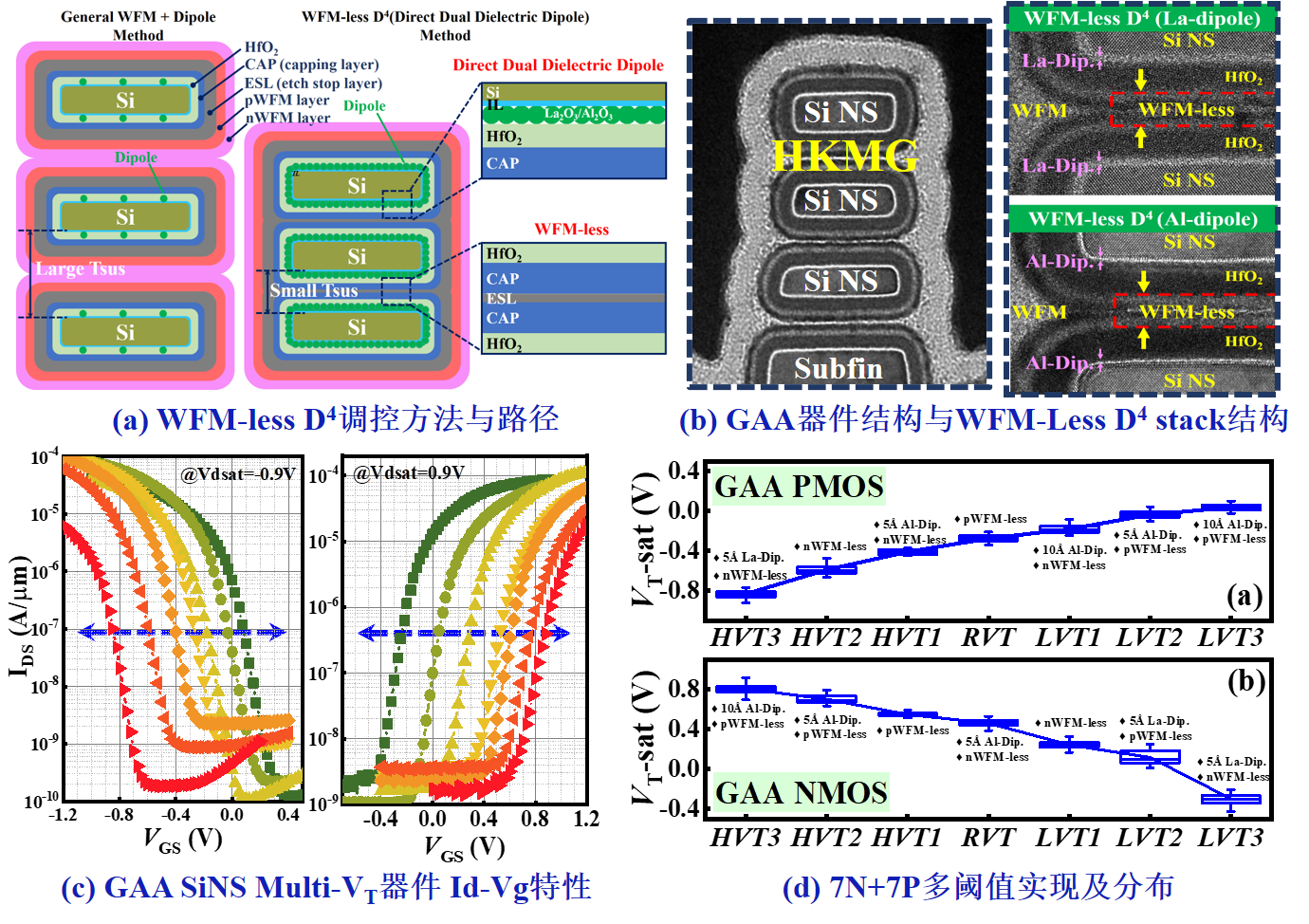

针对上述关键问题,中科院微电子所先导中心殷华湘研究员团队提出了一种无传统功函数金属填充的栅介质界面原位偶极子(WFM-less D4)阈值调控技术,有效突破传统高k/金属栅(HKMG)填充空间的限制,在三层堆叠Si纳米片GAA n/pFET中获得了7(N)+7(P)种类的多阈值集成, 分别实现了最大1105和873 mV的ΔVT调控幅度,达到世界领先水平。该阈值调控技术还适用于Tsus进一步微缩的GAA器件,降低GAA晶体管的寄生电阻和电容影响,提高器件驱动性能与电路工作频率。

基于该研究成果的文章“Record 7(N)+7(P) Multiple VTs Demonstration on GAA Si Nanosheet n/pFETs using WFM-Less Direct Interfacial La/Al-Dipole Technique”入选2022 IEDM先进逻辑技术Session。2022年12月7日,微电子所姚佳欣博士在美国旧金山IEDM大会现场进行了口头报告,并与包括Intel、TSMC、CEA-Leti、IMEC、UC Berkeley、MIT等国际产业界和顶尖研究机构、大学在内的多位技术专家、学者进行了详细且深入的交流与探讨。

该研究由中科院微电子所先导中心独立完成,微电子所是唯一通讯单位。微电子所姚佳欣助理研究员(在站博士后)为第一作者,殷华湘研究员、张青竹副研究员为通讯作者。

该研究得到了中科院战略性先导A专项、北京市自然科学基金青年项目、北京市科技新星计划等项目资助。

图(a)WFM-Less D4调控方法与路径,(b)所制备三层堆叠硅纳米片(SiNS)GAA器件与WFM-Less D4 stack结构的TEM结果,(c)多阈值GAA器件Id-Vg特性@Vdsat=±0.9V,(d)7N+7P器件多阈值的实现及分布