过去的一年,chiplet(小芯片,又称“芯粒”)成为半导体行业的“最热词”,得到了业界的广泛关注。目前苹果、台积电、AMD、Intel等国际芯片巨头均已布局chiplet技术,且推出了多款小芯片设计的芯片,取得了很好的应用效果。同时,在摩尔定律放缓,以及科技脱钩等诸多因素下,Chiplet技术被认为是提升算力密度的重要路径,也成为中国半导体企业破解芯片技术封锁的重要技术方向之一。

在2023年初数天内,中外芯片企业均宣布Chiplet技术的新进展。近日,美国芯片巨头AMD在CES 2023上发布全球首个集成数据中心APU(加速处理器)芯片Instinct MI300,最快2023年下半年发货。中国晶圆封装龙头长电科技近日也宣布,其XDFOI Chiplet高密度多维异构集成系列工艺已按计划进入稳定量产阶段,同步实现4nm节点多芯片系统集成封装产品出货。目前,Chiplet技术已经成为全球半导体产业重点关注的赛道之一。

后摩尔时代的技术路径之一

Chiplet,小芯片,又称为模块芯片,具有成本低、周期短等优点,是一系列先进封装技术的汇总与升级。Chiplet设计分割不同功能模块进行独立制造,再通过先进封装组装成一个系统芯片,不需要全部都采用先进制程在一块晶圆上进行一体化制造,这样可以提升良率的同时降低不良率造成的额外制造成本。

实际上,Chiplet概念很早就已经被提出来。早在2015年ISSCC大会上,美国芯片巨头Marvell创始人周秀文提出了MoChi(模块化芯片)架构概念。同一年,美国芯片巨头AMD公司就以实现性能、功耗和成本的平衡为目标,率先将Chiplet应用于商业产品中,自此之后陆续使用HBM、Chiplet和3D Chiplet等技术研发芯片产品。

2022年3月,英特尔、AMD、ARM、台积电、三星等芯片巨头发起一项瞄准Chiplet的新互连标准UCIe。同月,苹果也发布一个性能爆表的属于chiplet技术范畴的顶级电脑芯片M1 Ultra。4月,饱受芯片之苦的华为也发布了3D堆叠技术专利……Chiplet被认为是后摩尔时代继续提升芯片规模和密度的重要技术之一。

Chiplet具有诸多技术优势,主要体现在:一是可以大幅提高大型芯片的良率;二是可以降低设计的复杂度和设计成本;三是降低芯片制造的成本;四是可以满足多样化市场需求,特别是满足应用端对定制芯片的需求。

目前,Chiplet已被认为是系统级芯片(SoC)集成发展到后摩尔时代后,持续提高集成度和芯片算力的重要途径。据Omdia报告,到2024年,Chiplet的市场规模将达到58亿美元,2035年超过570亿美元,Chiplet的全球市场规模将迎来快速增长。

当前,先进芯片工艺性能提升越来越难,但成本直线上升,使摩尔定律遭遇瓶颈,而作为先进封装技术的Chiplet被认为是缓解摩尔定律的一个有效方式,也被认为是未来满足人工智能、高性能计算等行业需求的重要技术方向之一。有行业机构甚至指出,随着Chiplet技术生态逐渐成熟,中国厂商通过自重用及自迭代利用技术的多项优势,推动各环节价值重塑。

Chiplet进入规模化应用阶段

在CES 2023上,AMD推出了从CPU到GPU、从移动版到桌面版新品,包括Ryzen 7000系列移动版处理器、Ryzen 7000 X3D系列台式机CPU、移动版RX7000独显以及AMD迄今为止最复杂芯片——Instinct MI300等。

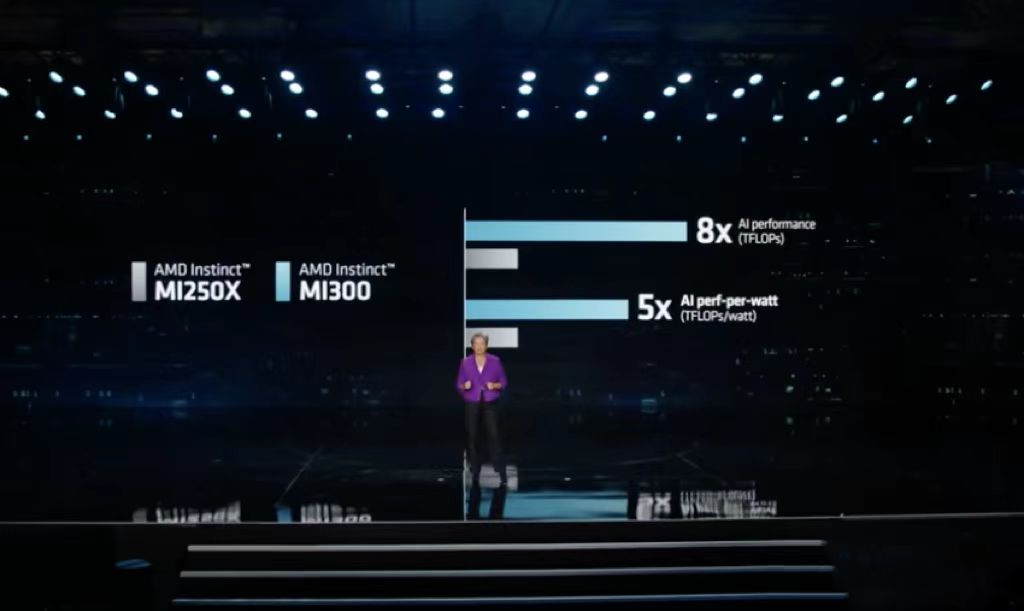

据悉,Instinct MI300是AMD首款数据中心/HPC级的APU,而首席执行官苏姿丰称其是“AMD迄今最复杂的芯片”,相较InstinctMI250X,InstinctMI300可提升8倍的AI训练算力和5倍的AI能效。

AMD首席执行官苏姿丰介绍Instinct MI300

如果对比晶体管数量可以发现,英特尔的服务器GPU Ponte Vecchio集成了1000亿个晶体管;英伟达新核弹H100的晶体管数量则为800亿;而AMD的Instinct MI300的晶体管数量达到1460亿个!

值得一提的是,Instinct MI300采用了当前火热的先进封装技术——Chiplet,利用3D封装技术将CPU和加速计算单元集成在一起。Instinct MI300预计将在2023年下半年交付,首发将部署在美国新一代超算El Capitan上,性能冲上200亿亿次,比当前TOP500最强超算Frontior性能提升一倍。

而长电科技则基于XDFOI™ Chiplet高密度多维异构集成系列工艺,可生产4nm多芯片封装产品,最大封装体面积约为1500mm²的系统级封装。据悉,长电科技XDFOI™ Chiplet技术工艺通过小芯片异构集成技术,在有机重布线堆叠中介层(RDL Stack Interposer, RSI)上,放置一颗或多颗逻辑芯片(CPU/GPU等),以及I/O Chiplet 和/或高带宽内存芯片(HBM)等,形成一颗高集成度的异构封装体。

该制造工艺一方面可将高密度fcBGA基板进行“瘦身”,将部分布线层转移至有机重布线堆叠中介层基板上,利用有机重布线堆叠中介层最小线宽线距2μm及多层再布线的优势,缩小芯片互连间距,实现更加高效、更为灵活的系统集成,另一方面,也可将部分SoC上互连转移到有机重布线堆叠中介层, 从而得以实现以Chiplet为基础的架构创新,而最终达到性能和成本的双重优势。

目前,长电科技XDFOI™技术可将有机重布线堆叠中介层厚度控制在50μm以内,微凸点(µBump)中心距为40μm,实现在更薄和更小单位面积内进行高密度的各种工艺集成,达到更高的集成度、更强的模块功能和更小的封装尺寸。同时,还可以在封装体背面进行金属沉积,在有效提高散热效率的同时,根据设计需要增强封装的电磁屏蔽能力,提升芯片成品良率,有效解决后摩尔时代客户芯片成品制造的痛点。

Chiplet并非“十全十美”

作为中国芯片封装巨头,长电科技是国内较早布局Chiplet技术的半导体企业之一。2021年7月正式推出面向Chiplet(小芯片)的高密度多维异构集成技术平台XDFOI™,利用协同设计理念实现了芯片成品集成与测试一体化,涵盖2D、2.5D、3D Chiplet集成技术。目前,长电科技基于XDFOI™ Chiplet高密度多维异构集成系列工艺的技术优势,已在高性能计算、人工智能、5G、汽车电子等领域得到应用,可以提供外型更轻薄、数据传输速率更快、功率损耗更小的芯片成品制造解决方案。

不过,尽管Chiplet有诸多优势,但该技术并非十全十美的,要真正实现Chiplet带来的集成效应,还有很多问题待解决。具体而言,Chiplet技术挑战不仅包括物理电气工艺/构型、Interposer和导线材料、通信互连/I/O、Analog/Logic design rules、电源和信号控制等挑战,同时还面临着生态和制造端的挑战。

实际上,尽管苹果、AMD、Intel等大厂产品中已广泛采用Chiplet技术,但该技术目前更多为少数企业提供了竞争优势。清华大学教授、中国半导体行业协会副理事长魏少军曾接受媒体采访时表示,“当前Chiplet面临着芯片设计系统思维、设计工具、制造材料、成本等多方面挑战,不能简单地认为,Chiplet具备降低系统复杂度、提升芯片良率、在摩尔定律之外推动芯片性能提升等好处。”

也就是说,Chiplet技术在良率和成本上的优势也是有一些前提条件的。比如,将一颗大的SoC芯片拆分成多个芯粒,相比单个大的SoC可以更好的提升Chiplet的良率,但是这也会带来更多的测试工作。很大程度上来说,Chiplet封装的芯片复杂程度更高,需要晶圆测试段更精确分类测试,避免最终性能降低。同时,在SoC芯片设计时,企业需要将内部封装的各个模块看成一个整体的系统,需考虑到整个系统层级的设计和优化。这也要求EDA厂商、Chiplet厂商和芯片厂商高度协同配合。

另外,多芯粒的封装与组合,要实现芯片互联,需要解决一致性协议问题,自然也要涉及到互联相关标准。

目前,中国Chiplet产业链还不成熟,存在诸多技术挑战,比如芯片测试良率、互连技术、集成封装技术、供电散热等方面的技术挑战,同时还存在芯片IP(知识产权)偏少,产业上下游的支持力度差等问题。2022年12月,中国发布了首个原生Chiplet技术标准《小芯片接口总线技术要求》,将有助于行业的规范化、标准化发展。

总结起来,Chiplet技术是从先进封装的角度来延续摩尔定律,提升芯片性能和降低芯片成本,但通过Chiplet技术集成的SoC芯片的性能根本上也是由芯片工艺的先进性来决定的。比如,AMD发布的Instinct MI300是在4块6nm芯片之上,堆叠了9块5nm的计算芯片,才在性能上被冠以“AMD迄今最复杂的芯片”。