随着大数据时代来临,人们对消费性电子产品的需求更加广泛,在物联网、5G、人工智能与电动车等技术快速兴起下,机器人、无人车辆与无人机等产品也逐渐普及,这些应用的技术需求包含高速信息传输、感知外界环境,还需减少传输延迟,进而达到节省能源、降低风险等目标,以上皆需要非常快速且巨量的运算,使得先进半导体芯片的需求炙手可热。伴随这些技术的进步,芯片中晶体管管的密度越来越高,但基于摩尔定律(Moore’s Law)的超大规模整合晶体的小型化放缓,如今需要在先进封装中进行突破,才能持续增加晶体管的密度。

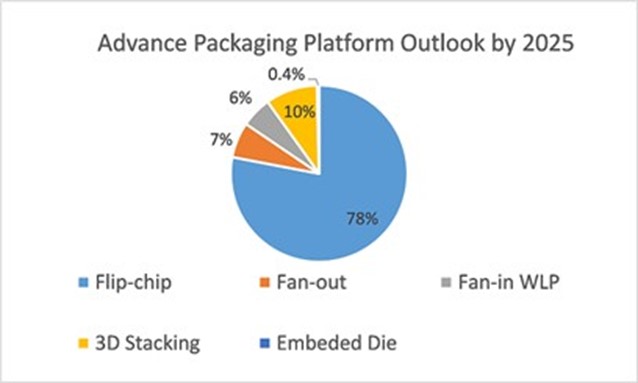

根据市场研究公司The Insight Partners于 2022 年 2 月 15 日所提出的最新报告“Advanced Packaging Market Size, Share, Revenue, Growth, Global Analysis and Forecast to 2028”,由于封装技术的创新、组件的微小化和微机电系统(Microelectromechanical systems,MEMS)的普及,先进封装市场将以 8% 的复合年成长率提高,从2020年大约300亿美元到2028年达到550亿美元。2020年先进封装在半导体封装市场占有约 40% 的份额,预计到2030年时,将提高至60%以上(图1)。此外,预估在2021~2030年间,3D/2.5D IC、扇出封装(Fan out)的复合年成长率分别约为22%和16%,是所有的先进封装技术中,需求量成长最快速的技术(图2)[1]。

图1:2020~2030 年全球封装市场份额[1]。

图2:2025年前先进封装技术市场份额[1]。

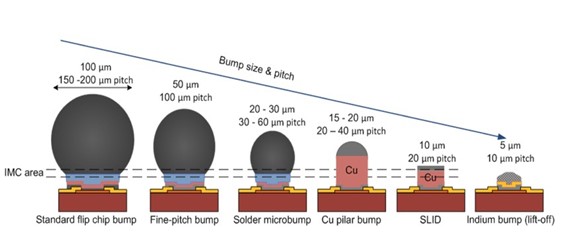

先进封装中晶体管密度的提升,主要由纯铜对接(Cu-Cu hybrid bonding)、微微焊点(Microbump)技术来推动。前者设计用于接点间距10μm以下的高阶产品,可达到更高的晶体管密度,除Cu-Cu对接外还有Au-Au对接。该方法是通过平坦的纯金属相互扩散接合,制造门坎与难度较高,需要更佳的表面平整度及洁净度;后者则是市面上更普遍的技术,主要用于中高端产品,目前最先进的微焊点间距为40μm,随着热压接合(Thermal compression bonding,TCB)技术进步、更先进的机台设计,也许在不久的将来,微焊点间距能缩减为20μm,甚至达到10μm,而微焊点的尺寸约为间距的50%,亦即微焊点可能达到焊锡尺寸10μm以下的次微米级焊点(图3)。

图3:凸点间距与尺寸的微小化发展[2]。

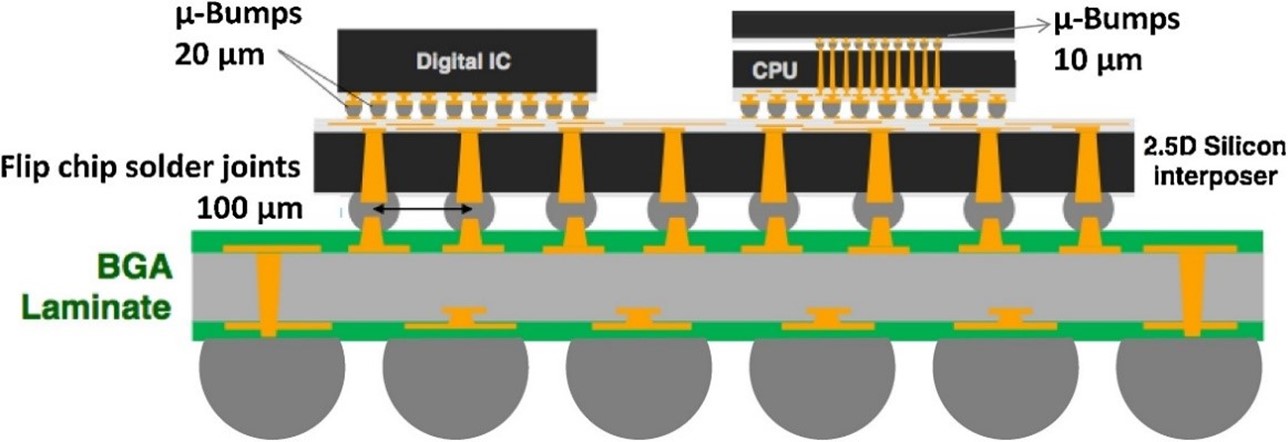

以先进封装中焊点为例,最大的球门阵列(BGA)直径约为760μm、中等尺寸覆晶封装的(C-4)焊点约为100μm、2.5D/3D IC技术中的微凸点(μ-bump)直径为10μm (图4)。与C-4焊点相比,微焊点的直径小了10倍,而体积则相差约1,000倍,表面积/体积比的增加,让焊料与界面的反应加剧,使微观结构产生了巨大的差异。

图4:2.5D/3D IC 封装结构的横截面图[3]。

在2.5D/3D IC中,多层的封装结构与更小尺寸的焊点意味着封装过程将经历多次的回焊(Reflow),使介金属化合物(Intermetallic compound,IMC)快速成长,增进焊点中锡的消耗与IMC的生成,随着焊点中IMC的比例提升,晶粒的性质将显著影响焊点的物理性能。

随着IMC的成长可能对微焊点设计造成什么影响?

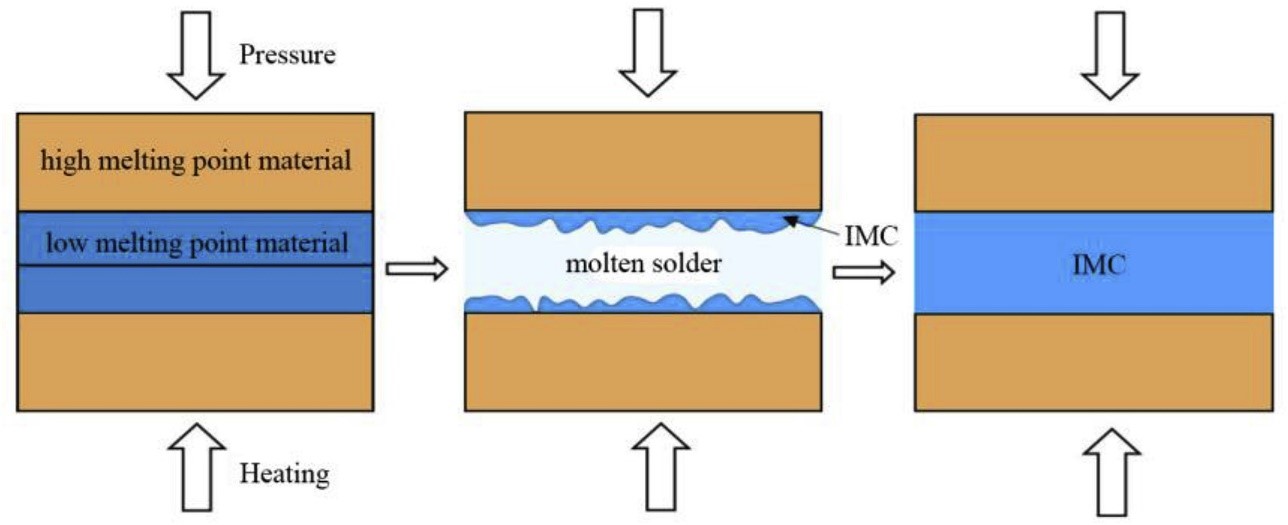

在3D IC中,固液互扩散键合(Solid-liquid interdiffusion bonding,SLID)是一种很有前景的技术(图5),也可称作TLPB (transient liquid phase bonding),特点是在较低的熔点下进行接合,并产生高熔点之全IMC焊点。而在3D IC的多层结构中往往须经历多次回焊,全IMC焊点正好可避免焊料中残余的Sn重新融化而影响芯片的对齐、堆栈。然而,产能是SLID工艺过去面临最大的问题,此技术往往需要进行数小时之久,因而限制其应用性与经济效益。

图5:SLID键合示意图[4]。

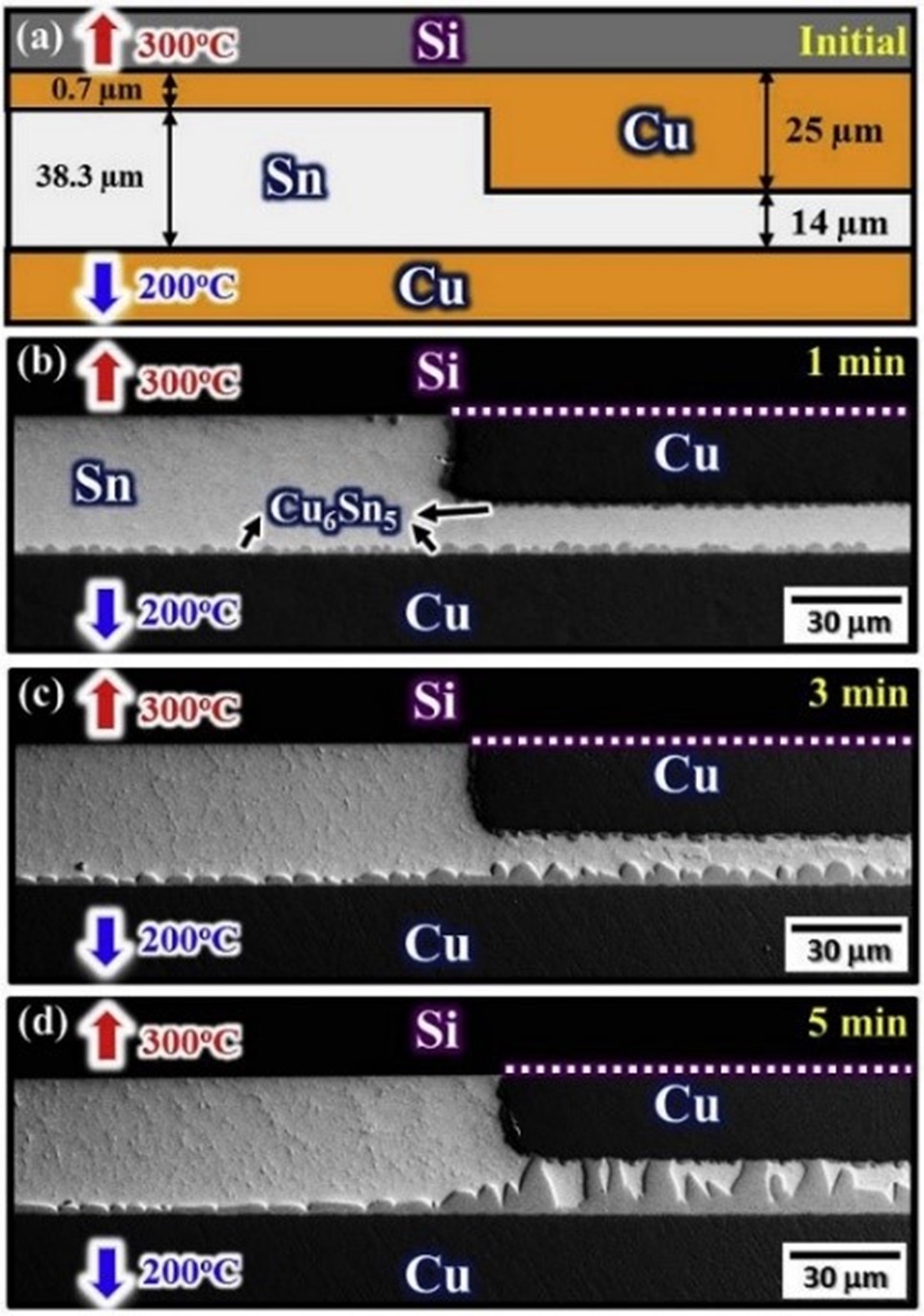

由图6可知,基于相同的工艺参数,当焊点高度有所差异时,IMC的成长情形也截然不同,随着焊点尺寸微小化,使得焊点中IMC的成长速率更快。此外,透过控制工艺中的温度梯度,影响Cu原子在Sn中的溶解度差异,所形成的浓度梯度,将加速热端的IMC向冷端成长,进一步缩短工艺时间、减少冷端基板的消耗[5]。在未来更小尺寸的焊点中,可能仅需要数分钟即可完成SLID键合工艺,使得全 IMC 焊点在实际应用中得以实现。

图6:不同焊点高度下的IMC生长情形[5]。

评估焊点可靠度时,微观结构中形成的空隙往往是人们最常关注的不利因素。在细间距的小尺寸微凸点(μ-bump)封装中,电镀为沉积焊料的工艺之一,如图3中的Cu-pillar bump,从Cu-pillar bump本身到焊帽(Solder cap)的成长,皆可由电镀的方式形成,然而,电镀会在焊料层中引入各种杂质,诸如镀浴中添加的表面平整剂、螯合剂、抑制剂或外来金属原子等,当更多的焊料被消耗(图5),将使不溶于IMC的杂质浓度增加,并被推挤至晶粒边界,形成缺陷或孔洞。

在传统封装中,焊球表面的氧化物、残留的助焊剂也会产生类似的问题,但由于焊点中IMC的比例较低,杂质浓度变化较小,不易造成有害的影响[6],而杂质造成缺陷的机率,会因焊点尺度的缩小、全 IMC焊点的形成而提升,对可靠度有不利影响,例如因应力集中造成的机械强度弱化、电性下降等。

图7:(a)~(d)分别为Cu/Sn/Cu (10µm)在250℃反应1、12、17和20分钟后的BEI[6]。

图8:杂质随IMC成长变得集中[6]。

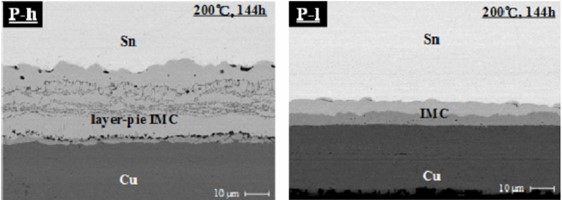

除了焊点微小化造成之空隙,电镀过程中,空隙也受电镀参数与镀浴环境的共同影响而产生,如图9所示,仅添加PEG与Cl抑制剂的组别于P-h (高电流密度)与 P-l (低电流密度)下、制备Cu镀层的焊点微观结构,当降低电流密度经回焊后,可获得完整、无空隙之微观结构。

图9:添加PEG与Cl抑制剂组别 – 在高低h/l电流密度下、镀制镀层回焊后之焊点微观结构[7]。

额外添加促进剂 A 与 B 组别在相同电镀条件下之焊点微观结构(图10),促进剂B在电镀过程中,取代抑制剂PEG吸附位点的能力较弱,且具有较高的杂质浓度而造成空隙。因此,透过调整电镀参数、电镀浴配方的开发,变得至关重要,如电流密度、抑制剂/促进剂的同时添加,以控制晶粒尺寸或是可能生成的空隙[7]。

图10:添加促进剂A与B组别——在相同电流密度下镀制镀层回焊后之焊点微观结构[7]。

透过调控电镀参数、添加抑制剂/促进剂,虽有助于制备出无空隙镀层,但在3D IC的领域,也必须权衡在焊点微小化过程中,添加剂可能造成的缺陷(因杂质浓度提升所导致),对于是否要简化镀浴配方以减少杂质来源、或电镀参数的掌控,可能为电镀工艺在3D IC领域中的关键挑战。

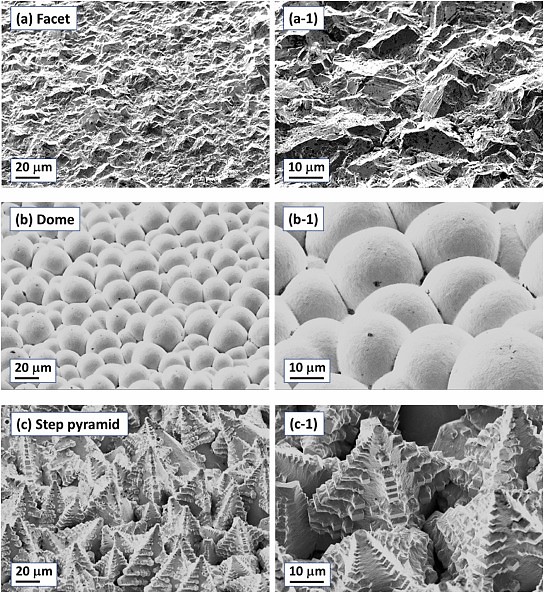

电镀工艺中所使用的添加剂并非总是带来害处,除了能影响回焊后空隙的形成,还可修饰镀层的表面形貌,显示其潜在的应用价值与灵活性。如图10所示,透过开发镀浴中添加剂、调整工艺参数,可制备出具有特殊表面型貌之Cu镀层,并应用于全IMC焊点。圆顶型与金字塔型表面使焊点的剪切强度大幅提升,归功于特殊的Cu表面结构的互锁效应(interlocking effect)、铆接(riveting),使得裂纹不易传递扩展[8]。

图11:刻面、圆顶和阶梯金字塔型 – 表面结构的全 IMC 焊点的剪切强度[8]。

图12:圆顶、阶梯金字塔型焊点——断裂表面的俯视SEM图,(a)圆顶、(b)阶梯金字塔、(c)断裂路径示意图[8]。

由于更细的微焊点间距,焊点中的焊料体积更小,Sn的迅速消耗与IMC的大量形成,虽使TLPB的可实现性大幅提升,但也可能形成空隙影响可靠度。

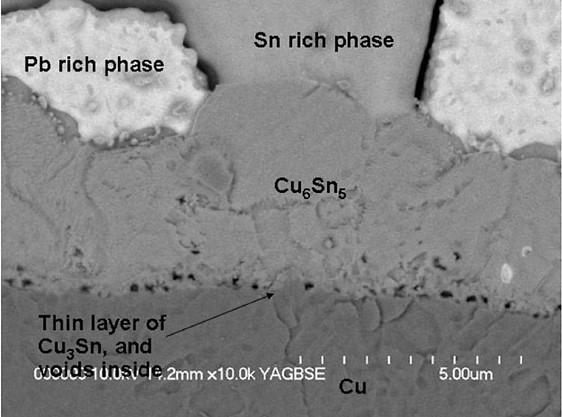

除了工艺中的杂质影响,还有其他空隙形成的原因,如两种元素扩散速率不同所造成的Kirkendall void,以常见的Cu/Sn接口层为例,Cu会先与Sn形成Cu6Sn5相,而Cu6Sn5相会进一步与Cu形成Cu3Sn相。

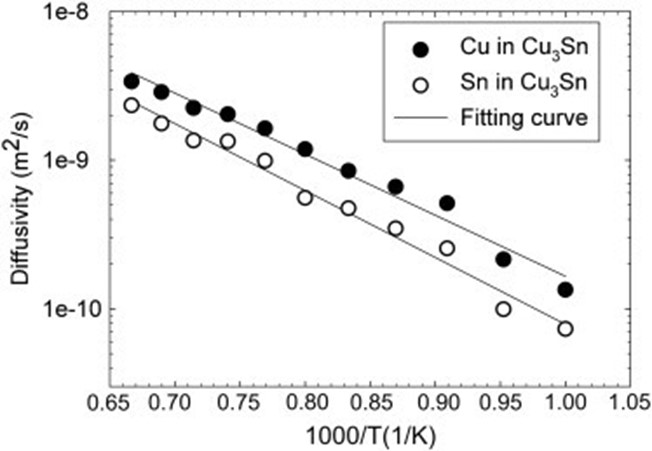

在室温环境300K的情况下,Cu原子在Cu3Sn相中的扩散速率,为原子Sn在Cu3Sn相中扩散速率的17倍,如此巨大的扩散速率差异,使Kirkendall l void出现于Cu/Cu3Sn之接口处(图13),而随着热老化的进行,Kirkendall void面积也会伴随增厚的Cu3Sn层而增加,此为各级封装长期以来的关键议题。

图13:具有各种表面形态的Cu镀层的SEM俯视图,(a)平面型、(b)圆顶型、(c)阶梯金字塔型[8]。

图14:BGA封装接点接口处的空隙[9]。

图15:Cu与Sn在Cu3Sn相中的扩散速率[10]。

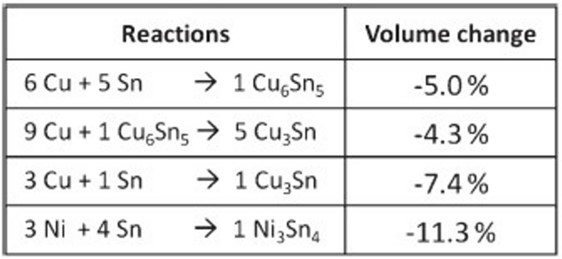

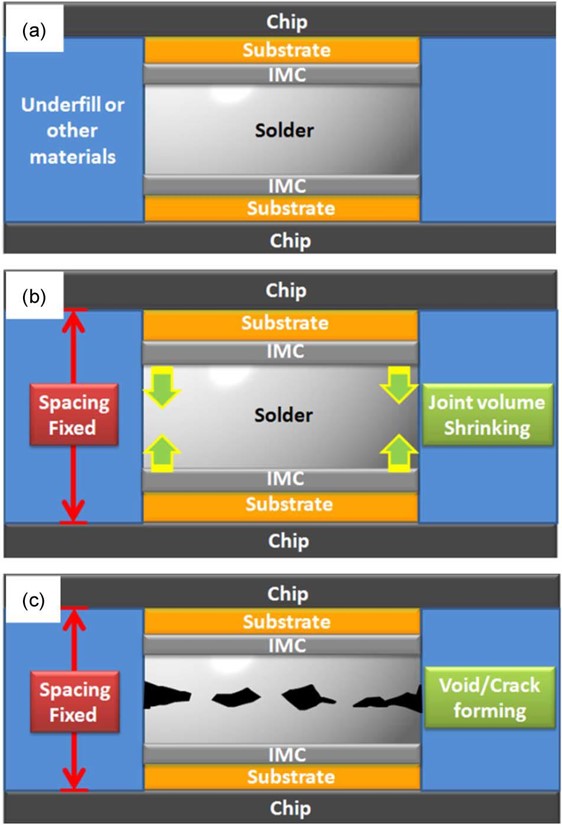

在3D IC中广泛被讨论的TLPB之全IMC焊点,随着焊料尺寸微缩,IMC成长速率增快会提升可制造性的优势,另一方面,回焊与热老化过程中的接口反应使IMC过度成长,也会使接点中的孔隙增多,除了上述提及的Kirkendall void,在热反应下发生的相转所带来体积变化(表1),体积收缩会引起内应力,随着IMC的持续成长、发生的第二次相转变(如Cu6Sn5相转变为Cu3Sn相),都有可能使内应力增加,进而引发裂纹与空隙,对可靠度造成不良影响。

表1:各反应下的体积变化率[6]。

简而言之,IMC的生成是双面刃,由于IMC本质较硬脆,若取代Sn可能使焊点机械性质强化,倘若过度成长则会引发许多可靠度问题。未来3D堆栈的需求会持续成长,TLPB的工艺时间较过去缩短数倍,因尺度缩小使全IMC焊点得以实现,然而在持续的热作用下,如何避免IMC的过度成长引发的空隙,将会成为重要的议题。

图16:焊料和金属反应引起的体积收缩应力,(a) As-assembly、(b)反应进行时、(c)所有焊料消耗完毕[6]。

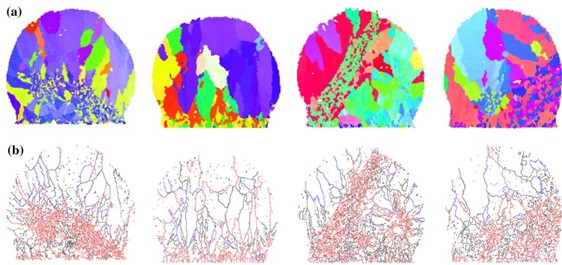

IMC快速生长的现象,在过去大尺寸C-4焊点不会发生,此为全IMC焊点中特有的现象。当两侧的扇贝状Cu6Sn5 晶粒接触(图17),会迅速并成一个柱状晶粒,使晶粒粗化。

图17:(a) Cu/Sn/Cu在260℃下回焊3分钟之SEI、(b) Cu6Sn5之EBSD晶粒取向图 (回焊3分钟)、(c) Cu6Sn5之EBSD晶粒取向图(回焊4分钟) [11]。

一般而言,晶界能量取决于晶粒结晶方位差角(misorientaion),推测大角度晶界具有较高能量,扇贝型Cu6Sn5晶粒会发生极快速的晶粒生长,是由于液态焊料润湿(wetting)造成的大角度晶界,液态通道(Liquid channel)为晶粒生长提供极快的动力学路径。若晶界是小角度倾斜型或扭转型,液态焊料将无法润湿,因此不会发生快速晶粒生长[11]。

晶粒取向差异与晶粒尺寸也存在一定的关系,如图18的BGA焊点[12],为添加Ni的SAC305焊球与OSP Cu基板的界面反应,图(b)中的蓝线、红线与黑线,分别表示大于65゜、介于55~65゜及小于 55゜的晶界角度位错值,从图中可以观察到较低晶界角度位错区域,如红线与黑线区域,通常分布较密集,β Tin 的晶粒也更细小,而形成如图17 (a)中的 interlace 结构。

图18:(a)四个选定的SAC1205-0.1Ni/OSP Cu焊点的EBSD晶粒取向图、(b) 相应SAC1205-0.1Ni/OSP焊点的晶粒结晶方位差角图(misorientation) [12]。

Ni元素层添加于Cu/Sn接口间,为封装中常见的扩散阻障层,可降低Cu-Sn IMC的成长速率。文献中也指出,Ni可作为Cu6Sn5晶粒在Sn当中的成核位点,促使晶粒细化,并提升焊点的机械性质。元素的添加可望应用于3D IC的TLPB焊点中,进行晶粒的细化、晶粒取向多元化等,以强化焊点可靠度[13]。此外,(Cu,Ni)6Sn5相较于(Cu,Ni)6Sn5在(001)和(110)晶面上的性质更相近、且获得强化[14],并由于固溶强化而使晶粒本身硬度提升。

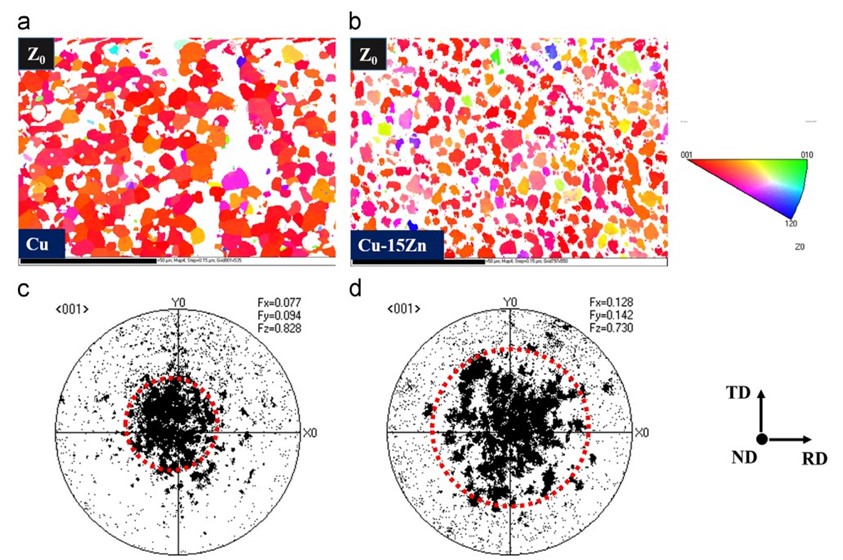

过去也有研究证实 Zn 元素添加所造成的短程有序,可使晶粒细化、晶粒方向性多元化之效果15-17。在TLPB焊点中,Zn元素的添加会使Cu6Sn5晶粒形成interfold的微观结构,如图20 (d)所示,将优选取向(prefer orientation)的晶粒修饰为interfold的微观结构,有望能阻止裂纹传递路径,进而提升焊点的可靠度[16]。

图19:(a) SAC 305/C焊点中、(b) SAC 305/Cu-Zn焊点中的EBSD晶粒方向图(ND)、(c) SAC 305/Cu焊点中的Cu-Sn IMC、(d) SAC 305/Cu-Zn焊点中EBSD极向图 (pole figure) [17]。

图20:(a) Cu/Sn-3.5Ag/Cu TLP键合、(b) Cu/Sn-3.5Ag/Cu-15Zn TLP键合的BSE影像、(c) Cu/Sn-3.5Ag/Cu TLP键合中、(d) Cu/Sn-3.5Ag/Cu-15Zn TLP Cu-Sn IMC的EBSD晶粒取向图[16]。

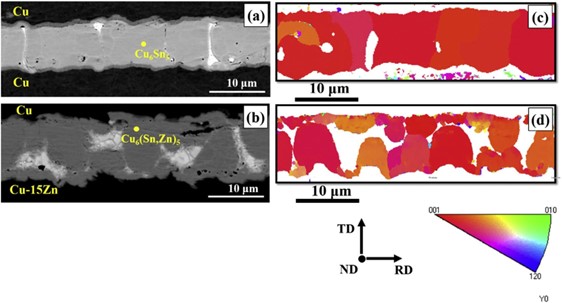

添加Zn元素于基板有助于提升Cu6Sn5相稳定性,避免其转换为Cu3Sn相,以及伴随产生的Kirkendall voids[18-20],如图21所示,基板添加Zn在热老化后,几乎完全抑制Cu3Sn相与Kirkendall voids的成长,显示出Cu6(Sn,Zn)5良好的热力学稳定性。

图21:Sn/Cu、Sn/Cu-15Zn和Sn/Cu-30Zn焊点的横截面图。(a)~(c)为热老化前;(d)~(f) 为150℃下,热老化80天后之截面图[18]。

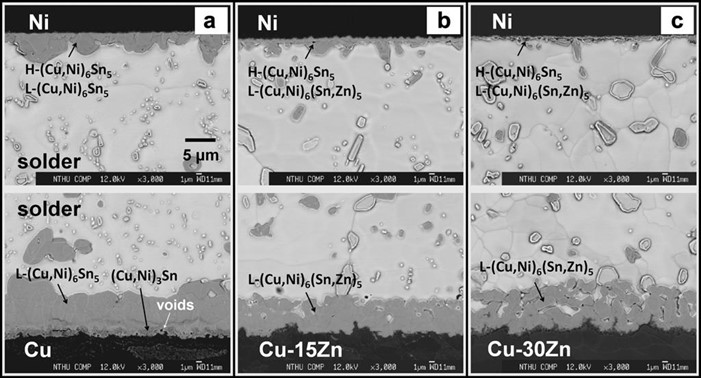

图22为Ni/SnACu/Cu1-x -Zn x的焊点微观结构横截面图,在Cu基板添加Zn,完全抑制两侧基板中的Cu3Sn相,虽然在这些研究中,焊点属于BGA焊点的接口反应,良好的IMC成长抑制能力与相稳定性符合TLPB微焊点需要预防IMC过度成长之需求,在未来3D IC领域中存在其潜在应用价值。

图22:(a) Ni/SnAgCu/Cu、(b) Ni/SnACu/Cu-15Zn、(c) Ni/SnAgCu/Cu-30Zn的接口微观结构[20]。

结论

在未来几年内,先进封装与3D IC的市场需求将持续快速成长,TLPB工艺所制备的全IMC微焊点受益于焊点尺寸微型化而得以实现。由于焊点熔点高,且能将Sn完全消耗,可避免多次回焊后Sn重新融化的对齐与堆栈问题。然而,TLPB所面临的关键性问题,包括IMC的快速成长与过度成长,伴随了体积收缩、相变化与Kirkendall effect所造成的空隙,以及电镀工艺中所造成的杂质污染所致空隙等问题,都在微焊点完全被IMC占据后一一浮现,所幸透过镀浴环境、电镀参数的调整,能显著改善电镀工艺中可能带来的缺陷。

透过元素掺杂于金属基板,除了可望修饰IMC的晶粒尺寸与取向,甚至可提升其热力学稳定性,在经受长时间的热老化时效下,避免相转变所引发的体积收缩或空隙,若将其应用于3D IC的微焊点中为适得其所,可望大幅提升微焊点在长时间下之可靠度。

参考数据:

[2]Ramalingam, Suresh. “Advanced Packaging–Future Challenges.” CMC Conference. 2016.

[3]T. L. Yang , et al. “Effects of silver addition on Cu–Sn microjoints for chip-stacking applications.” Journal of alloys and compounds 605 (2014): 193-198.

[4]Sun, Lei, et al. “Recent progress in SLID bonding in novel 3D-IC technologies.” Journal of Alloys and Compounds 818 (2020): 152825.

[5]Yang, Ting Li, et al. “Full intermetallic joints for chip stacking by using thermal gradient bonding.” Acta Materialia 113 (2016): 90-97.

[6]H. Y. Chuang,, et al. “Critical concerns in soldering reactions arising from space confinement in 3-D IC packages.” IEEE Transactions on Device and Materials Reliability 12.2 (2012): 233-240.

[7]Lee, Hsuan, Wei-Ping Dow, and Chih-Ming Chen. “Effects of additive formula and plating current density on the interfacial reactions between Sn and Cu electroplated layer.” 2016 International Conference on Electronics Packaging (ICEP). IEEE, 2016.

[8]Hsu, Shao-Yu, et al. “Surface modification of Cu electroplated layers for Cu–Sn transient liquid phase bonding.” Materials Chemistry and Physics 277 (2022): 125621.

[9]Mei, Zequn, et al. “Kirkendall voids at Cu/solder interface and their effects on solder joint reliability.” Proceedings Electronic Components and Technology, 2005. ECTC’05.. IEEE, 2005.

[10]Gao, Feng, and Jianmin Qu. “Calculating the diffusivity of Cu and Sn in Cu3Sn intermetallic by molecular dynamics simulations.” Materials Letters 73 (2012): 92-94.

[11]Gusak, A. M., King-Ning Tu, and Chih Chen. “Extremely rapid grain growth in scallop-type Cu6Sn5 during solid–liquid interdiffusion reactions in micro-bump solder joints.” Scripta Materialia 179 (2020): 45-48.

[12]Fleshman, Collin, and Jenq-Gong Duh. “The Variation of Microstructure and the Improvement of Shear Strength in SAC1205-xNi/OSP Cu Solder Joints Before and After Aging.” Journal of Electronic Materials 49.1 (2020): 196-201.

[13]H. J. Dong,et al. “Grain morphology evolution and mechanical strength change of intermetallic joints formed in Ni/Sn/Cu system with variety of transient liquid phase soldering temperatures.” Materials Science and Engineering: A 705 (2017): 360-365.

[14]D. Mu , H. Huang, and K. Nogita. “Anisotropic mechanical properties of Cu6Sn5 and (Cu, Ni) 6Sn5.” Materials Letters 86 (2012): 46-49.

[15]Wei-Yu Chen, and Jenq-Gong Duh. “Suppression of Cu3Sn layer and formation of multi-orientation IMCs during thermal aging in Cu/Sn–3.5 Ag/Cu–15Zn transient liquid-phase bonding in novel 3D-IC Technologies.” Materials Letters 186 (2017): 279-282.

[16]Wei-Yu Chen, Rui-Wen Song, and Jenq-Gong Duh. “Grain structure modification of Cu-Sn IMCs by applying Cu-Zn UBM on transient liquid-phase bonding in novel 3D-IC technologies.” Intermetallics 85 (2017): 170-175.

[17]Wei-Yu Chen, et al. “Growth orientation of Cu–Sn IMC in Cu/Sn–3.5 Ag/Cu–xZn microbumps and Zn-doped solder joints.” Materials Letters 134 (2014): 184-186.

[18]Chi-Yang Yu, and Jenq-Gong Duh. “Growth mechanisms of interfacial intermetallic compounds in Sn/Cu–Zn solder joints during aging.” Journal of Materials Science 47.17 (2012): 6467-6474.

[19]Chi-Yang Yu, Wei-Yu Chen, and Jenq-Gong Duh. “Improving the impact toughness of Sn–Ag–Cu/Cu–Zn Pb-free solder joints under high speed shear testing.” Journal of alloys and compounds 586 (2014): 633-638.

[20]Chi-Yang Yu,Wei-Yu Chen, and Jenq-Gong Duh. “Suppressing the growth of Cu–Sn intermetallic compounds in Ni/Sn–Ag–Cu/Cu–Zn solder joints during thermal aging.” Intermetallics 26 (2012): 11-17.