作为电子工程师,最好的学习成果是,在工作中发现电路有工作不正常的地方后,能够及时找到根本原因。并希望在产品投入生产之前及早发现,越早越好。这里讨论的大部分是一个关于工程“在职培训”的故事,希望如果你没有意识到所有这些问题的话,会预先得到警告,并清楚了解需要注意哪些问题。

陶瓷电容器规格

很多人认为C0G、X7R、B5X和Z5U等常用陶瓷电容术语是一种物理电介质规格。一些制造商会说“X7R电介质”之类的话,但这并不准确。这三个字母代表的不是物理电介质,而是一个性能评级,制造商可以选用任何电介质配方,只要它们符合这三个字母的性能规格。型号名称为C0G或NP0的陶瓷电容器属于Ⅰ类,电容非常稳定,温漂也非常低,通常低于30ppm/℃。C0G类型电容的容积效率也最低。

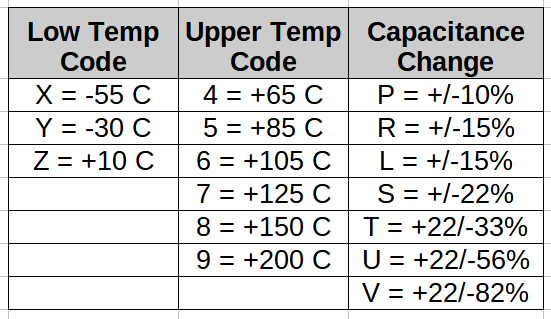

Ⅱ级电容器重点考虑的是尺寸,其三字母编号方法详见表1。

表1:II类电容器三字母标注代码。

电子产品中最常用的型号是X7R和B5X。这一名称并不代表特定的电介质,而是一种规范。制造商可以使用他们希望的任何结构,只要它们符合规范即可。例如,“X7R”规范特征为:工作温度范围为-55~+125℃,而电容变化最大为±10%。

如果在任何地方都使用C0G规范的电容,我们的生活(及我们的电路)将会变得更加美好。问题是它们太大了,在大多数现代应用中无法广泛使用。下面将会看到除C0G类型以外,其他类型“电容器变坏”的地方。

电容上的直流偏置电压

对陶瓷电容的“糟糕体验”,是我第一次决定在新的软件定义无线电中主要使用陶瓷电容进行电源总线滤波时。收音机工作正常,但电源总线发生振荡。该电源是一个5.5伏的大容量电源,为一个由5伏低压差调节器(LDO)组成的大型网络供电。当电压偏离至5.4V时,所谓的0.22F、0402电容器的电容量损失了一大部分,总线没有足够的大电容来缓冲LDO产生的低频交互作用,振荡随之而来!

幸运的是,这很容易解决。我只是在现有电容上背搭了一只2.2F电容,并继续测试第一块电路板。这促使我开始寻找根本原因,并仔细研究电容器数据手册。

在该产品要求大幅缩小尺寸之前,一直使用额定电压通常为50V的0603和0805型电容,供电轨上至少还用有一个钽电容。由于电源轨在80%的时间里为5V或更低,电容器没有出过明显的问题。

正如其他工程师所详述的,许多人都有类似的经历。随着尺寸的减小,多年来一直有效的方法突然失效了。

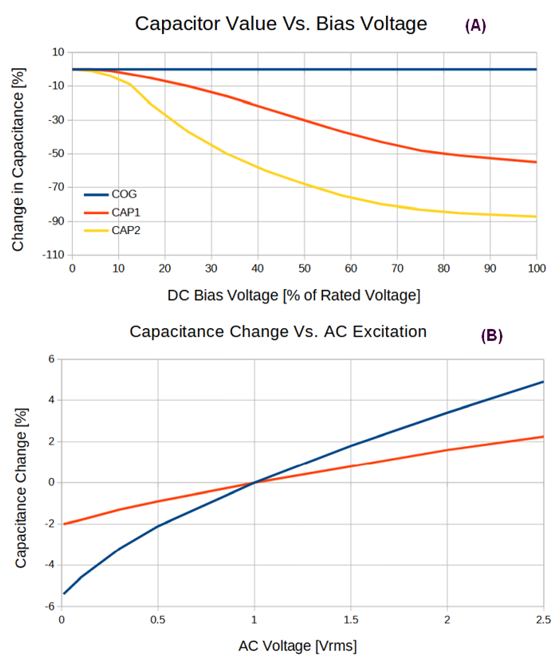

众所周知,有几种电容器的电容量随偏压的升高而降低,如图1所示。

图1:相对于C0G电容,两款0.01F、50V、X7R电容器的电容降低量与DC偏置的关系(A),以及两款X7R电容与交流激励电平的关系(B)。另外,看似相似的X7R电容,不同制造商之间还可能存在巨大差异。

尽管使用X7R规格的电容进行旁路,但我发现电容值大幅降低,因为同时降低了电容的额定电压,这是一种被我称之为“打击平方”的“双重打击”。

之前有专家说:“为了帮助用户,如今所有主要的供应商都至少在其片式多层陶瓷电容器(MLCC)规格书中提供DC偏差信息,”但是最近我发现这不再是真的了。在过去的几年中,这类信息几乎在数据手册中消失,现在要获得这些信息,也必须专门去寻找。

AVX、村田和KEMET等公司的网站上,显示了几乎所有电容器的各种参数和性能曲线,但遗憾的是,这些信息通常不能转用到另一制造商。例如,一家制造商的0.1F、10V X7R在5VDC偏置下,可能会损失4%的电容,而另一家制造商在相同条件下,电容损失量则会高达35%。这表明,即便是同一种规格,也根本不能假设一个制造商的电容性能等同于任何其他制造商的电容性能。

此外,大家可能还记得,2017年,所有类型的陶瓷电容器都出现了全球短缺。当时,制造商们争先恐后地生产尽可能多的器件进行销售。我遇到了几个与生产相关的问题,不仅最终用户做出了未经验证的器件变更,而且制造商也对他们的器件进行了更改,导致器件具有不同的DC偏置电压特性曲线。

观察当今的电容与DC偏置的关系曲线时,会发现是几十年前的制造信息,我开始怀疑它是否与现实相符。它只是没有被更新吗?而最近我发现这些信息不仅是没更新,似乎还被删除了。

电容变差引起的失真

另一个问题是失真。在模拟信号通道中,DC偏置引起的容量变化可能导致使用任何电容器都会出现的问题。我见过太多空间紧张的设计,工程师简单地根据尺寸和额定温度选择电容。这种设计选择只能用于各种各样的数字信号处理,而对模拟信号处理则会产生灾难性的后果。

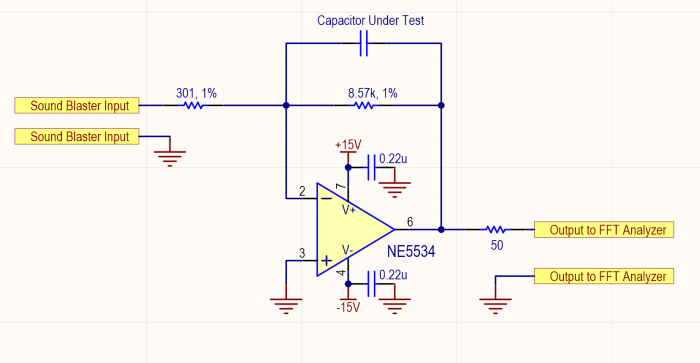

为了展示和度量这种失真效应,使用了我的BlasterAmp项目的一部分,即Sound Blaster USB加密狗的音频输出、用于创建超低失真音频音调的软件、还有用于测量失真的定制18位FFT分析仪、以及图2中的电路。

图2:用于测试失真的NE5534运算放大器电路。

图2中,“被测电容器”是焊接各种被测电容器的地方。当连接到Sound Blaster USB加密狗和一些定制软件时,该电路产生一个高达16位的无失真信号(至少>95dBc)。

图2中的电路仅限于Sound Blaster中DAC的16位失真。按照预期测量了各种0.01F、C0G陶瓷和叠层薄膜电容。都没有给输出增加可测得到的失真。

当我测量X7R电容时,有趣的事情发生了。通常,我只在旁路电路中使用X7R电容,但在实际工作中,有时候为了更有把握,这种电容器也确实会在信号处理通道误用一两只。幸运的是,它们并没有造成任何问题,因为它们的额定电压几乎都是50V,远高于信号摆幅。

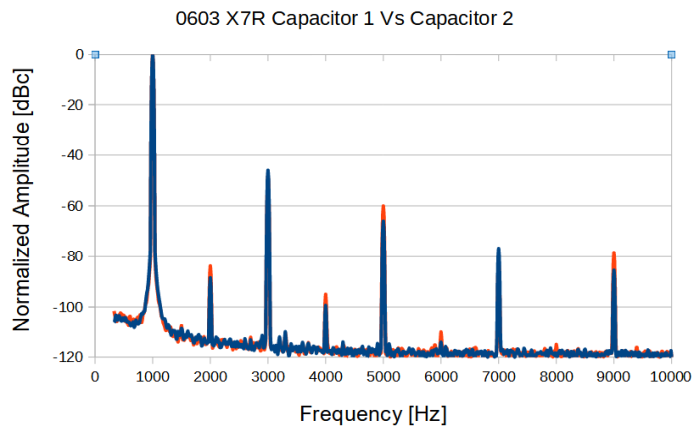

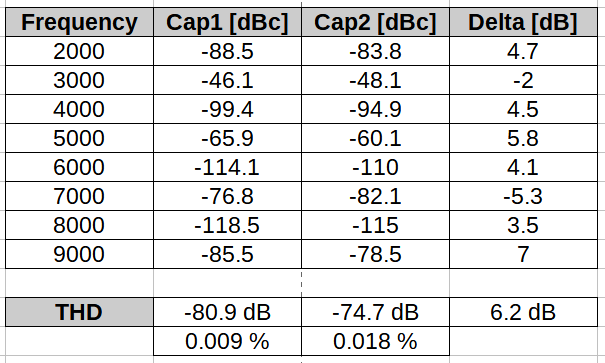

图3所示为两个看似相同的0.01F、50V、0603、X7R型器件的测量结果(信号峰峰值摆幅为20V)。可以看出,这些电容在FFT图上具有非常不同的失真特性。表2給出了更好的失真产物比较,不难发现,其中一个“看似相同”的电容的失真比另一个电容好一倍!

图3:两个看似相同的50V、X7R、0603尺寸电容的FFT失真信号。可以看出,其中一个的失真特性明显差很多。

表2:图3中不同被测电容的结果数据。其中一个电容的总谐波失真百分比是另一个电容的两倍。对于三次谐波,即使在8位电平(-49dBc),两者的性能都较差!

另外,我还测量了一些X7R,0805,50V的电容,甚至还有一款0402,10V额定电压的电容,失真情况和上面类似。0402的测试结果本想更差,因为相对于其额定最大工作电压的相对摆幅更大,但结果并非如此。这让我觉得这些器件的数据手册曲线非常陈旧,根本不符合现实。我还将0402电容的偏置电压提高到50V,漏电流也没有明显增加,难道它可能是基于50V电容工艺制造的?具体情况不得而知,但如果根据电容量下降与工作电压的经典关系曲线,结果应该比实际情况要糟糕得多。

在我翻箱倒柜找电容进行测量的时候,还偶然发现了一个45年前生产的Z5U盘式电容。我原以为其失真特性会非常糟糕,但测试结果却证明,它一点也不差,与现代X7R竟然差不多!(参见图4)

图4:出于兴趣,对一个约50年的Z5U电容进行测量。结果其失真没有预期的那么严重。

从图3中所测电容中取出一只,降低电容上的峰峰值电压,一直降到使失真产物被埋入噪底基底内,然后将数据绘制成图5。

图5:三次谐波失真与施加在图3中一只0.1F、50V、X7R、0603电容上的峰峰值电压的关系。与预期一致,测量的失真遵循拟合的对数趋势线。

图5中绘制的趋势线与对数曲线吻合良好,这表明即使在信号通道中必须使用X7R电容,只要通道的信号电平足够低,也不会有任何失真问题。

制造商数据表中没有列入失真特性参数。如上所示,随DC偏置电压变化,看似相似的电容容量变化差异很大。

工程师所能做的就是远离除C0G以外的任何电容器,或者是在可能会出现失真的地方使用薄膜电容器。即使仔细测试也不一定能确保成功,因为永远不知道零件的设计或结构何时会发生变化,从而导致问题。是的,这意味着尺寸可能会成为一个问题,但有时必须进行设计折衷。

陶瓷电容的压电效应

在与一些知识渊博的锁相环(PLL)设计人员一起工作时了解到这一点;他们说,除C0G或X7R电容之外的任何电容都会有问题。这个“问题”是,除了用于制造C0G电容的电介质之外,任何电介质都使用一种自然压电材料,当变形时,将在器件两端产生电压。

我认为,是在显示冷却风扇旋转频率上的RF边带设计中,PLL设计人员首次发现这个问题。风扇导致PCB振动,这种振动导致相关电容产生足够的压电电压,对PLL的振荡器谐振信号产生了调制,从而产生边带。将电容改为C0G型后,问题就解决了。

电容器行业都知道这一点,他们称之为:“唱歌电容器”,因为很多人了解这种压电现象的方式与我的经验相反。即如果在其中一个电容上施加交流电压,电容内部结构就会自行弯曲,如果频率、电压和安装方式巧合而产生谐振,PCB就会变成扬声器,产生听得到的音噪。

阅读许多笔记本电脑的评论有时会描述在某些笔记本电脑的特定负载条件下可以听到的声音。他们通常将此描述为“线圈呜呜声”,但它可能真的是一个“唱歌电容器”

一些制造商修改了其电容器的设计,以缓解这一问题并降低可能的音噪。过去也已经做了一些很好的工作来证明和衡量这些问题,本文没有必要赘述。

正如我根据其他设计师的经验提到的,在模拟设计中,除了C0G和X7R电容之外,我不用任何其他电容,只在必要的地方使用更高密度的电容器,比如FPGA的电源焊盘之间等地方、或严格的数字设计中。但是,如果在时钟线路中使用这种压电效应非常大的电容,谁能保证某些压电电压不会引起开关阈值抖动,从而导致线路中产生不必要的时钟抖动呢?小心为妙!

我一直认为X7R电容不会受到压电问题的影响,但事实也并非如此,因为X7R电容使用的电介质材料本身也具有压电特性。只是到目前为止,压电引起的电压非常低,故不会带来任何问题。这种情况随时可能发生变化,正如我在2017年大电容器短缺时的经历所示,所以最好非常谨慎。或者在适当的情况下使用专门设计的低音噪电容。

陶瓷电容的开裂

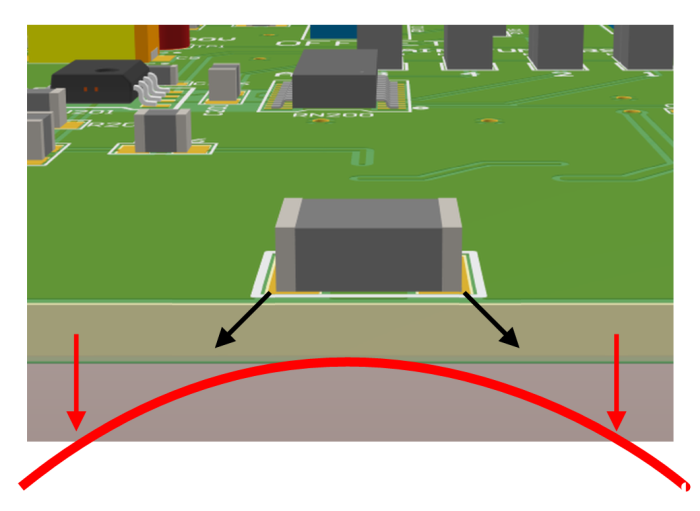

陶瓷电容器非常易碎。谁没弄破过或者把端盖搞掉过?在薄PCB上使用大的陶瓷电容器会加剧这种脆弱性,其中PCB翘曲会导致许多电容器破裂(如图6所示)。我的经验是,在标准厚度为0.032~0.062英寸的PCB上,使用任何大于1206尺寸的器件,我都会感到担心。我甚至以工字梁的方式直立安装电容器,以减少可能的应力。许多大型陶瓷电容器阵列甚至安装在应力消除框架中,以减少可能的开裂应力。

图6:如果对任何焊接好的PCB组件施加力,将会导致弯曲(红线)。那么沿弯曲安装的任何零件将在其安装点受到力的作用(黑箭头)。陶瓷电容器非常脆,通常首先受到翘曲力的作用,并在焊接点爆裂。

从某种程度上来说,电容结构的确很重要,但所有陶瓷电容都容易因翘曲应力而破裂。谨记这一点,并根据元件尺寸使用适当厚度的PCB,以减少可能的弯曲。标准厚度为2.2~3.0mm的PCB比0.8~1.6mm的材料坚硬得多,可能足以解决任何潜在的翘曲问题。

请记住,翘曲应力不仅发生在电路板发生物理变形时,整个组件的温度循环也会产生足够大的应力,使陶瓷电容破裂。

一些制造商生产的电容器具有特殊柔性或软焊接端,故允许焊点实际翘曲一些,这可以大大有助于缓解问题。

对于任何小于0603的元件,其另一个实际问题是,当处理电路板或试图将组装好的电路板放入坚硬的/法拉第屏蔽的金属化防静电袋中时。这些类型的金属化袋非常坚硬,可以非常容易地从板上剪下小零件。在将组件放入坚硬的法拉第屏蔽袋中之前,将组件放入更柔软或有衬垫的防静电袋中可以防止许多损坏问题。

不知道还有什么不知道

所有这些电容问题都是众所周知的,并有文献记载,但仍未得到普通工程界的广泛认可。故直到如今,仍然看到一些设计,试图在模拟信号通道中使用尽可能小的电容。遗憾的是,这些设计师还都将靠自己亲自了解并经历电容下降、失真和压电问题。这是很不幸的事情!因为像我这样,被前者的经验引导着绕过陷阱的痛苦要小得多,所以如果不是我亲自遇到所有这些问题,我也不会遭受这么多痛苦。

最近,在电容器严重短缺之后,我重新评估了基于压电经验法则究竟可以做出多少推断,就像X7R电容器在某种程度上不受这个问题的影响。现实教会我不再盲目假设,而是更加谨慎。正如TDK应用说明书中所述:

“工程师不能仅根据……{电路之外}……的测量值做出通用性假设!”

仔细对电路中选用的器件进行测试,而不要试图根据其他类似的器件作出推断。它们可能完全不同,更糟糕的是,这可能会在下一次零件短缺到来后的一周里就发生变化。

只有电容器会出现问题吗?

不久前,当凌特科技开始生产18位和20位ADC时,他们发现即使更小的SMT电阻也会引起失真。事实证明,12位和14位分辨率的实现相当容易,但当分辨率大于16位时,就需要精心设计了,需要针对每个器件,仔细检查其非线性。包括在焊接好的电路板上进行“敲击”,以寻找压电效应!

(参考原文:Ceramic capacitors how far can you trust them)

本文为《电子工程专辑》2023年1月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅