我们之前写过挺多文章去谈Intel的尖端技术的——这家公司过去的不少技术对半导体行业都影响巨大,比如说FinFET结构晶体管、Hi-K金属栅等。不过Intel目前的境遇可不怎么好,公司Q3财季营收(revenue)同比滑坡20%(GAAP),营业毛利(operating margin)出现赤字,净收入(net income)则锐减了85%。

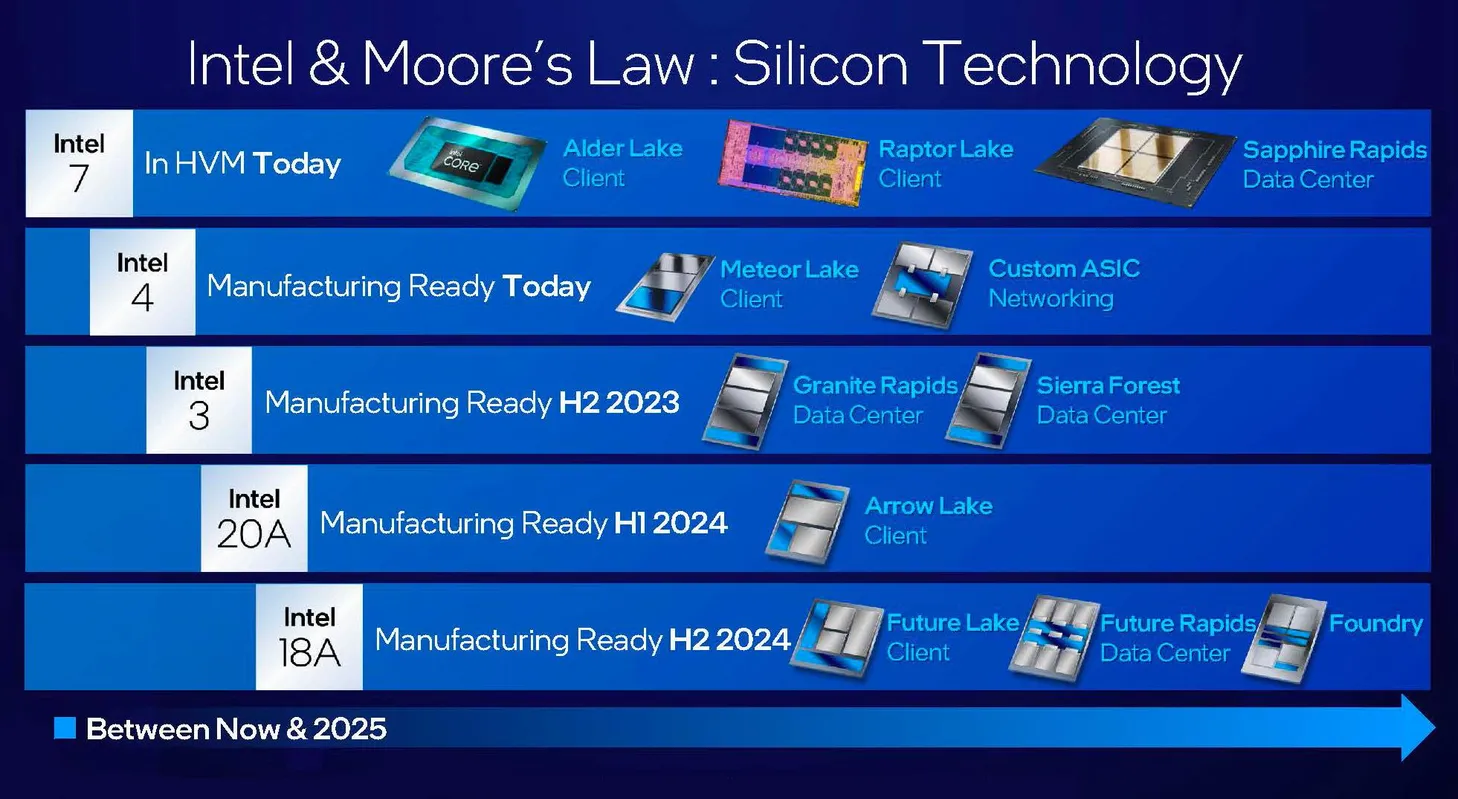

市场内卷和大环境不佳是外部因素,如近几季的PC出货量大幅滑坡是共识;而Intel自身在半导体制造工艺技术决策和发展上的失误,致其落后于竞争对手是内因。我们比较关注的Intel的CCG(客户端计算事业部)季度营收81亿美元,同比下滑了17%。不过Intel CEO Pal Gelsinger认为Intel业绩表现是稳健的,而且在半导体制造技术方面推进稳定,包括Intel 4工艺在推进量产,Intel 3也在“按计划推进”。

最近的IEDM大会上,Intel还特别表示20A、18A工艺量产都会放到2024年——18A的量产计划是提前了的。而且据说20A和18A的内部测试芯片和潜在foundry客户已经达成了流片。

即便外部有那么多唱衰的声音,Intel这类企业的立身之本还是在尖端技术。Intel 4/3/20A/18A、PowerVia供电技术、EMIB和Foveros先进封装这些自然是个中关键。不过实际上,不只是近在眼前的技术很重要——Intel本身也扮演着摸索半导体制造技术向前发展的角色,所以更前沿的技术也重要。

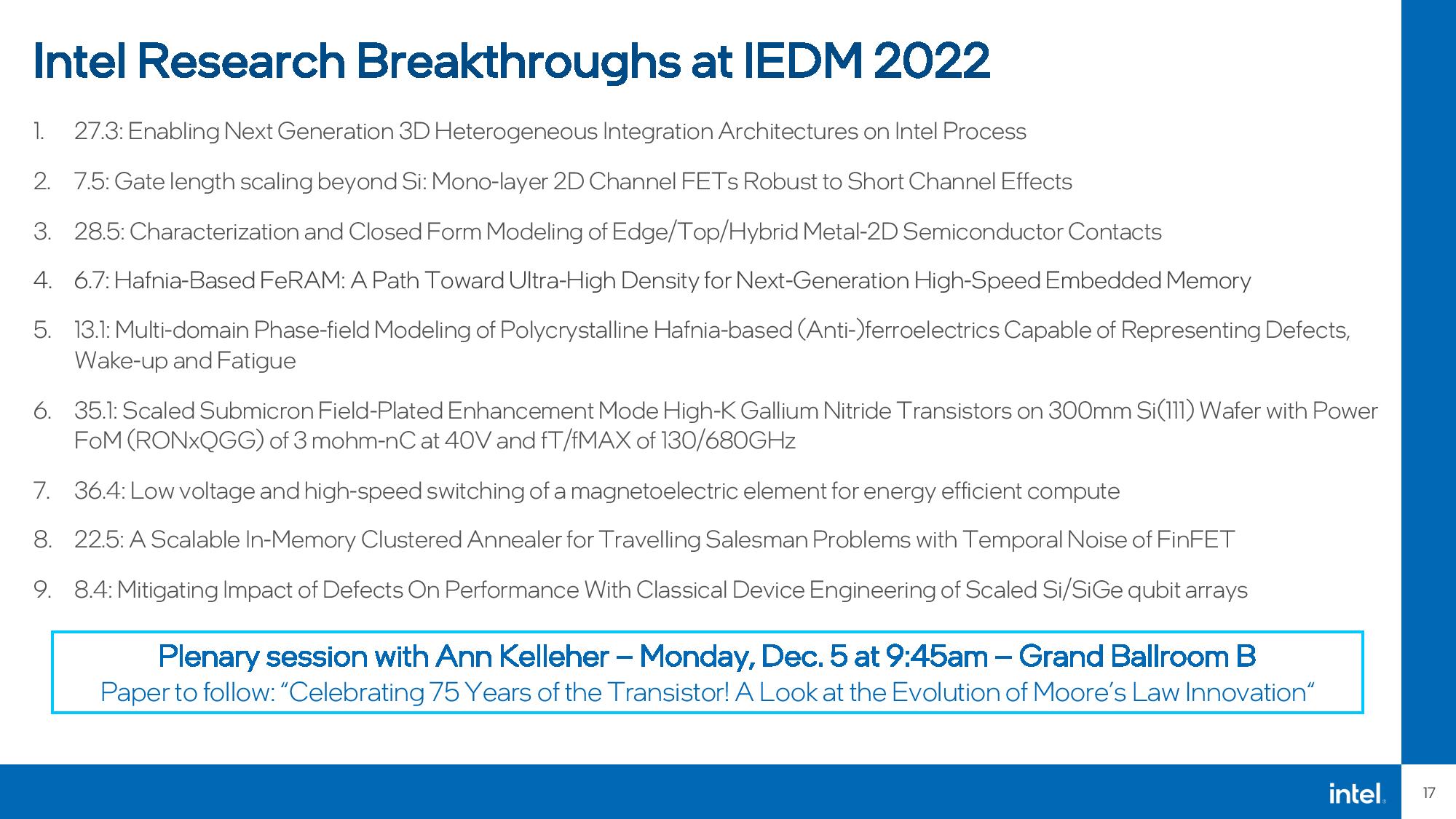

在IEDM 2022上,Intel发了多篇研究paper,内容包括2D材料、3D封装技术、某种断电不会丢失状态的晶体管、可堆叠在逻辑芯片上方的嵌入式存储等。新闻稿中说“为在2030年打造出万亿晶体管芯片铺平道路”。我们选择其中一部分来谈一谈,这些技术都有望在近未来,在芯片上发光发热;而对这些技术的了解也有利于我们把握和观察半导体制造技术的未来。

有一种新的3D封装技术

前两个月的电子工程专辑杂志封面故事详述了先进封装技术的重要性,及当前发展趋势;去年Intel Accelerated活动期间,我们也详细介绍过Intel在2.5D和3D封装技术上的未来规划。

简单来说,当摩尔定律放缓,且半导体制造——尤其是尖端工艺的成本越来越难以控制,导致行业只能从其他层面来探寻性能增长和缩减成本的方式。而先进封装成为方向之一。

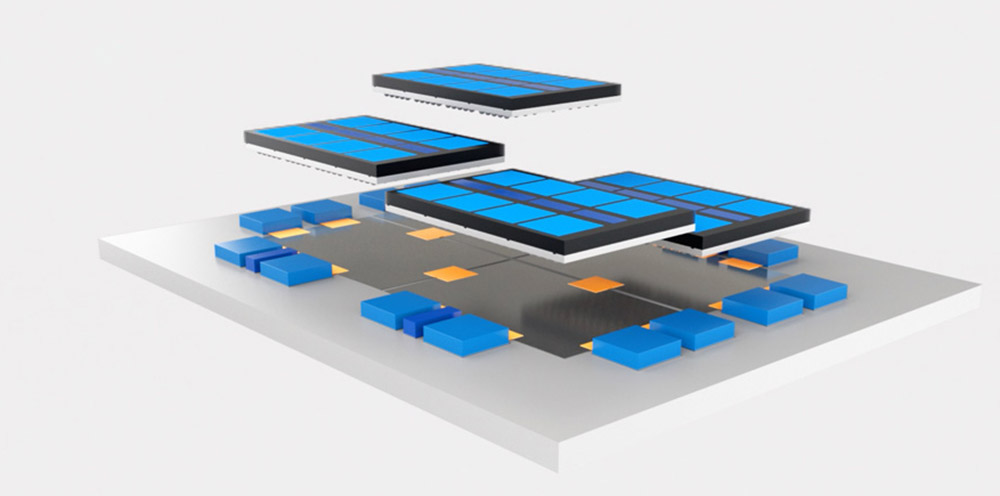

把原本要用尖端制造工艺生产的一整颗大芯片,切分成好几块,每块都用最适合的工艺来造;然后再把切成的好几块die或chiplet,藉由先进封装工艺集成到一起,组成一颗完整的芯片。这类方案能够有效降低制造成本,不仅因为小尺寸的die造起来良率更高,而且也不是每个die都需要用到最先进制造工艺;另外在维系可承担成本的同时,也能有效达成性能增长。

“封装”一词所描述的,不仅是像打包一样,把die都包装起来,还在于采用某种方法,令其可与外部世界连接到一起。比如CPU要封装以后,才能放到主板上工作,因为无论是供电还是数据通信,总需要有个通路,让CPU与主板能够相互沟通。

其实“先进封装”中的“先进”部分是在描述芯片与外部“连接”的密度足够高,主要是数据I/O。过去几十年封装技术发展,达成的I/O接触凸点间距(bump pitch)微缩幅度,在摩尔定律指导的晶体管尺寸微缩幅度面前是完全不够看的——这其实也给芯片性能释放造成了限制。

所以台积电、日月光、三星、Intel、索尼之类的企业一直在寻求先进技术,来增大I/O密度。现在所说的2.5D、3D封装一般藉由硅中介(silicon interposer)、硅桥(silicon bridge)或者hybrid bonding(混合键和)的方案,来把多个die连接起来。Intel的EMIB、Foveros方案,台积电的InFO、CoWoS方案都是比较知名的。

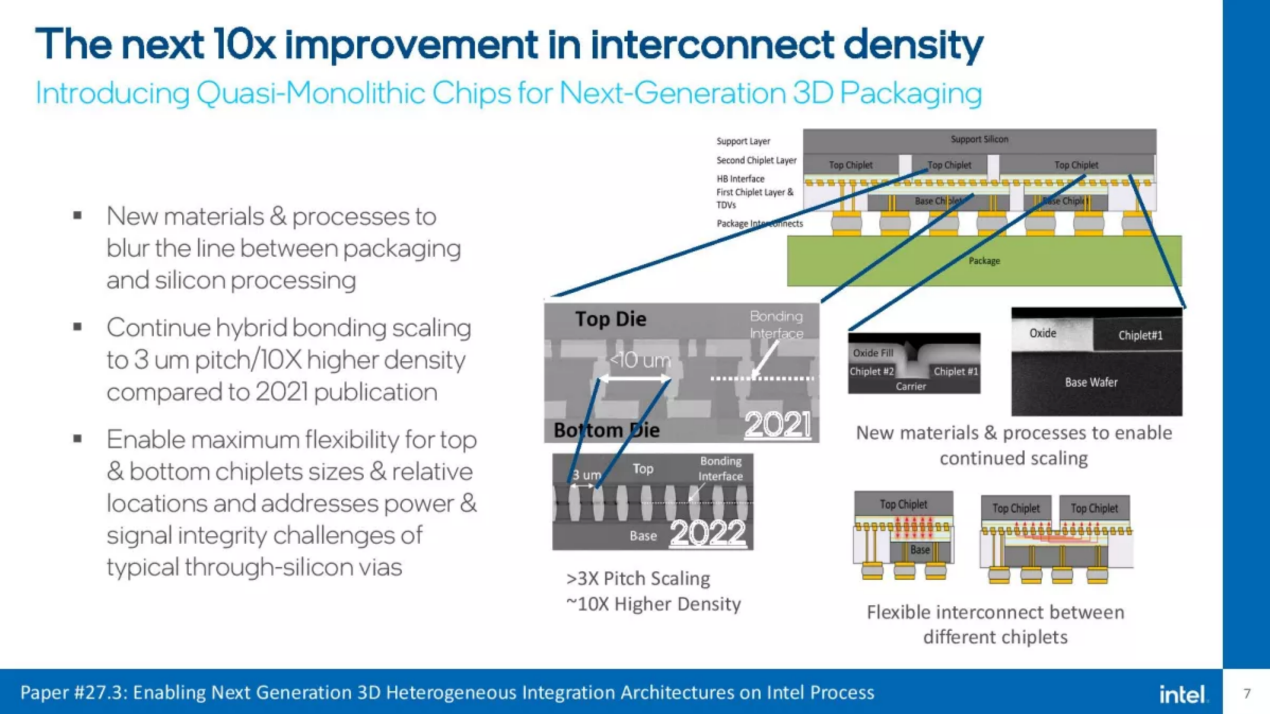

不过Intel认为,现有的这些方案在性能、功耗和成本上仍然没有那么理想。所以Intel在开发一种新的名为QMC(Quasi-Monolithic Chips,准单片)的封装技术。Intel期望QMC所能达成的,是即便采用多die方案,在性能和功耗上也几乎可等同于monolithic单die芯片。这其实就要求多die互联的I/O效率足够高。

QMC本身是一种hybrid bonding技术。Hybrid bonding在互联时并不采用bump,而藉由TSV铜铜直连的方式进行die之间的互联——如上下两片die的3D互连(上图);QMC当然也支持上下两片die的垂直堆叠方案;据说QMC键合间距达到了小于3μm的程度,能效和性能密度又大约10倍的提升(相比于去年IEDM公开的方案)。3μm这个值相较于Intel路线图上已经有的Foveros Direct的互联间距10μm级别就低了更多。

其实去年IEDM上,Intel公开的<10μm的互联间距,宣传中就已经提到了10倍提升;可见先进封装技术这些年的发展速度还是相当之快的。目前尚不知QMC在传输功耗、I/O密度方面的确切数字,不过Intel表示,互联密度和功耗表现都堪比monolithic单die方案,这就让先进封装方案未来有了进一步被期待的依据。只是不知道QMC何时正式问世。10μm级Foveros Direct的计划量产时间是2023年。

2D材料方面的研究

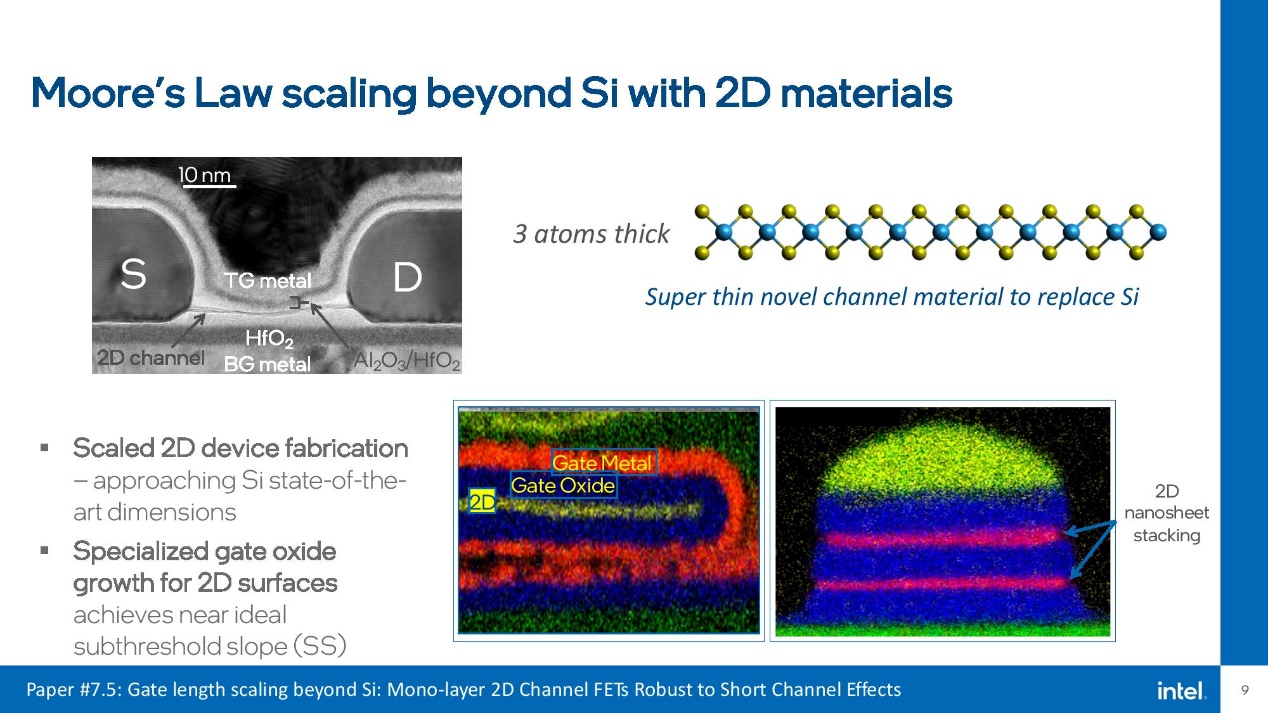

《5年以后,1nm晶体管大概长这样…》一文大致提到了可能2030年以后才会普及的2D材料FET器件。这也是行业研究了多年的方向。好像直到今年为止,业界都认为2D材料要进入半导体制造的规模化量产还不大可能。在去年的IEDM上,Intel也大致介绍过RibbonFET(也就是GAAFET)的2D材料FET器件。

所谓的2D材料主要是指TMD(transition-metal-dichalcogenide,二维过渡金属硫化物)材料,比如二硫化钼、二硒化钨;这类材料可以达成更薄的沟道,实现gate length的缩减和高沟道迁移率。未来半导体制造走向2D原子沟道似乎也已经是不少企业机构的共识。

对应于2D,现在我们所说半导体制造用材料的硅乃是3D晶体,这就决定了它在微缩方面是存在限制的。而2D材料,所谓的“平面内键合”带来原子级的厚度——可达成仅有3个原子的厚度。Intel此前的研究,就提到这种材料可以应用到GAAFET晶体管上。

我们知道,GAAFET晶体管结构相当于把原本FinFET的fin给90°横置了,被称为nanosheet——一个GAAFET器件上会在垂直方向有几个nanosheet。这些nanosheet四面被gate栅极所环抱。从Intel的计划表来看,Intel的GAAFET晶体管——被其称为RibbonFET——会在2024年的20A工艺上到来。

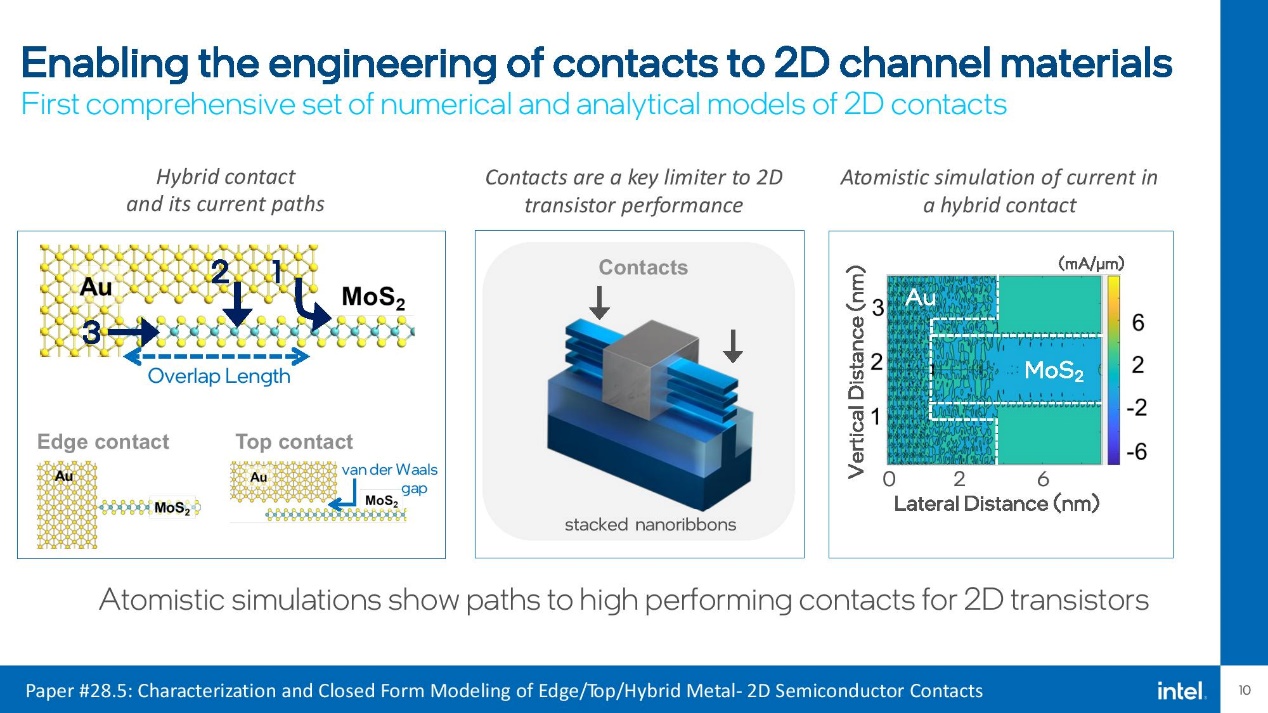

Intel在这次的paper中提到,这种GAAFET结构可以用上仅3个原子厚的沟道材料,室温下也能达成低漏电流。以2D沟道材料的厚度,要建立到nanosheet的电连接是有很大难度的,所以Intel对电连接拓扑进行了建模,具体见上图。这对于理解2D材料性质和工作方式很重要,也是未来持续做深入的一部分。

当然了,作为一种未来技术,2D材料的应用目前应该仍然有不少技术挑战,最早的RibbonFET应该也看不到对应技术的量产。

Intel在新闻稿中说“英特尔展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅三个原子的2D通道材料,同时在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。这是堆叠GAA晶体管和超越硅材料的固有限制所需的两项关键性突破”。“研究人员展示了对2D电接触材料的拓扑结构的首次全面分析,有望为打造高性能、可扩展的晶体管通道进一步铺平道路。”

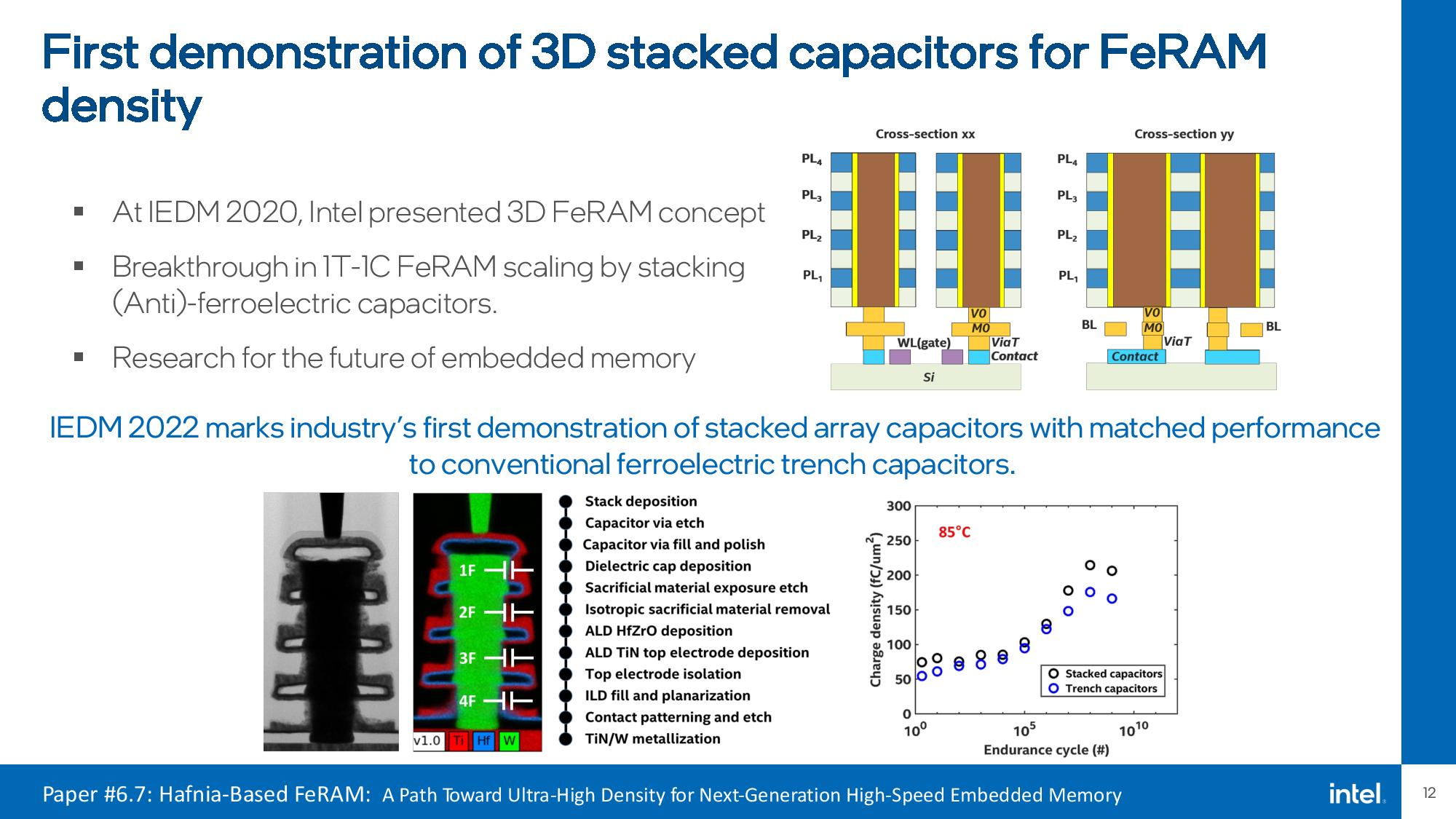

3D堆叠的FeRAM和其他技术

另外一项值得一提的是,Intel这次还提到3D堆叠的FeRAM演示,或者应该说是铁电电容器可以垂直堆叠到逻辑电路die晶体管的上方。换句话说,以后存储部分可以直接叠在处理器逻辑电路的上面。而且在存储容量方面,每个trench沟槽可以存放4bit数据。

有关这项技术的应用,估计应该是增大存储密度、增大带宽,降低访问延迟,增强片内cache的性能。Intel说今年的成果在于,“业界首个3D堆叠FeRAM电容器阵列,且性能达到传统铁电沟槽电容器的展示”。

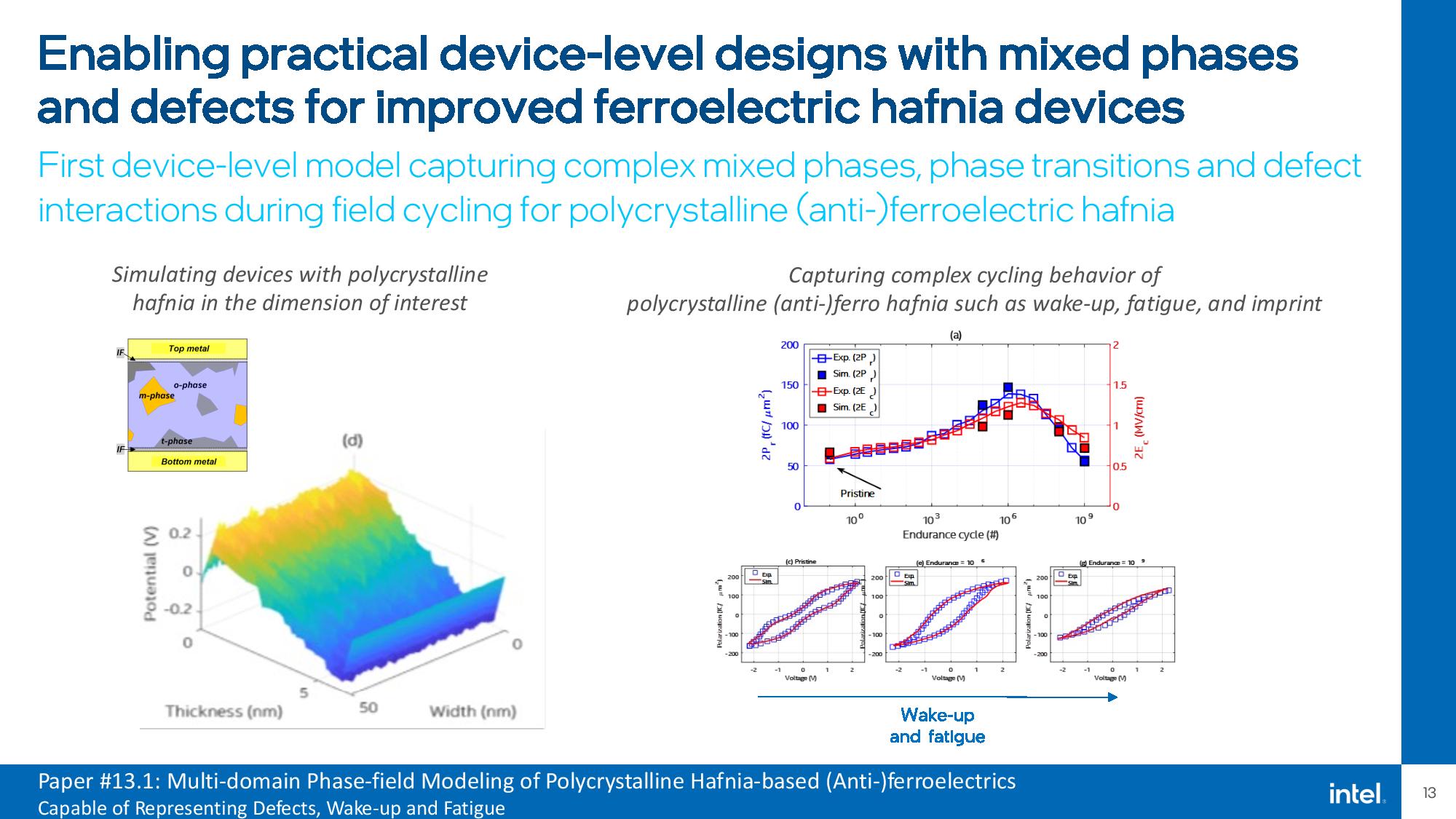

除了上述研究,Intel还宣布对于铁电氧化器件(ferroelectric hafnia)的混合相位与缺陷进行了建模;正在研究某种“不会遗忘”或者应该说是在断电以后不会丢失数据的晶体管——可类比于非易失性存储单元,不过这种可保留状态的技术是针对逻辑晶体管的,据说Intel在这项技术的研究上突破了两个重大关卡;量子计算相关的,存储比特位信息更好的方法;相关300mm氮化镓晶圆的技术等等...

有兴趣的同学可以关注近期Intel对于相关技术的陈述和解释。虽说在这类顶会发布的技术未必有机会走出实验室,但其存在和介绍也对行业探索有着相当大的帮助作用。

以上这些都属于未来技术发展的研究型储备,落到实处还得是当下可商用的产品。这两年Intel的日子过的不大好,不过intel对外表现的态度一直还是挺乐观的,大概是对后续技术更新相对乐观的原因吧。

Gelsinger上任以来,Intel的产品发布速度明显变快了。似乎13代酷睿到手还没多久,几个月后14代酷睿处理器就又要来了——不仅是其中的compute die基于Intel 4工艺,而且整颗芯片采用chiplet多die方案,同时基于Intel的Foveros封装工艺。

虽说Intel 4作为Intel首个应用EUV的工艺,比台积电晚了快4年,但现在Intel明显在加快工艺迭代速度。此前我们就分析了Intel 4,这个工艺节点实际上更靠近台积电3nm(虽然它只有HD单元库),而非N4。而Intel 3按照Intel的计划会在2023下半年准备好量产,率先用于数据中心的Granite Rapids和Sierra Forest。

2024年上半年Intel的20A工艺就要做好量产准备,也就是首个应用了PowerVia技术+RibbonFET结构的晶体管——如果计划顺利,则应该在这个时间点可达成与竞争对手的齐头并进。

另外18A做好量产准备的时间提前到了2024年下半年,Intel准备在这代工艺上正式走到竞争对手前面;这代工艺上,Intel还会率先采用ASML的0.55数值孔径的EUV设备。“2025年晶体管性能和功耗会再次回到领先地位,我们正在这条路上持续行进。”Gelsinger说。

不过我们也时常在说,半导体尖端制造工艺不只是成本在增加,难度也在指数级增加;目前仅剩的3家参与尖端半导体制造工艺竞争的fab厂都已经有了工艺开发进度延后的历史。所以能否按照计划表来行进,还是个未知数。加上目前市场大环境不确定因素甚多,近两年的半导体尖端制造技术状态变化显得更有意思了。