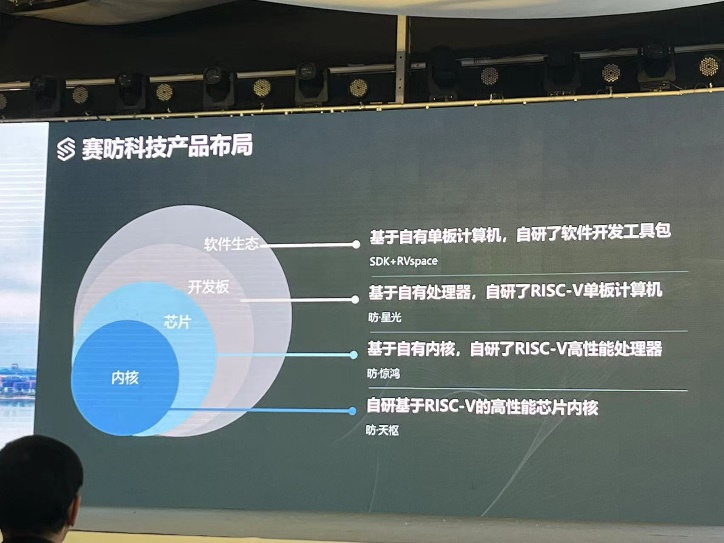

从2018年成立至今,赛昉科技已经基于RISC-V基金会提供的标准指令集和最新指令集,形成了稳定的产品布局。“首先我们自研了基于RISC-V的高性能CPU,基于CPU去自研RISC-V高性能SoC芯片。一切都是基于市场对于RISC-V芯片的需求来布局,同时赛昉科技还会针对一些定制化应用做场景适配。” 在11月30日由中国RISC-V产业联盟和芯原微电子主办的第二届滴水湖中国RISC-V产业论坛上,上海赛昉科技有限公司资深产品总监赵晶说到。

上海赛昉科技有限公司资深产品总监 赵晶

为了推动RISC-V生态发展,赛昉科技还基于高性能SoC芯片开发了一系列RISC-V单板计算机。个人爱好者、对RISC-V感兴趣或心存疑虑的开发者,都可以利用这些单板计算机进行评估、以及软件和应用的开发。“赛昉科技会提供芯片的SDK以及完整的社区(RVspace)供大家进行讨论。基于内核、芯片、开发板,我们已经形成了整套能够反馈给社区和RISC-V生态的软件生态。”赵晶说到。

从芯片产品的规划路线来看,赛昉科技在2022年8月份发布的JH7110芯片已经正式量产,预计明年会有十万片以上的销量。今天发布的惊鸿8100芯片,是面向于高性能运算的智能视觉处理SoC平台,是赛昉科技最高性能的SoC,也是是全球第一款适合主流笔记本/Mini-PC应用的RISC-V芯片,拥有各大主流操作系统的支持。

据介绍,惊鸿8100能够实现对数据的控制、存储、计算,具有高性能、低功耗、低成本的特点,同时具备视觉、语音系统和人工智能引擎,适用于开发板、工控交换机、教育及入门笔记本电脑等终端产品。

同时赵晶表示,赛昉会根据自家RISC-V芯片CPU性能的提高,来规划下一代更高性能和更多应用场景的惊鸿系列芯片。

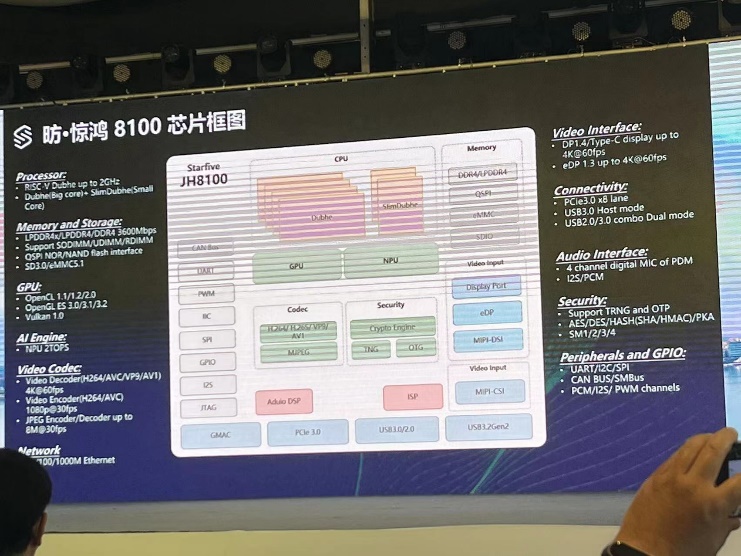

关于本次发布的新品昉·惊鸿8100的性能,主要包括以下几点。

首先,采用赛昉自主可控高性能RISC-V天枢CPU。其次,采用了12nm制程,在低功耗方面提供保障。在多媒体方面,可以支持H.264/265、VP9、AV1解码能力。同时为了适应笔记本和PC应用场景,也提供了包括USB3.0/2.0x4、PCIe3.0 x8等更加丰富和灵活的扩展性接口。人工智能方面,拥有2TOPS AI算力,支持TensorFlow等主流架构。

从惊鸿8100的芯片框图可以看到,CPU采用“大小核”多核架构,大核频滤2GHz,小核1.5GHz。除了高速接口之外,芯片还集成了Aduio和自研算法,包括AES、DES和一些国际通用算法,还满足国密的加密算法,可部署在国产可控和自主替代的一些应用场景。据悉,赛昉惊鸿8100还集成了芯原的IP。

惊鸿8100天枢处理器内核采用的64位超高性能设计,12级流水线,超标量、深度乱序执行,支持最新的指令集,包括:位操作扩展、用户级中断、向量扩展V1.0、虚拟化。采用台积电12nm工艺,频滤2GHz,主要对标Arm的A76。

赵晶表示,赛昉在做大小核架构时发现,这对于高性能CPU公司来说极具挑战。8100芯片继承Starlink1.0的主要目的是为了在多线程、高性能CPU处理器中做同步,“这是一个非常低功耗和低延时的总线。在当前的设计中,时延达到13.5纳秒、功耗只有0.27瓦。因此,我们会持续迭代Starlink IP。”

据悉,昉·惊鸿8100的诞生经过了详细的市场调研,主要应用市场在三个领域: IT基础设施、工业/行业领域国产化替代以及走量的消费领域,例如NAS等。

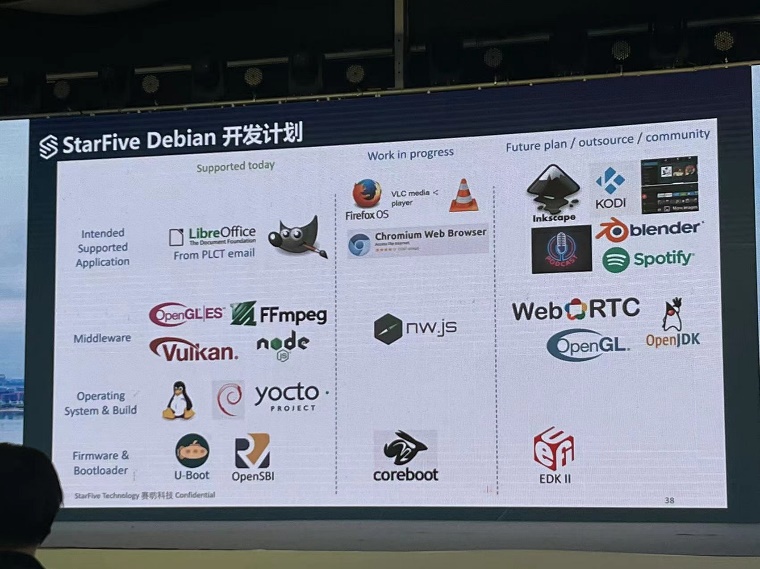

除了硬件,赛昉认为RISC-V要实现产品化最重要的下一步是软件开发。一直以来,赛昉科技秉承着自研、客户合作、开源社区开放和三方合作伙伴一起维护RISC-V生态的宗旨,除了自身持续维护Long term support和debian操作系统,也会通过开发板鼓励社区进行多种多样的Linux OS深度开发,包括OpenWRT/OperELEC等不同场景的操作应用。同时赛昉还会与合作伙伴一起进行操作系统的移植。

赵晶最后分享了赛昉科技在Debian操作系统开发上要做的工作。据悉,目前基于基于惊鸿7110已经完成了Debian系统多媒体中间键的开发,下一步主要工作是基于这些中间键和驱动适配主要应用,例如针对浏览器、Office等应用做更好的适配。