当前集成电路设计日益复杂,系统级、场景级验证需求不断增加,创新成本及设计周期压力骤增。在这样的背景下,作为集成电路设计工具的EDA,不仅仅局限在满足功能验证需求,也更多参与到设计、架构、软硬协同、功耗等方方面面的优化探索中,在系统级创新及芯片敏捷开发中扮演更重要的角色。因此集成电路产业创新发展,日益呼唤更加敏捷高效的验证服务。

“面对急剧增加的设计规模与成本,系统芯片在设计过程中除了供应链方面的挑战,也在设计周期、复杂的软硬件算法、架构设计等维度面临非常多的创新障碍跟门槛。芯片验证在整个开发周期中该如何赋能创新,是新时代EDA亟需解决的挑战。芯华章提出的敏捷验证,能够贯穿从验证到测试的完整闭环,从而加速系统设计与架构创新,从整体上降低芯片开发的成本、风险和难度。”2022年11月10日,在AspenCore主办的国际集成电路展览会暨研讨会(IIC Shenzhen 2022)同期的全球CEO峰会上,芯华章科技首席市场战略官谢仲辉谈到。

芯华章科技首席市场战略官谢仲辉先生

过去这十年,SpaceX 作为太空开发创新者,创造了太多航天领域的历史,从过去的好几年发射一次火箭,到现在SpaceX平均每一周都可以发射一些火箭,在大大降低发射成本的同时,也极大地提升了发射效率,在架构创新上达到了火箭回收的开发目的。如今的SpaceX技术已处于世界领先地位,在整个产品开发过程中有哪些创新路径能给半导体开发提供借鉴呢?

谢仲辉认为,SpaceX的成功,很大程度上归功于其引入了很多新的敏捷开发手段。

譬如SpaceX一方面使用商用芯片,用更主流的材料来降低开发成本;另一方面还大量引用软件开发里的敏捷开发手段,通过非传统的工业软件开发环境,采用更公开且主流的软件开发环境,比如Linux,从而引进更多相关人才参与,并透过建模,不断迭代测试,监测、收集和覆盖分析手段,不断降低测试成本,加速开发的周期,达到如今能够在短短十年间就做到了火箭回收的最终目的。

其实,集成电路行业对于敏捷开发的探索也早已经开始了。从70年代温斯顿·罗伊斯(Winston Royce)提出的文档驱动的瀑布开发模型,再到现在测试驱动的敏捷开发模型,敏捷开发方法逐渐发展,其核心在于更快、更多、更好地迭代,以更早的集成、测试、交付来发现问题和调整产品。

文档驱动的瀑布开发模型,在产品每个周期从开发到上市是一环接一环,按顺序地开发指导上市,这种开发模式的系统需求明确,有清晰的阶段规划且交付标准高。不过潜在问题在早期无法被发现,开发周期相对很长,对一些市场的要求和架构变化、需求没办法及时响应。

到了90年代,测试驱动的敏捷开发模型进入眼帘。这种增量式设计交付时间短,所以需求跟架构就可以快速调整。持续集成、持续测试也能尽早把潜在的问题曝露出来,因此测试驱动的敏捷开发模型,在快速发展的市场驱动芯片需求中被大量采用。

不过这样的开发模式对验证及测试的团队以及成本要求相对很高。在典型的芯片设计流程中,从算法和架构探索、性能验证、模块设计、物理设计,每个阶段都会发现很多不能在单个阶段可以完全解决、完全发现的问题。这非常符合敏捷开发需要解决的问题场景。虽然目前有部分敏捷开发手段已经赋能在芯片开发周期中,然而其中占了芯片设计很大一个环节的验证模块并没有得到很好的解决,所以必须要有更完善的验证手段,进一步降低成本,并提高验证效率。

“众所周知,芯片验证在一个典型SoC项目中占了大约7成以上的投入,因为目前的芯片验证已经不仅仅要满足功能正确性,还必须要包括架构探索、性能验证甚至功耗系统级验证等等问题。除了在开发周期中要确保功能正确,达到流片标准,验证也已经覆盖到量产测试阶段,赋能系统从设计到量产的端到端全链条创新。”谢仲辉认为。

基于上面的挑战,EDA也在很多方面进行自我革新。

作为被主流验证团队大量使用的工具,目前动态仿真、逻辑仿真已经非常成熟,但它所消耗的时间也非常长。业界因此提出如果能更多结合形式化验证的工具,以数学建模的方式,可以更完备、更快速迭代芯片验证,也能够提升自动化跟智能化验证水平,加快迭代的速度。

然而,传统的形式化验证工具获得大范围应用也面临一些现实的挑战。比如其不能支持大模块的设计要求。伴随技术创新,这并非是不能解决的问题。如果能透过底层架构创新,借助更智能化的调度器、更多的求解器以及并行化的云部署,就可以大大增加算力跟收敛的速度,解决相关的问题。

另一方面,如果工具间的底层数据框架能够统一,比如在数据覆盖率方面、在调试方面,也可以避免重复验证、重复覆盖的问题,加快收敛的效率。

“EDA领域需要不断创新,以满足复杂的系统级应用需求。通过在底层核心算法及框架上做进一步的优化,我们就能够更加善用目前云算力的优势做计算规模化,提高验证效率。进一步来讲,如果底层软件框架能够无缝支持异构计算,比如CPU、GPU异构,甚至NPU的异构,我们就能进一步提高算力,赋能自动化及智能化迭代。”谢仲辉表示。

这样的创新并非远在天边,很多设想已经付诸实践。

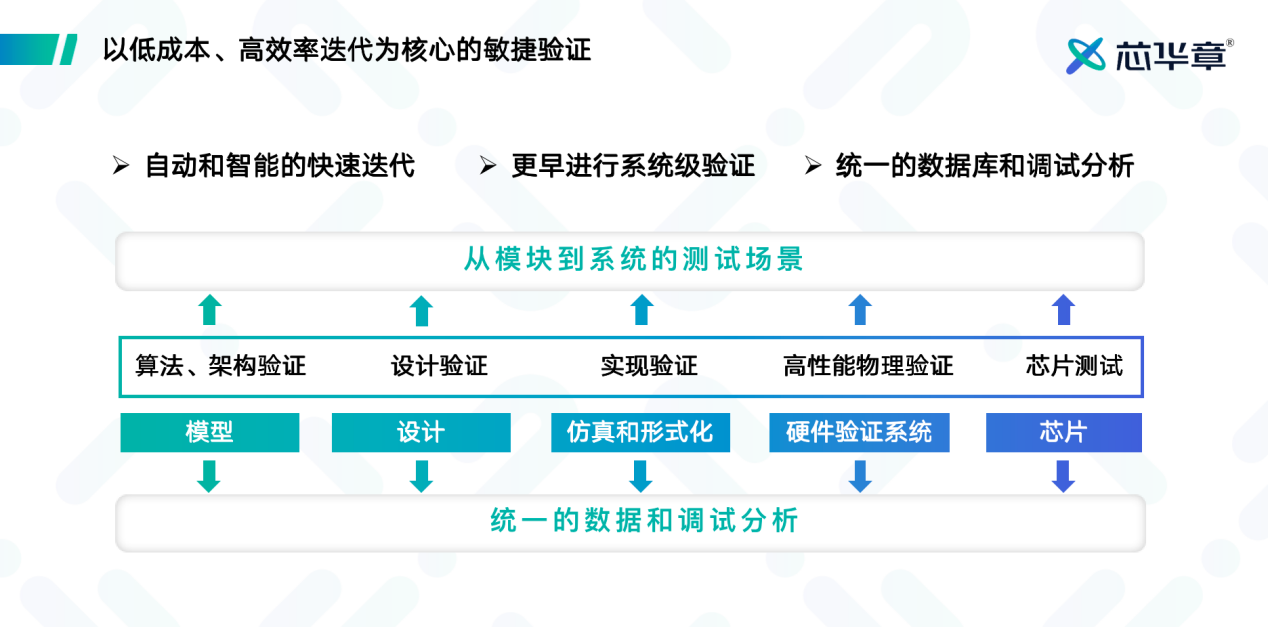

“我们需要更快、更好、更低成本的验证测试方法学、工具,来满足当前系统级创新的复杂需求。作为敏捷开发的基础,敏捷验证就是要解决这方面的重要环节。作为系统级验证EDA解决方案提供商,芯华章希望通过跟供应链伙伴密切合作,解决敏捷开发中的敏捷验证环节的主要问题,能够以低成本在各个芯片验证与测试环境中,进行自动化和智能化的快速迭代,并提早进行系统级验证,透过统一的数据库和高效的调试分析,进行验证与测试目标的高效收敛。”谢仲辉表示,“基于敏捷验证的开发理念,芯华章以终为始,打造了统一底层架构的智V验证平台,通过创新融合的技术底座和协同的验证工具,以自动化、智能化快速迭代为目标,致力于提早让用户进行系统级验证,通过统一的数据库及系统调试分析手段形成闭环,赋能敏捷验证,让系统公司能够加快系统架构创新及产品上市速度。”

EDA工具作为集成电路设计链的皇冠,一直是少数玩家的领域。其中作为本土企业,芯华章的发展令人瞩目。目前,芯华章已发布智V验证平台与5款自研数字验证工具,基本建立了完整的数字验证全流程服务,大大提高了验证效率与方案的易用性,并获得数十家产业一线用户实际项目部署应用。

在IIC Shenzhen 2022同期举办的“全球电子成就奖”上,芯华章凭借系统级验证EDA领域出色的产品力及技术创新表现,一举斩获双料大奖——芯华章董事长兼CEO王礼宾与Intel中国总经理张瑞同获“年度创新人物”,统一底层技术框架的智V验证平台获颁“年度EDA产品奖”。

关于芯华章科技

芯华章聚集全球EDA行业精英和尖端科技领域人才,以智能调试、智能编译、智能验证座舱、智能云原生等技术支柱,构建芯华章平台底座,提供全面覆盖数字芯片验证需求的七大产品系列,包括:硬件仿真系统、FPGA原型验证系统、智能场景验证、形式验证、逻辑仿真、系统调试以及验证云,为合作伙伴提供自主研发、安全可靠的芯片产业解决方案与专家级顾问服务。同时,芯华章致力于面向未来的EDA 2.0智能化电子设计平台的研究与开发,以技术革新加速电子系统创新效率,让芯片设计更简单、更普惠。

目前,芯华章在北京、上海、南京、深圳、厦门、成都等地都建立了研发中心,集结了一支400余人的全球化精英团队,其中八成为尖端研发人员,硕博比例高达80%,已取得专利授权31件,发布5款具备自主知识产权的数字验证产品,基本建立了完整的数字验证全流程服务,并得到中科院半导体所、燧原科技、芯来、鲲云等几十家业内知名企业实际项目采用,为中国集成电路产业腾飞提供了重要的支撑和保障。