IIC国际集成电路展览会暨研讨会于2022年8月16-17日如期在南京国际博览中心开幕。此次峰会汇集年度创新产品展示、技术交流、高端论坛、产业峰会及前沿科技探讨等众多内容。借此机会,杭州行芯科技有限公司董事长兼总经理贺青先生接受了特邀采访,贺先生就EDA产业现状发表了见解,阐述了先进工艺对EDA的挑战以及解决方案,分享了公司平台技术及未来发展战略。

贺青先生(行芯)接受视频专访

杭州行芯科技有限公司(简称行芯)与芯同行,是一家具有完全自主知识产权和国际竞争力的EDA企业,拥有顶尖的团队和核心技术,致力于行业领先的Signoff工具链开发。

行芯荣获年度创新EAD公司颁奖现场

作为国内先进工艺EDA工具链的创新代表,行芯凭借在FinFET先进工艺上的突破与创新,荣膺“年度创新EDA公司”奖项。

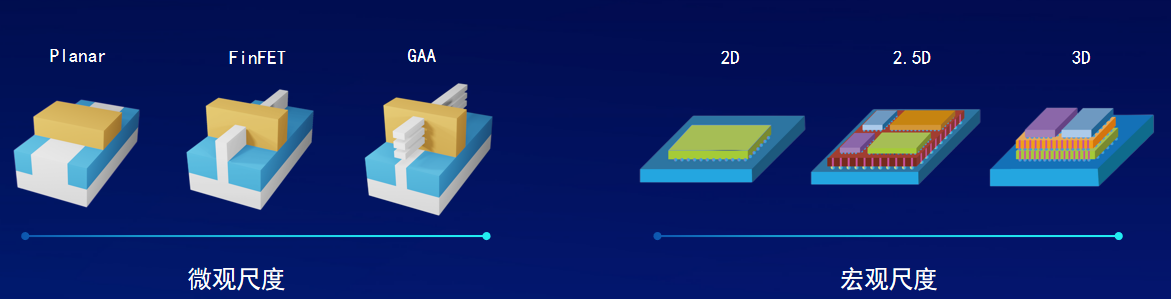

在先进工艺节点下,芯片设计从微观尺度到宏观尺度全面进入三维世界,传统的二维建模方式无法精确模拟三维结构,设计人员还需要面对大量的复杂工艺效应、先进封装、电路规模持续增长、PPA极致要求等重重挑战,导致签核无法按时完成。贺青强调,行芯通过底层EDA技术创新,业界首次实现将二维与三维结构进行高精度统一建模,并利用人工智能辅助的交互式建模技术和支持超大容量的弹性计算架构,提速芯片设计签核验证流程,并在Foundry端成功通过硅精度数据验证。

先进工艺的发展状态及面临的挑战

贺青博士一直深耕于EDA行业,研究底层技术原理逻辑,专注于工具链的开发,对行业有透彻的观察。贺总首先谈到“先进工艺”状况,先进工艺不单指工艺技术由16nm、10nm、7nm、5nm至3nm摩尔式的发展,同时也包括芯片设计从2D进入3D的转变。虽然先进工艺的延伸对材料、制程工艺、工具和方法提出了挑战,但从设计企业的发展状况来看,起步虽晚但发展几十年且极大受益于fab厂的支持,迭代速度紧跟国际发展步伐,整体而言,这方面发展并不落后。相反,由于严格的技术壁垒,EDA在先进工艺方面发展速度较慢,表现为产业链上相对薄弱的一面,受到了行业高度关注和重视。

芯片设计从2D进入3D世界

芯片设计全面进入3D世界,在平面工艺向先进工艺的演进过程中带来了一系列挑战,具体表现为:

三维复杂结构带来的工艺建模挑战:在三维结构中,工艺建模方式发生了变化,传统的二维建模方法无法满足三维工艺的需求和发展,同时不同FAB之间的建模方式也存在较大差异;2. 晶体管微缩带来大量复杂工艺效应的挑战:三维工艺伴随而来的新技术涉及多重曝光、工艺抖动、众多电解质和刻蚀负载效应等;3.三维集成带来的挑战:三维集成涉及多种工艺和架构的混合,电、电磁、热、力等的耦合,多维度海量数据的交互呈指数型变化,这都给三维集成带来不少挑战;4. 规模持续增长带来的挑战:电路规模的增长表现为晶体管及RC参数规模的持续增长,后端仿真的规模以几何式增长导致仿真无法完成;计算稳定性、一致性和新型计算架构对EDA算力带来规模挑战;5. 功耗-性能-成本的极致挑战。

行芯在先进工艺方面的创新

面对先进工艺带来的种种设计挑战,行芯利用底层EDA技术创新,主要通过精度、效率和容量三个维度来加速先进工艺的设计收敛:

二维与三维结构高精度统一建模:与硅数据高度吻合的物理验证与优化工作均依赖于对工艺结构的高精度模拟,是保证芯片设计收敛的基石。行芯在业界首次实现将二维与三维结构进行高精度统一建模,并先后完成3D验证、晶体管级验证和门级验证;

人工智能辅助快速工艺建模和工艺文件生成:AI辅助的交互式建模技术大幅降低先进工艺的建模难度,弥补工程师技术能力短板,实时修正模型,整体工作将效率提升6倍以上;

各层级超大容量设计:弹性计算架构可支撑数百万晶体管、数亿门电路、上百亿门系统等设计。

行芯EDA工具链_Signoff平台

行芯专注于SoC、ASIC、Memory、Custom、AMS等芯片物理设计Signoff领域,包括寄生参数提取、电源完整性、信号完整性、功耗分析、时序分析、片上多物理域分析、先进工艺设计优化等,行芯提供的关键技术可应用于整个物理设计过程和签核过程。

EDA工具链Signoff平台主要有GloryEX全芯片参数提权、GloryBolt全芯片电源可靠性、GloryPower全芯片功耗性能优化和PhyBolt芯片级多物理域耦合等。

行芯展望

行芯于今年2月完成超亿元B轮融资,在谈到未来发展战略时,贺总表示,行芯需要和生态链上的伙伴深度合作,共同挖掘产品规律,积极开展前沿探索,实现EDA行业的快速发展和持续技术迭代与创新,打造一个硅精度、智能化、大容量和平台化的EDA解决方案。

EDA企业不能满足于单纯的产品替代,而是需要具有较强的产品输出能力和技术引领能力。贺总表示,行芯会持续丰富产品线,为系统厂商及半导体设计者提供端到端一体化服务,用创新的Signoff技术促进芯片设计制造的协同与创新,赋能集成电路产业发展。