电子工程专辑讯,近日据集邦咨询调查,英特尔原计划将Meteor Lake当中tGPU芯片组外包给台积电代工的3nm产能,因产品设计和工艺验证问题拖延至2023年上半年,近期量产时间再度拖延至2023年底,使得2023年原计划预定的3nm产能近乎全部取消,投片量产仅剩少量进行工程验证。

集邦咨询表示,此举在很大程度冲击了台积电的扩产计划,造成3nm工艺自2022年下半年到2023年首波客户只有苹果,产品包含M系列芯片和A17 Bionic。台积电已经决定放缓扩产进展,来确保产能不能过度闲置造成巨大的成本摊提压力,除了正式通知设备供货商调整2023年设备订单外,由于3nm扩产成本高昂将影响部分2023年资本支出规划。但是在苹果3nm产品放量的情况下,台积电全年的营收也会比2022年有所增长,只是增长幅度会放缓些,对台积电来说会降低3nm量产初期对毛利稀释的程度。

不过台积电的其他客户,比如AMD、联发科、高通等都已经陆续规划2024年量产3nm产品,再加上2024年苹果的iPhone新机预计全面导入3nm工艺处理器,也将增进台积电3nm在2024年的产能利用率和营收表现。

集邦咨询还认为,英特尔自身Intel 4工艺发展状况及其伴随的委外状况仍为台积电重要的潜在成长动能,倘若Intel 4未能如期量产,则英特尔可能将其运算核心(computing tile)加码委外至台积电,也将强势带动台积电2024年成长规模,相反地,倘若Intel制程发展顺利,则选择自行制造相关产品而取消台积电订单的可能性仍然存在。

台积电对此指出,不评论个别客户业务,强调产能扩充项目按照计划进行。

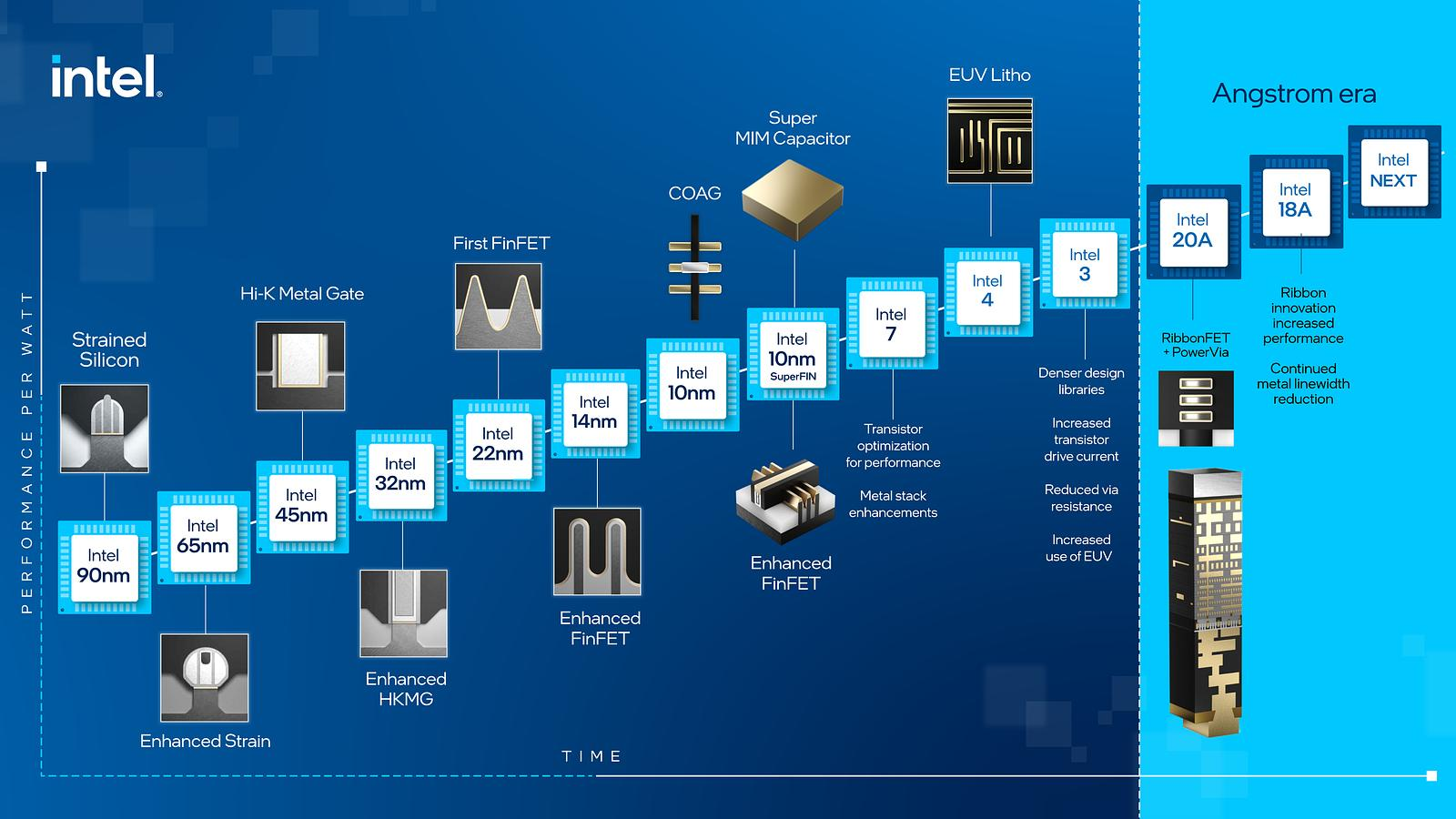

据悉,较于上一代 Intel 7,Intel 4 于相同功耗下能够提升 20% 以上的效能,高效能组件库(library cell)的密度则是 2 倍,同时达成两项关键目标:它满足开发中产品的需求,包括 PC 客户端的 Meteor Lake,并推进先进技术和工艺模块。

英特尔指出,Intel 4 于鳍片间距、接点间距以及低层金属间距等关键尺寸(Critical Dimension),持续朝向微缩的方向前行,并同时导入设计技术协同优化,缩小单一组件的尺寸。透过 FinFET 材料与结构上的改良提升效能,Intel 4 单一 N 型半导体或是 P 型半导体,其鳍片数量从 Intel 7 高效能组件库的 4 片降低至 3 片。综合上述技术,使得 Intel 4 能够大幅增加逻辑组件密度,并缩减路径延迟和降低功耗。

Intel 7 已导入自对准四重成像技术(Self-Aligned Quad Patterning、SAQP)和主动组件栅极上接点(Contact Over Active Gate、COAG)技术来提升逻辑密度。前者透过单次微影和两次沉积、蚀刻步骤,将晶圆上的微影图案缩小 4 倍,且没有多次微影层迭对准的问题;后者则是将栅极接点直接设在栅极上方,而非传统设在栅极的一侧,进而提升组件密度。Intel 4 更进一步加入网格布线方案(gridded layout scheme),简单化并规律化电路布线,提升效能同时并改善生产良率。

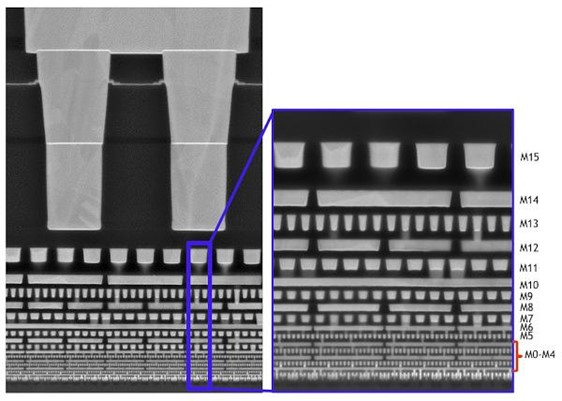

随着工艺微缩,晶体管上方的金属导线、接点也随之缩小;导线的电阻和线路直径呈现反比,该如何维持导线效能抑是需要克服的壁垒。Intel 4 采用新的金属配方称之为强化铜(Enhanced Cu),使用铜做为导线、接点的主体,取代 Intel 7 所使用的钴,外层再使用钴、钽包覆;此配方兼具铜的低电阻特性,并降低自由电子移动时撞击原子使其移位,进而让电路失效的电迁移(electromigration)现象,为 Intel 3 和未来的工艺打下基础。

将光罩图案成像至晶圆上的最重要改变,可能是在于广泛的使用 EUV 来简化工艺。英特尔在 Intel 4 的较高互连层中使用 EUV,以大幅度减少光罩数量和制程步骤。其降低制程的复杂性,亦同步替未来制程节点建立技术领先地位及设备产能。