摩尔定律“失效”了以后,先进工艺芯片何去何从?

为了应对芯片工艺挑战,目前包括三星在内的芯片厂商均从封装环节寻找突破口。近日,据韩媒Business Korea报道,三星电子挖角苹果半导体专家,担任三星美国总部封装解决方案中心理事。

目前主流的封装技术是三维集成和先进封装。随着前端工艺中电路的小型化工作已达到极限,“3D封装”或“小芯片”技术正在吸引厂商投资,三星电子也加入其中,并在2020年推出3D堆叠技术“X-Cube”。未来,三星将从先进工艺和先进封装两个层面提升自身核心竞争力。

全方位与台积电竞争

在芯片代工领域,三星与台积电是最大的竞争对手,彼此也将超越对手成为发展目标。

虽然三星代工业务比台积电晚了近20年,但其后续发展势头却十分强劲,2015-2016年间凭借逐渐成熟的代工技术抢夺了台积电不少客户,在2017年晶圆代工业务部门独立后,其市占率更是直接超过格芯和联电,稳坐全球晶圆代工第二的宝座。

2019年,三星定下来未来10年内(至2030年)超越台积电的目标。一直以来,为了实现这个目标,三星大力投资、招聘人才,除了先进制程,半导体设备和材料、IC载板、先进封装……等一切与晶圆代工有关的领域,也都成为了其瞄准的焦点。

实际上,先进封装自诞生起,就被视为撬动半导体产业继续向前的重要杠杆。其中,三维集成把晶体管堆叠起来,像3D NAND那样,从尺寸缩小转变为堆叠层数的增加。先进封装是把很多小芯片封装在一起,形成一个更大的芯片。只要封装能力在持续提升,单颗芯片里面的晶体管数量就可以持续增长,而且成本也不会显著增加。

目前台积电、英特尔、三星等大厂皆推出了自身先进封装技术。Yole Development数据显示,英特尔和台积电分别占据2022年全球先进封装领域投资的32%和27%,日月光以及三星则紧追其后,前四大厂商的资本支出合计占比高达85%。

据悉,三星在2020年8月公布了名为“X-Cube”的3D封装技术,并表示该技术已成功试产,可用于制造7nm和 5nm芯片。

持续发力先进封装

据悉,X-Cube是一种利用垂直电气连接而不是电线的封装解决方案。三星在7nm制程的测试过程中,成功利用 TSV 技术将SRAM 堆叠在逻辑芯片顶部,从而释放了空间以将更多的内存封装到更小的占位空间中。通过3D集成,超薄封装设计显著缩短了芯片之间的信号路径,从而最大程度地提高了数据传输速度和能效。

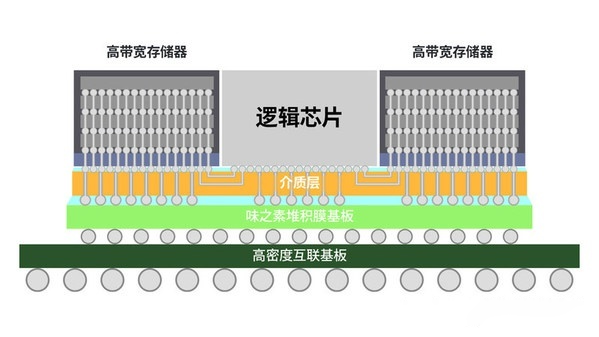

2021年5月,三星宣布下一代2.5D封装技术Interposer-Cube4(I-Cube4)即将面世,可将一个或多个Logic Chip和多个高带宽内存芯片(HBM)使用硅中介层,从而使多个芯片排列封装在一个芯片里。

到了2021年11月,三星又推出了全新2.5D封装解决方案H-Cube(Hybrid Substrate Cube,混合基板封装),专用于需要高性能和大面积封装技术的HPC、人工智能、数据中心和网络产品等领域。

图源:三星电子

三星电子透露,H-Cube技术是由三星晶圆代工厂和Amkor Technology公司联合开发,采用在高端ABF基板上叠加大面积的HDI基板的结构,通过将连接芯片和基板的焊锡球间距缩短35%,缩小ABF基板的尺寸,同时在ABF基板下添加HDI基板以确保与系统板的连接,从而进一步实现更大的2.5D封装。

不过,与台积电的“3DFabric”和英特尔的“Foveros”封装技术相比,三星的先进封装技术显然暂时无法从中获胜。

为了进一步提升自身的先进封装技术,近日三星电子在三星设备解决方案部门美国总部(DSA)设立了封装解决方案中心,并任命前苹果半导体专家Kim Woo-pyeong担任理事。

据悉,Kim Woo-pyeong毕业于韩国科学技术院(KAIST),曾任职于德州仪器和高通,从2014年开始在苹果工作,迄今已有9年。

上个月,三星电子DS部门成立半导体封装工作小组(TF),由DS部门CEO Kye Hyun Kyung直接领导。据悉,该团队由三星电子的DS部门测试与系统封装(TSP)的工程师、半导体研发中心的研究人员,以及三星内存和代工部门的专家组成,预计将提出最新的先进封装解决方案,意在加强与大型晶圆代工厂客户在封装领域的合作。

日前有消息称三星电子开始考虑对半导体封装业务加大投资,正评估一项投资计划,可能在韩国天安厂扩产。

当前全球半导体巨头之间的竞争越来越激烈,而三星也将在先进封装领域持续寻找能与竞争对手抗争甚至保持领先的方法,包括一流半导体人才的引进。