物联网、大数据和人工智能(AI)正在推动半导体行业的新一轮增长。然而,尽管对芯片创新的需求从未如此强烈,传统摩尔定律在2D缩放领域的步伐却正在放缓。

每一代芯片的缩小迭代都需要更长的时间和更高的成本。随着芯片制造商和系统公司在功效、性能、面积、成本和上市时间(应用材料公司称之为PPACt)方面不断推动改进,对新的设计和制造方式的需求也在与日俱增。

封装作用日益突出

几十年来,半导体PPACt路线图一直是通过2D平面缩小和单片半导体集成实现的,并且节奏相对比较固定。在此期间,半导体封装通常被视为该行业中低价值部分。它的主要功能是保护芯片并能够将芯片连接到印刷电路板(PCB),然后在PCB板上完成各芯片和各模块之间的电源和信号连接。

随着计算从个人电脑到移动设备的发展,又到如今的人工智能时代,封装的作用发生了巨大变化。今天,先进的封装支持异构设计和集成,它提供了一种替代方式来延续与传统摩尔定律2D缩放相关的PPACt优势。世界领先的芯片和系统公司,都在采用这种实现摩尔定律的新方法,依此作为竞争之必需。

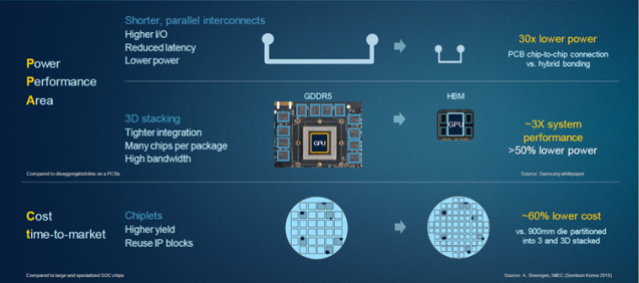

异构方法可以帮助工程师将大型设计分解为更小的小芯片(chiplet),然后在单个封装中将这些小芯片连接起来,实现PPACt改进。将小芯片组合在一起的一种方法是使用硅通孔(TSV)实现3D堆叠。类似于TSV的3D互连可以比传统布线短得多,从而有利于实现更低的功耗和更高的I/O密度。

对于目前的工艺节点,摩尔定律在2D缩放的继续正在停滞。伴随着每次的迭代,芯片缩小需要更长的时间和更高的成本。因此迫切需要新的设计生产方式。与此同时,硅光子学正在从一种专为利基市场保留的技术,成为一种可用于大批量市场的技术。下面让我们了解一下即将到来的“超越摩尔”特别项目的承诺和魅力。

例如,与传统的PCB连接的凸出引脚相比,TSV可以将I/O密度提高约100倍,并将传输每比特的能量降低约15倍,具体数值取决于架构和工作载荷,因此可以实现高能效的3D芯片堆叠。随着逻辑电路和内存靠得更近,性能还可以得到进一步提高。

成本降低有两种方式:较小的裸片通常具有较高的良率,但先进节点的晶圆通常比基于先前节点的晶圆更昂贵,这意味着工程师可以将性能关键的裸片与其他小芯片进行混合和匹配,从而实现较低的混合成本。随着经过验证的IP小芯片得到更快的整合,上市时间也可以显著缩短。

图1:异构设计和先进封装支持PPACt以多种方式得到发展。(图片来源:应用材料公司)

混合邦定即将腾飞

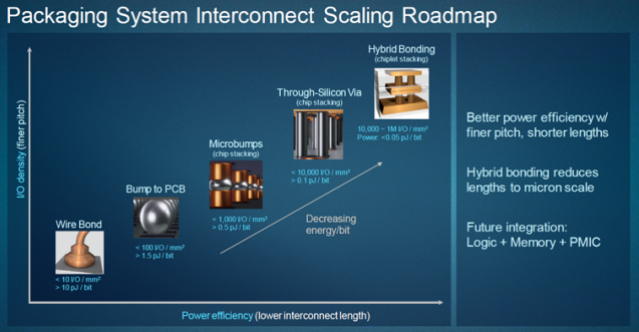

先进封装的下一场革命是混合邦定,该技术对I/O引脚使用金属端连接到基板、再通过基板布线实现芯片之间电气互连的传统多芯片封装技术进行了重大改进。混合邦定通过直接铜到铜邦定的方式来连接芯片和晶圆,因而可以缩短布线距离并进一步提高I/O密度,提升电源效率和系统性能。与TSV相比,混合邦定将使I/O密度再提高10倍,每比特能量也能再改善2倍。

图2:混合邦定是封装系统互连路线图中的下一项创举。

每项后续技术都能提供更高的输入输出密度,以及更低的每比特数据传输功耗。

实现混合邦定需要一整套先进的半导体制造技术。为了获得最佳性能,必须同时对邦定焊盘成型、平面化、表面处理和邦定等关键技术进行优化。

对于世界领先的半导体和系统公司来说,异构设计和混合邦定等先进封装技术的重要性将越来越高。应用材料公司正通过独特的产品组合广度和深度,来助力加速这一趋势。该公司新加坡封装实验室中,将这些因素结合在一起,并与客户和行业合作伙伴一起合作,展示了一套完整且经过验证的芯片到晶圆和晶圆到晶圆混合邦定的制造技术。参与这些活动的目的是建立一个先进的封装生态系统,加速客户的PPACt路线图并应对传统摩尔定律缩放的放缓。

封装和本地化

新冠疫情大流行驱动下的供应链短缺已对主要行业造成经济破坏,汽车就是一个突出的例子。许多制造商甚至国家都在重新考虑其半导体战略,并且进一步延伸到封装领域。

贸易组织IPC和研究公司TechSearch International于2021年11月发表的报告指出,北美仅占全球先进半导体封装产量的3%。这一不足可能会通过美国国会去年通过的520亿美元芯片产业补贴来弥补。该法案要求在美国国内创建一个国家先进封装制造计划,这一举措得到了包括应用材料公司在内的美国半导体行业领导者们的大力支持。

(参考原文:As Classic Moore’s Law Dims, Heterogeneous Integration Steps Into the Limelight)

本文为《电子工程专辑》2022年7月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订