电子工程专辑讯,6月30日,三星半导体发布新闻稿正式公布,三星基于3纳米(nm)全环绕栅极(Gate-All-AroundT,简称 GAA)工艺节点的芯片已经开始初步生产。

来源三星电子新闻稿截图

目前不清楚三星所谓的“开始初步生产”是处于什么阶段,究竟是试产,还是小批量或大批量生产?

针对外界对三星良率仍抱有怀疑态度,韩国芯片分析师 Greg Roh 接受《韩联社》专访时透露:“据我所知,三星 3 纳米芯片良率的提升速度远优于市场预期,而且新客户增速也相当快,三星代工业务预计将比一年前增长约 40%,高于业界整体增幅水平(25%)。”

Roh 预计:“明年初 DRAM 位成长率估计只有 11-16% ,即便经济衰退来临时,报价也会在供应紧张的情况下止稳、甚至上扬。”

早前,有外媒披露测试报告指出,三星4纳米的良率仅有35%,远远不如台积电的70%水平,三星3纳米的良率也只有10至20%左右,这让多家厂商不得不将订单转给台积电生产。

再有三星员工针对公司“内斗文化严重”发文指出,面对越来越高的技术挑战门坎,出现难以克服的情况,而员工们选择应付了事,对上、对外造假摆烂,呼吁公司如果改革企业文化,未来所有产品都可能会落后对手。

韩国中央日报、BusinessKorea报导,为求提升晶圆代工良率、留住客户,传三星替换了约20名管理层。对此三星确认人事的确有更动,但并未说明详细数字、也否认跟芯片良率问题有关。

据悉,三星现已任命副总裁Song Jai-hyuk为半导体研究中心的新负责人,三星旗下的各个业务部门也进行重组,包括内存芯片制造、代工和设备解决方案。一家投资公司的分析师表示,此次重组不寻常,但三星似乎希望找到问题的解决方案,包括能够开发出具有良率的下一代芯片。

还有业内人士表示,如果三星在基于 GAA 的 3纳米工艺中确保稳定的良率,它可以成为代工市场的游戏规则改变者。台积电预计将从 2纳米芯片开始引入 GAA 工艺,并在 2026 年左右发布第一款产品。对于三星来说,未来三年将是关键时期。

中国矿机芯片公司首发三星3纳米工艺技术

6月28日,韩国媒体TheElec援引消息人士的话报道称,三星3纳米工艺的首个客户是中国比特币挖矿用半导体厂商——上海磐矽半导体有限公司(PanSemi)。

根据天眼查发现,上海磐矽半导体有限公司成立于2016年3月,注册资本为4500万元,法定代表人为陈建兵,经营范围包括从事电子元器件的研发、销售,集成电路的研发、销售,芯片的设计、研发、销售以及系统集成等。

股权穿透后,上海磐硅半导体有限公司的实控人为香港注册公司研极科技(香港)有限公司。

目前,上海磐矽半导体有限公司官网仅有一个展示页面,称该公司总部位于上海,是一家芯片设计能力为28纳米、16纳米和10纳米的高科技初创公司,专注于数字加密货币和Al应用的专用芯片设计。企查查显示,该公司核心团队只有陈建兵1人,参保人数也仅有3人。

三星方面对此并没有披露任何信息。

早前台积电的5纳米客户也是由中国的比特大陆首发。吴忌寒曾经在比特大陆主办的法兰克福矿业大会上透露,2020年一季度5纳米将开始量产,3纳米芯片的研发也正在路上,即便是2纳米和1纳米的芯片也已排上日程。

比特大陆2019年下半年给台积电下的订单大概在5万片,包括16纳米和7纳米芯片,可以出产约60万台矿机。

三星3纳米芯片:对比5纳米,面积减少16%,功耗降低45%

由于半导体芯片和智能手机销售强劲,三星 2022 年第一季获利成长 50.3%,创下自 2018 年以来高点,当季净利高达约 89 亿美元,不过,三星警示,新冠疫情、乌俄战争以及供应链限制等不确定性因素之下,可能对公司 2022 年剩余时间的销售和获利带来影响。

据TrendForce 近期调查显示,台积电今年第一季以 53.5% 的全球代工市占率位居第一,三星以 16.3% 位居第二,远远落后台积电。

三星计划通过抢先发布3纳米工艺来进一步抢占晶圆代工市场。

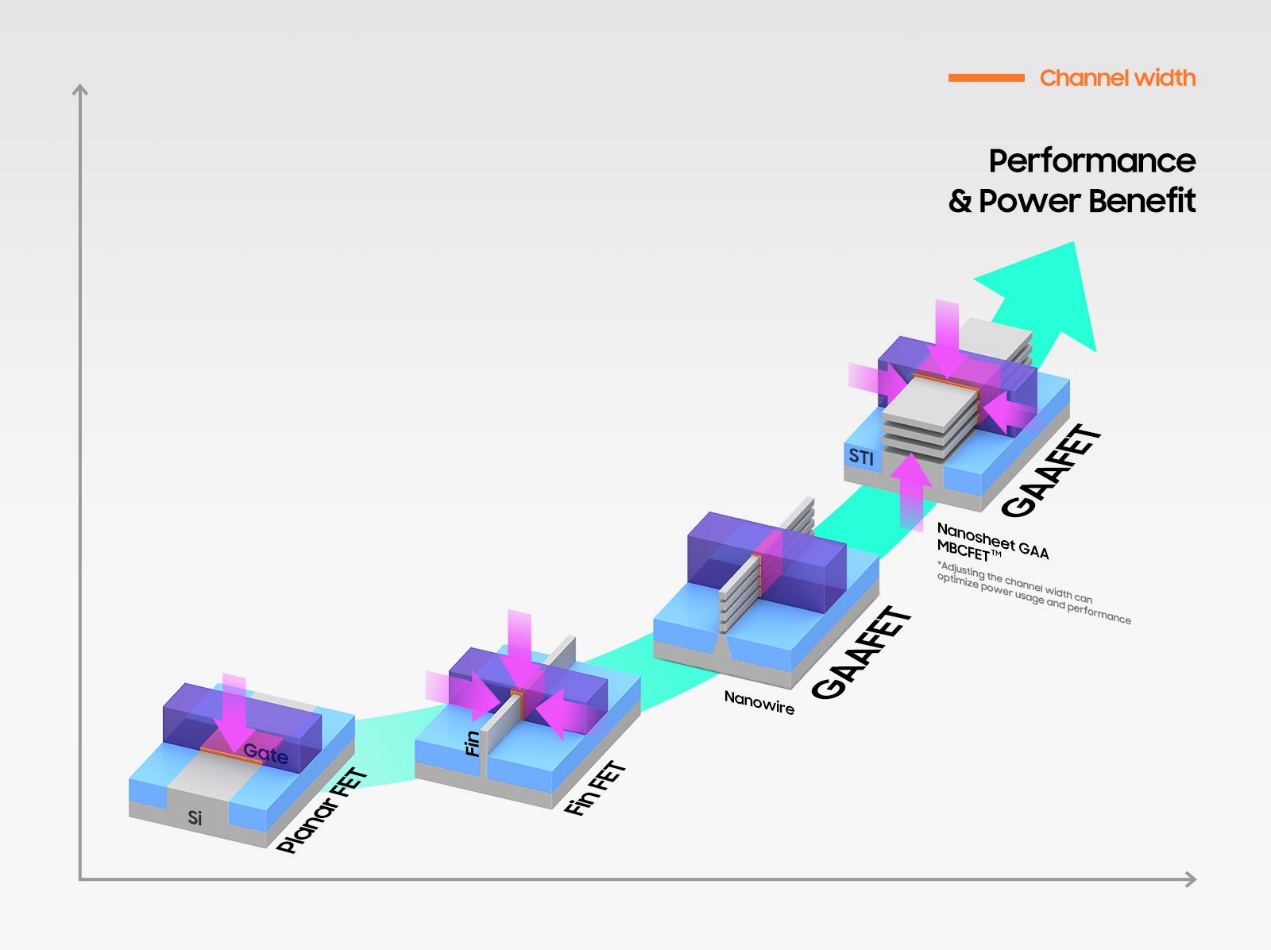

三星电子表示,三星首次实现GAA“多桥-通道场效应晶体管”(简称: MBCFET™ Multi-Bridge-Channel FET)应用打破了FinFET技术的性能限制,通过降低工作电压水平来提高能耗比,同时还通过增加驱动电流增强芯片性能。三星首先将纳米片晶体管应用于高性能、低功耗计算领域的半导体芯片,并计划将其扩大至移动处理器领域。

三星电子总裁兼代工业务负责人Siyoung Choi博士表示:“一直以来,三星电子不断将新一代工艺技术应用于生产制造中。例如:三星的第一个High-K Metal Gate (HKMG) 工艺、FinFET 以及 EUV等。三星希望通过首次采用3nm工艺的“多桥-通道场效应晶体管”( MBCFET™),将继续保持半导体行业前沿地位。同时,三星将继续在竞争性技术开发方面积极创新,并建立有助于加速实现技术成熟的流程“。

来源三星电子官网图片

据悉,3纳米GAA 技术采用了宽通道的纳米片,与采用窄通道纳米线的GAA 技术相比能提供更高的性能和能耗比。3纳米GAA 技术上, 三星能够调整纳米晶体管的通道宽度,优化功耗和性能,从而能够满足客户的多元需求。此外,GAA 的设计灵活性对设计技术协同优化(DTCO)非常有利,有助于实现更高的性能、更低的功耗和更小的面积优势。与5纳米工艺相比,第一代3纳米工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而第二代3纳米工艺则使功耗降低50%,性能提升30%,芯片面积减少 35%。

台积电3/2纳米工艺技术最新进展

台积电在2022年北美技术论坛上,表示3纳米预计于今年下半年量产,并将搭配TSMC FINFLEX架构。其中,TSMC FINFLEX架构提供多样化的标准组件选择,包括3-2鳍结构支持超高效能、2-1鳍结构支持最佳功耗效率与晶体管密度、2-2鳍结构则是支持平衡两者的高效效能,能协助客户完成符合其需求的系统单芯片设计,各功能区块采用最优化的鳍结构,支持所需的效能、功耗与面积,同时整合至相同的芯片上。

同时,台积电还正式发表2纳米工艺将采用纳米片晶体管架构,全面提升效能及功耗效率。

据台积电分享的数据,2纳米采用纳米片晶体管架构,在相同功耗下指令周期增加10到15%;若相同速度下,功耗亦可降低25到30%;预计2025年开始量产。台积电宣称,这将使效能及功耗效率提升一个时代,通过协助客户实现下一代产品的创新,除了移动运算的基本版本,2纳米技术平台也会涵盖高效能版本及完备的小芯片整合解决方案。

当工艺缩小,空间越来越小,鳍的数量也会随之减少,持续提升驱动电流会更困难;而纳米片架构,就是其中一个被提出讨论的解方。纳米片架构将垂直的鳍转为水平,透过垂直堆栈纳米片,实现更大的有效导电通道宽度;再者,栅极360度接触信道的结构,让导电信道被高介电系数的金属栅极围绕,可实现更佳的栅极信道控制,并缩短信道长度。

布局2纳米,三星动作频频

三星晶圆代工业务总裁暨负责人表示,三星正进入高速成长期,将持续在下一代的制造技术上,保持领先姿态。不过该公司目前仍拒绝透露客户名单。

虽然在3纳米暂居领先,不过三星并未暂停布局脚步。

三星于去年底宣布,预计于美国德州斥资170亿美元设立新厂,生产移动设备、5G、高效能运算和AI(人工智能)等先进芯片,预计2023年上半年动工,2024 下半年投产。

上个月,三星电子副会长李在镕(Lee Jae-yong)以及执行长庆显桂(Kyung Kye-hyun)也造访了ASML高层和荷兰总理Mark Rutte,讨论关于关键设备极紫外光设备(EUV)的供应。三星声明称,EUV微影设备对于下一代半导体生产工艺不可或缺,但并未透露ASML将供应的额外EUV微影设备细节。

三星表示,李在镕要求Rutte提供支持,确保ASML能稳定供应EUV微影设备。

本文参考自巨亨网、韩国中央日报、BusinessKorea、三星半导体等报道