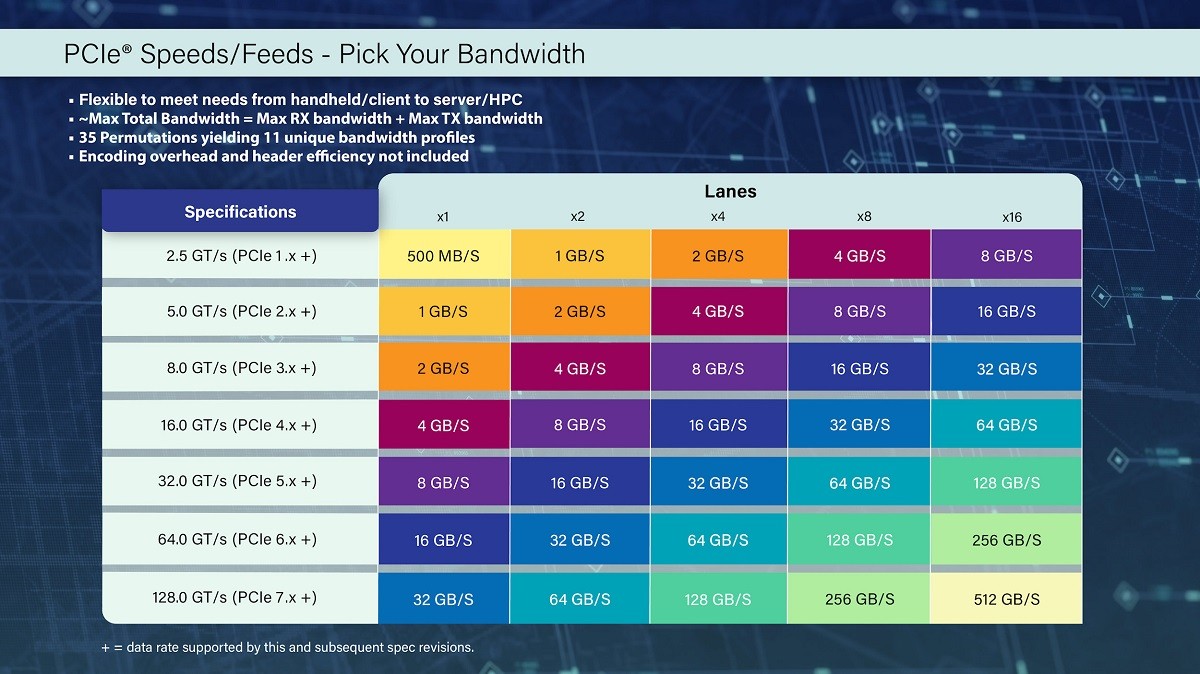

电子工程专辑讯,近日,在加利福尼亚州举行的最新的PCI-SIG 开发者大会上,负责制定 PCE Express(PCIe)规范的 PCI-SIG 工作组公布了下一代 PCI Express 7(PCIe 7.0)将于 2025 年发布。PCIe 每一代的数据速率和带宽都会翻倍,这代表 PCIe 7.0 可以提供高达 128GT/s 的最大数据速率,以及通过 x16 设定提供高达 512GB/s 的双向传输带宽。

对于 PCIe 7.0 部分,PCI-SIG 组织锁定在 800 Gig 以太网、人工智能、机器学习(AI / ML)、高性能计算(HPC)、量子计算以及超大规模数据中心和云端等领域。

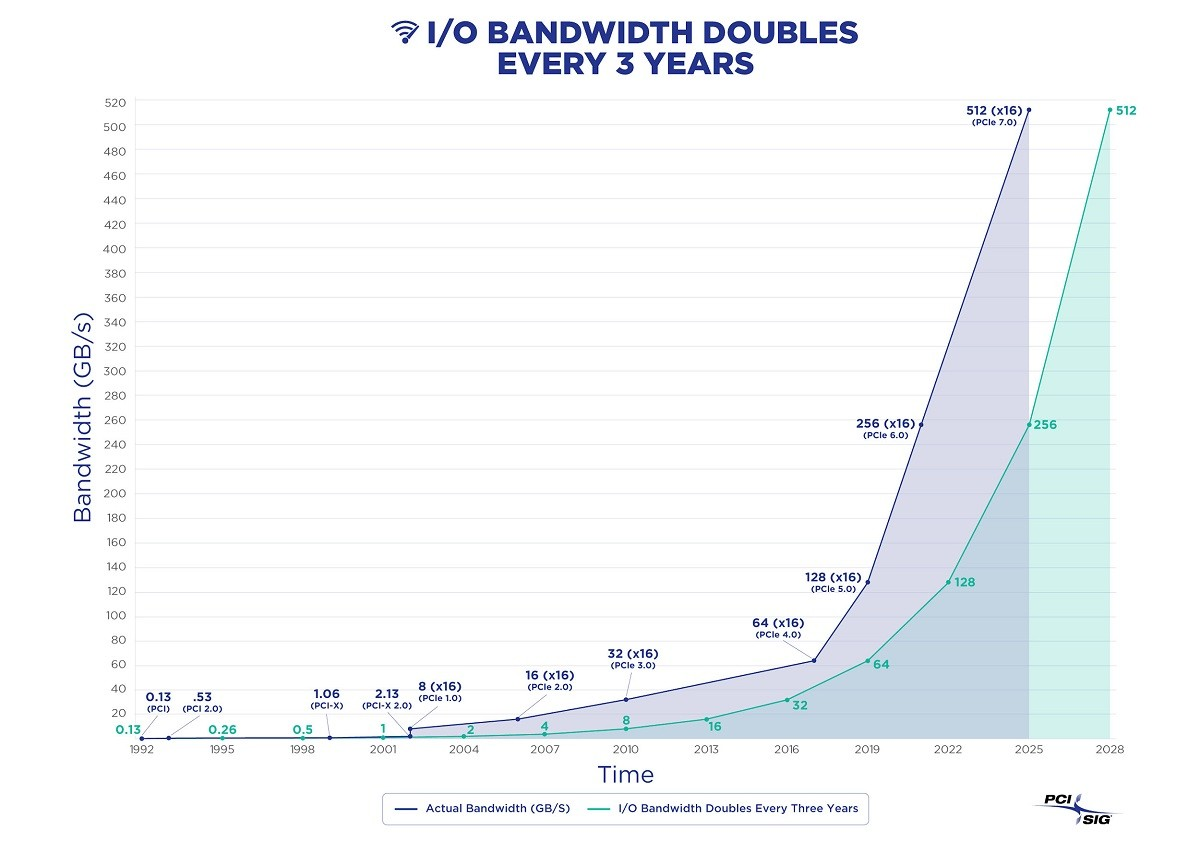

PCI-SIG 的原定目标是每三年将传输速度加倍,但目前是在进度超前大约 3 年的状态,原定要 2028 年才会达到双 512GB/s 的带宽,2025 年就能实现了。

不过从规范推出到厂家实际应用在产品上,还是会有一定时间的延迟。比如PCIe 5.0 规范在 2019 年就推出,而今年才正要开始普及;PCIe 6.0 规范则是在今年一月推出,搭载的产品恐怕要再两三年后才会见到。PCIe 7.0 自然也是相同的。

PCI-SIG是谁?

今天, 大多数的计算机依然遵循冯·诺依曼体系结构,其基本特点是软硬件分离,通过存储器保存程序(指令和数据),计算机由五个部分组成(运算器、控制器、存储器、输入设备、输出设备)。冯·诺依曼计算机体系结构的存储程序方式造成了系统对存储器的依赖,CPU访问存储器的速度制约了系统运行的速度。

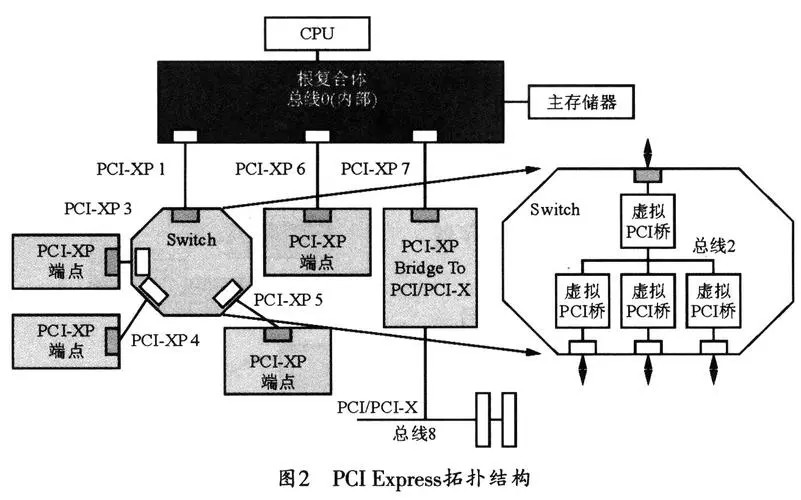

将计算机各个部分组织在一起,就有了总线的的概念。系统总线是连接计算机系统主要组件(比如CPU、输入设备、输出设备)的单一计算机总线。它结合了数据总线的功能来承载信息,地址总线的功能来确定应该从哪里发送或读取信息,以及控制总线的功能来确定其信息。

自从 IBM 兼容 PC 问世以来,PC 上已经先后出现过多种总线类型了,包括早期的 ISA、VESA 到 PCI 再到 PCI、PCI-X,还有针对显卡的 AGP等,这些总线各有千秋。每种接口使用的电压都不同,并不能兼容,要解决这种情况就只能推出一个大一统的新标准取代这些落伍的总线,这就是 PCI-E 总线的由来。

自1991 年下半年,Intel 公司首先提出了PCI 的概念,并联合IBM、Compaq、AST、HP、DEC 等100 多家公司成立了PCI 集团。

PCI-SIG英文全称为:Peripheral Component Interconnect Special Interest Group(外围部件互连专业组),简称PCISIG。

该组织拥有并管理着开放式行业标准——PCI规范。随着行业的I/O需求的发展,该组织负责定义和实现新的行业标准I/O(输入/输出)规范。目前,全球共有900多家业界领先公司成为了PCI-SIG成员。

在2001年的春季英特尔开发者论坛(IDF)上Intel公布取代PCI总线的第三代I/O技术,被称为“3GIO”。该总线的规范由Intel支持的AWG(Arapahoe Work Group)负责制定。2002年4月17日,AWG正式宣布3GIO 1.0规范草稿制定完毕,移交PCI特殊兴趣组织(PCI-SIG)进行审核,2002年7月23日经过审核后正式公布,改名为“PCI Express”。

PCI Express发展时间

在2003年,PCIe 1.0a标准正式发布。早期标准PCIe 1.0a的数据速率为每通道250MB/秒,总速率为2.5GT/秒(千兆/秒)。与其他串行总线一样,性能通常以每秒传输数来衡量,因此不会将额外的位计为“数据”。PCIe 1.0a 使用了 8b / 10b 编码方案,因此只有 80% 的传输位是实际的“数据”。附加位有两个主要功能。首先,串行接口确保始终有足够的时钟转换来恢复时钟。它保证没有净直流电流。

之后,对标准进行了定期升级。由于 PCIe 主要用于基于 Intel 处理器的 PC 和服务器的,实际上新标准在 Intel 发布使用 PCIe 的处理器后生效。

在2006年,发布PCIe 2.0, 又把预计到2007年才实现的“带宽×2”提前了。

2010 年推出的 PCIe 3.0 已更改为更高效的 128b / 130b 编码方案,并添加了已知的二进制多项式加扰功能以平衡了0和1的时钟恢复,没有直流偏置。此外,传输速度也有明显提升。16 通道 PCIe 3.0 接口的最大传输速率为 15.7 GB/秒。

据公开信息了解,PCIe 3.0 是移动设备中部署最广泛的 PCIe 版本。例如,Google TPU 版本 3 使用 PCIe 3.0,以及 USB4 标准是基于 PCIe 3.0。这听起来可能有点令人震惊,但 PCIe 被批准为标准后,花了将近十年的时间才成为主流。这有点像信用卡问题:商店不愿意接受繁琐的信用卡付款,直到许多人拥有信用卡,人们才愿意接受信用卡付款。

作为PCIe 3.0的下一代,PCIe 4.0直到2017年才姗姗来迟。这回仅过了2年,PCIe 5.0在2019年发布了——成为PCIe历史上间隔最短的一次升级。

在2022年1月,PCIe 6.0正式发布。PCIe 5.0和6.0发布时的带宽都已经是预言的同期值的2倍。

从PCIe 2.0到PCIe 3.0发布的期间,是虚拟机云计算需求的崛起的时代。PCIe 3.0到PCIe 4.0发布之间,应用领域主要在大数据、深度学习和低功耗需求的时代。

这些大数据、深度学习、移动设备和物联网应用对于I/O基础架构的需求主要归结于:更高的吞吐量和更低的功耗。

从存储来看,早期基于SATA/SAS接口、AHCI协议的NAND SSD暴露出接口带宽可扩展性的局限和软件栈冗长的问题。自从2011发布了基于PCIe 3.0的NVMe 1.0规范,SSD的性能(带宽和IOPS)获得了充分的释放。之后的7年,SSD的发展就聚焦到了可管理性、可维护性、内部传输效率、单位成本,而接口带宽暂时不成为瓶颈。这些从每一到两年就发布升级的NVMe规范的内容可以看出可管理性、节能等方面的内容是重点。这个时期SSD性能的提升主要得益于NAND Flash介质的逐步升级而非(对外的)接口带宽。

多年之后,随着NAND SSD的控制器和介质发展到新的阶段,PCIe 3.0提供的带宽才被视为 SSD的性能瓶颈。

每一代 PCIe 的性能都会更好,但这不仅仅是数据表中的数字,它还可以实现更强大的应用程序。

随着如今数据的爆炸性的增长,各应用端也对市场提出了更多全新的技术和需求。一方面,数据量越来越大,人工智能、机器学习的使用率日益提升,带来内存和I/O接口、带宽、性能需求;另一方面,随着数据加速向云迁移,联网设备日益增加,边缘计算持续增长,带来了对数据安全重视度的提升。

此外,智能汽车的自动驾驶、辅助驾驶对数据处理的带宽和时延、数据的安全性,视不同等级也对技术提出了不同的要求。

作为数据传输和计算系统中的核心总线标准,PCIe也从最初的1.0时代,历经多次PC架构的演化, 走到如今的7.0时代, 为“5G+AIoT”数据传输标准。

2022年6月29日,全球领先的专业电子机构媒体AspenCore将与深圳市新一代信息通信产业集群联合主办【2022国际AIoT生态发展大会】,同期将举办智慧可穿戴、工业互联网、智慧家庭、智慧机器人、智慧两轮车等多场分论坛,多家企业将在论坛现场探讨AIOT领域的前景机遇。 【一键报名】现场与行业资深人士交流与互动!点击这里了解大会详情。

本文参考自LoveIC、数码硬件、维基百科等报道

- GT/s 不知道是哪个SB弄的这单位