这段时间,存储器市场受关注程度高涨。不仅是因为知名分析机构近期都相继给出存储器产品的市场数据(以及有深圳昇维旭“加入DRAM玩家群”这类新闻),还在于存储器甚至开始应用于AI计算——很快我们将发布一篇文章,相对深入地剖析存内计算(in-memory computing)技术。

就半导体市场来看,存储器行业晃一晃,整个半导体市场就要跟着颤三颤。所以我们在Gartner的半导体市场预测报告里就看到,全行业趋势预测有包含存储器和不包含存储器两份数据,就是因为存储器在半导体行业中的价值之大。此前我们撰写过一篇,是对中科院刘明院士的主题演讲总结。

最近TechInsights也发布了一篇题为2022 and Beyond for Memory Technology的技术资料,大致总结了当前DRAM、NAND存储技术的现状、发展趋势和挑战——这也算是他们的周期性更新报告项目了;对当代存储技术在商业市场的应用有更全方位的解析。我们借此从技术层面来看看如今的存储技术发展到了何种程度,期望可作为爱好者或从业人员技术细节深挖的概览。

存储器在发展上,和逻辑器件还是有很大差别,但这一领域你来我往的技术竞争也相当激烈,上至数据中心服务器,下到各类嵌入式设备。AIoT智能物联网终端对于存储器的需求未来也将是海量的。

2022年6月29日,全球领先的专业电子机构媒体AspenCore将与深圳市新一代信息通信产业集群联合主办【2022国际AIoT生态发展大会】,同期将举办工业互联网、智慧家庭、智慧机器人、智慧可穿戴、智慧两轮车等多场分论坛,多家企业将在论坛现场探讨AIOT领域的前景机遇。 【一键报名】现场与行业资深人士交流与互动!点击这里了解大会详情。

DRAM单元还在变小,虽然幅度没那么大了

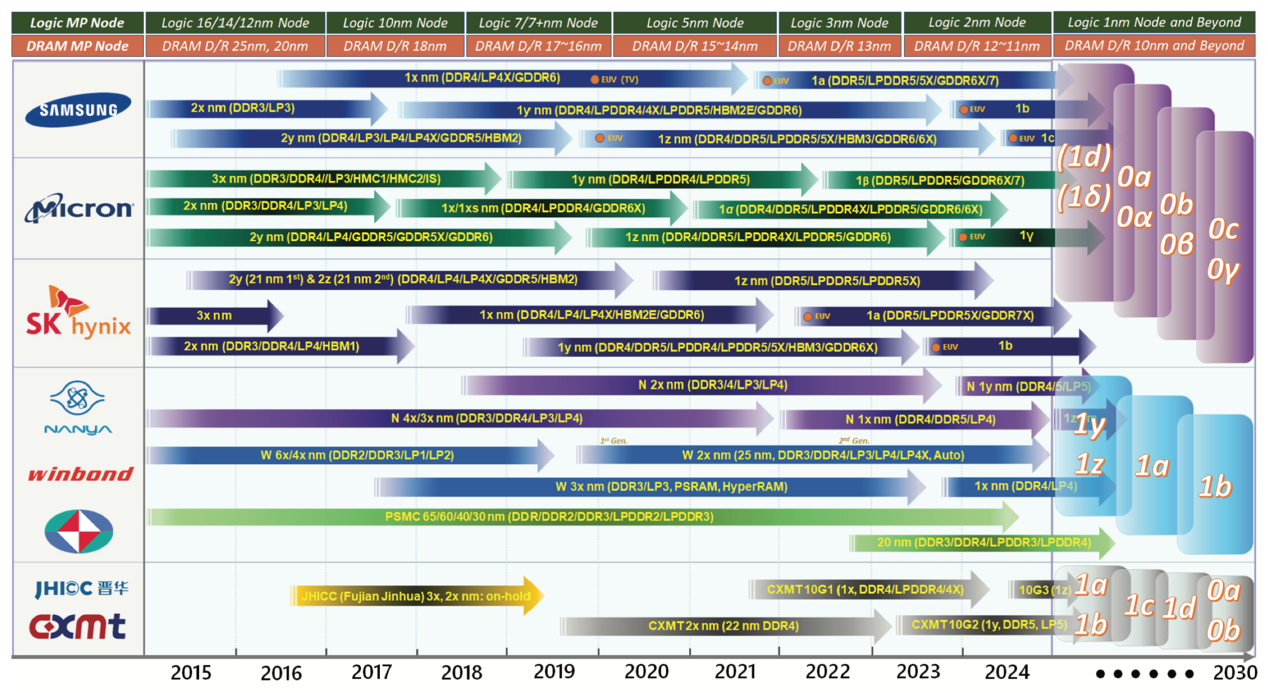

DRAM市场的几大参与者包括了三星、美光、SK海力士(SK Hynix),另外再加上南亚科技(Nanya)、力积电(PSMC)和长鑫存储(CXMT)等。下面这张图展示了该领域主要市场参与者的技术演进方向。长鑫存储(D1y)加入到前列竞争中应当也是众所周知的了。

来源:TechInsights

三星、美光与SK海力士面向DDR4、DDR5和LPDDR5应用,已经以15nm和14nm级别的单元设计规则(D/R)发布了D1z和D1α节点的产品。三星是最早在DRAM上采用EUV极紫外光的供应商,将其应用于D1x DDR4 DRAM模组和D1z LPDDR5规模量产。

美光和SK海力士在D1z节点上还在用基于ArF-i的双重曝光,虽说部分分析师评价三星提前在这一领域布局EUV技术是过于激进的。这张图同时也给出了2024年之后的一些DRAM工艺节点,包括D1d、D0a、D0b等。

来源:TechInsights

从存储单元(cell)来看,众所周知目前6F²的设计已经是主流,单元由1T+1C(1晶体管+1电容)构成——这种DRAM单元结构将在未来几代产品上延续。不过目前已经有厂商在开发4F²单元结构,仅1T或者说capacitorless的方案,作为DRAM技术未来发展的备选。

从单元晶体管与电容结构和材料的角度来看(图中的Cell TR & Cell Cap.),TechInsights在介绍中说,Bulky-fin(S-Fin)加上B-RCAT(Buried-Recessed-Channel-Array Transistor)结构的单元晶体管已经开始应用;用于buried wordline gate(埋入式字线栅)的材料,则已经从单钨层发展成了多晶硅/钨双功函数(work-function)层,做到栅极漏电的有效控制。美光在D1z和D1α节点用的是氮化锡(TiN)栅(gate)。

DRAM单元电容方面,SK海力士的D1y和D1z,以及三星D1z采用一种所谓的quasi-pillar电容(one-sided pillar capacitor)结构,而非主流的圆管式结构。

10nm级别及以下的DRAM单元设计,有新的工艺、材料和电路技术,包括前文提到的high-NA高数值孔径的EUV应用,1T DRAM单元,单元pillar电容,更高介电常数high-k的电容电介质,以及low-k ILD/IMD(层间介电层)材料。撰写这份报告的Jeongdong Choe博士表示,从近未来的节点演进来看,10nm会成为6F² DRAM单元的最后一代节点,延续到2027-2028年左右。

而DRAM单元持续缩小,未来将要面临的技术挑战包括了3D DRAM、row-hammer比特翻转问题变得更严重、低功耗设计、低延迟、新型功函数材料、HKMG(高介电常数金属栅)晶体管、片上ECC等。这份报告中特别提到了DRAM foundry厂对于速度(speed)和感测容限(sensing margin)的追求。三星应用于DDR5和GDDR6的HKMG外围晶体管技术是提升位线(BL)感测容限和速度的典型代表。

在DRAM单元尺寸缩减趋势预测上,TechInsights最近还专门撰写了一篇文章(DRAM Scaling Trend and Beyond),有兴趣的可作参考。另外值得一提的是,TechInsights也提到3D DRAM、HBM3、GDDR6X/7和嵌入式DRAM技术都将延续DRAM的寿命,扩展其应用。

3D NAND还在往上叠

3D NAND是现在我们谈到NAND时会提及的热门。不过还是有不少应用对于可靠性、高低温环境有要求,它们还是会用平面结构NAND,而且多半是SLC、MLC介质,而不会用复杂度相对更高的TLC或QLC。医疗、机器人、可穿戴、安防摄像头、机顶盒等各种IoT设备还是要用2D NAND。

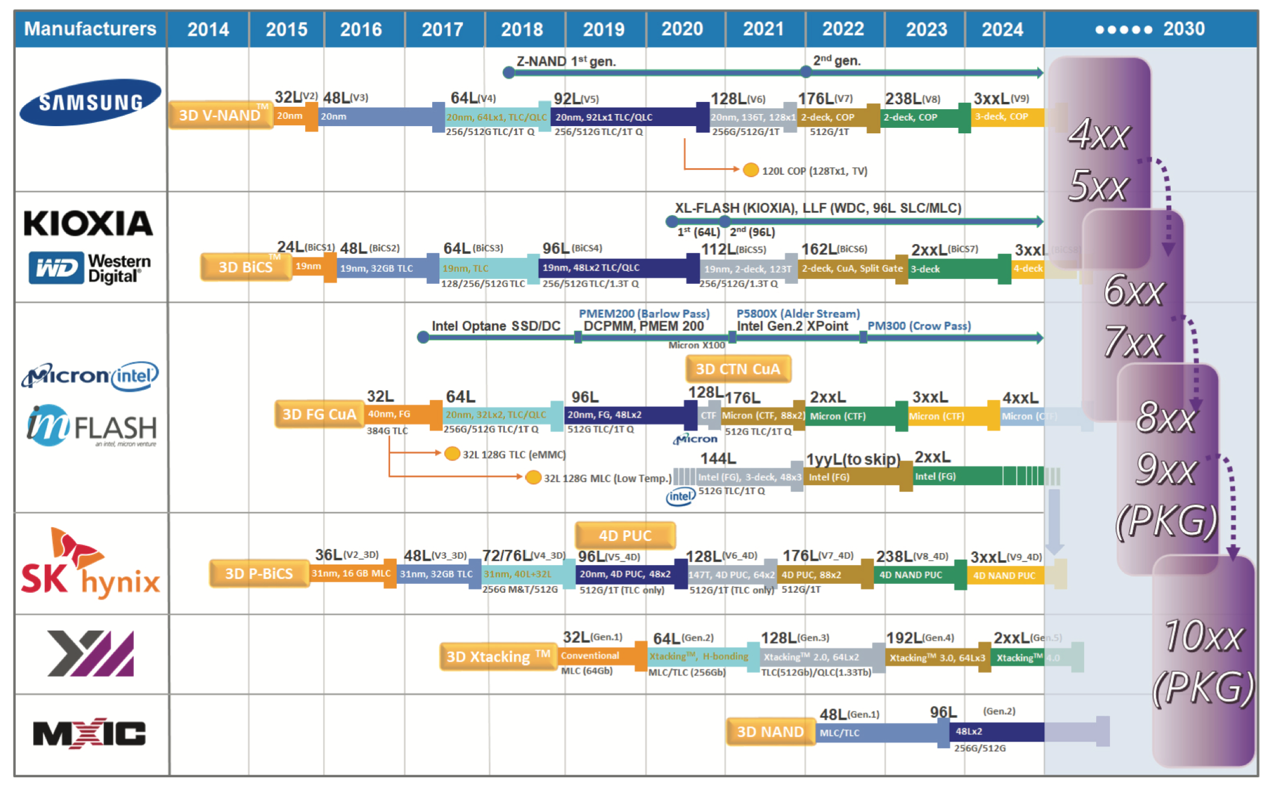

而3D NAND多见于数据中心、智能手机、PC等应用。垂直方向堆叠3D NAND层数的确是现在NAND芯片制造商竞赛的主要方向。主要的一些市场参与者的技术进展历史如下图所示:

当前进展为三星176层(V7)、铠侠/西数162层(BiCS6)、美光176层(2nd CTF)、SK海力士176层(V7),还有长江存储的128层Xtacking TLC和QLC产品;另外宏旺(MXIC)也宣布了48层的3D NAND原型产品,预计今年晚些时间或2023年进入规模量产。

主要的一些创新型技术和设计,比如3层deck结构,CuA(CMOS-under-array,美光)、COP(Cell Over Peri,三星)、PUC(Periphery Under Cell,SK海力士)结构技术,以及采用H-bonding键合的Xtacking die。其他创新技术热点还有诸如三星Z-NAND、铠侠XL-NAND这类低延迟高速NAND产品,也已经商用。

未来如果NAND向着超过500层堆叠迈进,其演进方向应当不局限在die堆叠上,还要考虑3D封装解决方案的协助。

具体说,三星V-NAND应用了一种单VC垂直蚀刻工艺,堆了最多128层(V6);其他所有的3D NAND产品则采用多deck的string集成(存储单元沿bitline位线串联起来构成一个string);比如Intel的144层,3-deck,上中下各48层。这些技术都是20nm或19nm位线half-pitch,也就是说3D NAND主要是基于ArF-i和双重曝光工艺。

堆叠的gate数量越多,垂直NAND的string高度也就在增加。比如176层的NAND string高度是12μm。追求高叠层的本质当然就在于单位面积内存储密度的提升,并伴随存储相同容量数据的成本降低。QLC die目前能做到15Gb/mm²的密度;每纵列NAND string的gate总数也增加到200个或更多。

TechInsights此前给出过长江存储Xtacking的分析(YMTC 128L Xtacking 2.0 for SSD, 也是Jeongdong Choe博士写的;不过相关报告似乎已经开始收费了),有兴趣的读者可以搜索看看。

总得来说,3D NAND的一些技术挑战集中在越来越高的深宽比(high aspect ratio)、层间应力控制、晶圆翘曲、工艺不一致性、原子层沉积与蚀刻(ALD/ALE)的控制、deck到deck的对齐问题、NAND string电流、3D封装解决方案、良率控制;还有闪存颗粒指标方面的,比如擦写速度、数据保持(retention)、电子泄露干扰之类的问题。基于技术发展,据说单个单元存储5bit数据的PLC 3D NAND几年内也会问世。

新型存储器的技术趋势与挑战

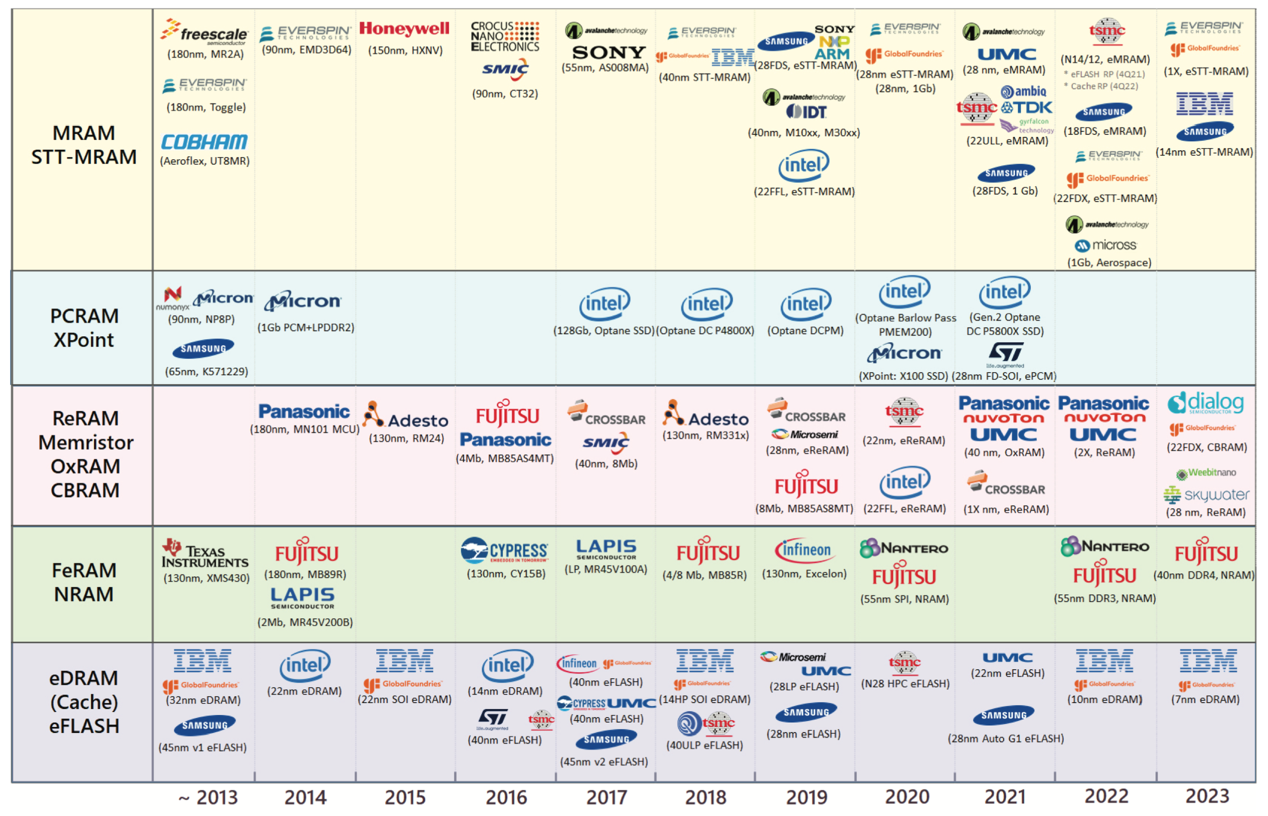

TechInsights笔下的新型存储器主要包含了MRAM(STT-MRAM)、XPoint、ReRAM、FeRAM、PCRAM/Xpoint等。某些新型存储器介质和材料本身也有更多元的应用,比如说ReRAM可能会成为存内计算的未来,MRAM可用作CPU的die内cache,XPoint应用于SCM存储级内存等。

STT-MRAM当前的发展似乎很不错,参与这项技术研发的企业和机构当前已经囊括了Everspin、GlobalFoundries、Avalanche、索尼、美光、Imec、CEA-LETI、美国应用材料、三星、富士通、IBM、台积电、Spin Transfer Technologies等。

TechInsights在这份报告中给出了较多MRAM赛道参与者的产品技术。比如说Ambiq公司的Apollo Blue系列MCU在台积电22ULL工艺的支持下携有eMRAM。而GlobalFoundries基于22nm FDSOI的eMRAM,应用在了GreenWave的AI处理器上。以及材料和工艺技术上各家的一些差异,比如Avalanche MRAM还在用旧的多晶硅栅和L型spacer间隔层,Everspin则往high-k栅极介电层(gate dielectrics)加入了镧;三星和台积电的MRAM栅极结构有gate-first HKMG和gate-last HKMG工艺之分等等。

其他新型存储器技术方面,富士通的8Mb ReRAM是全球密度最高、单独量产的ReRAM产品;基于45nm CMOS工艺,相比此前旧工艺的4Mb ReRAM产品有了相当大的存储密度提升和die size的缩减。XPoint技术的知名市场参与者自然就是Intel了,第二代XPoint存储器已经应用到了市场上,4堆栈的PCM/OTS层结构。

新型存储器件发展的基础就在于更出色的性能或效率——性能除了速度之外也包括数据保持时间、寿命之类的指标。只不过“新型”未大规模普及的原因无非在于成本还没能像传统器件那样降下来,尤其新型材料造成工艺兼容性方面的一些挑战。3D NAND显然在单位成本内的容量方面仍然有着无与伦比的优势。

谈了这么多尖端存储技术发展现状和未来相关的内容,更海量存储器产品的一个落脚点还在于AIoT产品方面。2022年6月29日,全球领先的专业电子机构媒体AspenCore将与深圳市新一代信息通信产业集群联合主办【2022国际AIoT生态发展大会】,同期将举办工业互联网、智慧家庭、智慧机器人、智慧可穿戴、智慧两轮车等多场分论坛,多家企业将在论坛现场探讨AIOT领域的前景机遇。 【一键报名】现场与行业资深人士交流与互动!点击这里了解大会详情。