电子工程专辑讯,近日韩国媒体Businesskorea报道,有消息传出三星(Samsung Electronics) 3 nm工艺因良率远低于目标,造成延后量产时间的消息。对此,三星的一位发言人通过电话向媒体表示,否认 3 nm工艺延后量产的报导,并指出三星仍按照计划于第二季开始量产 3 nm工艺。

3 nm环栅 (GAA) 是下一代工艺技术,它能以更小的体积实现更好的功耗表现,可将芯片面积减少多达 45%,同时性能提高 30%,功耗降低 50%。

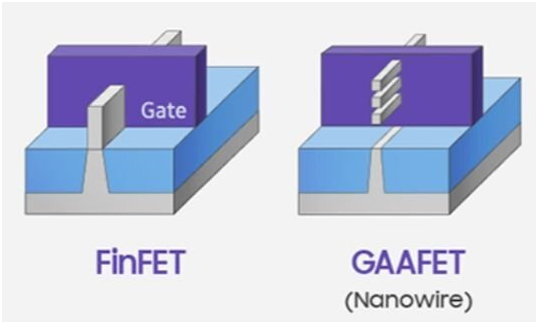

图注:在环栅结构中(右),一个栅极包围了圆柱形沟道的整个四个侧面,这是电流流动的通道,而在鳍式场效应晶体管(FinFET)结构中,一个栅极覆盖了三个侧面, GAA结构可以更精确地控制电流。

GAA 工艺技术有望为芯片行业带来另一次重大设计转折,它改进了半导体晶体管的结构,使栅极可以接触晶体管的所有四个侧面,而不是当前 FinFET 工艺中的三个侧面。GAA结构可以比FinFET工艺更精确地控制电流。

三星和台积电在提高 3nm 工艺良率方面均存在困难。三星晶圆已投入 3 nm工艺中试量产,但由于良率低的问题,该公司一直推迟正式量产公告。

台积电原本计划从 7 月开始为英特尔和苹果公司量产采用 3 nm工艺的半导体,但难以确保所需的良率。NVIDIA 向台积电支付了高达 90 亿美元的预付款,采用 3 nm工艺用于生产将于今年内发布的 GeForce RTX40 GPU 系列,但将收到 5 nm产品而不是 3 nm产品。据中国台湾 DigiTimes 报道称,台积电难以确保 3 nm工艺的预期良率,因此多次修改其技术路线图。

三星3nm量产冲刺,赶超台积电

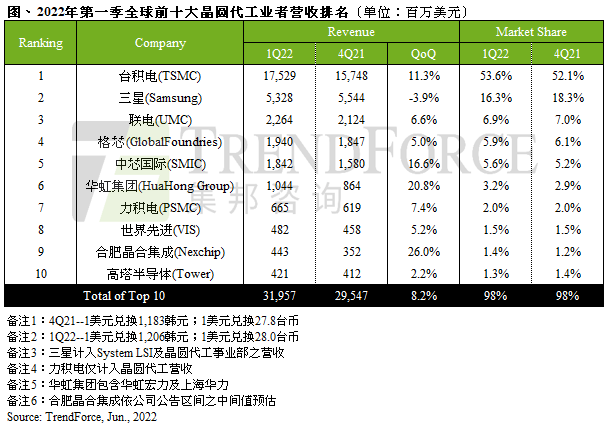

根据 TrendForce 最新调查显示,台积电今年第一季以 53.5% 的全球代工市占率位居第一,三星以 16.3% 位居第二,远远落后台积电。

从市占率来看,目前台积电还是远远超过三星。三星电子和台积电都在生产基于 FinFEt 技术的 5 nm芯片。据Businesskorea援引专家表示,台积电在良率和性能方面占据上风。

三星为赶超台积电,取得领先地位,将工艺技术押宝在GAA 技术上。三星今年将 GAA 技术率先使用在 3 nm的工艺上,并计划 2025 年量产 2 nm工艺。台积电计划继续将 FinFET 技术应用于 3 nm工艺,并从 2 nm工艺开始引入 GAA 技术。

如果事情按照三星的计划进行,三星将成为世界上第一家大规模生产采用 GAA 技术的3 nm半导体代工厂。

现代汽车证券研究主管 Roh Keun-chang 表示:“除非三星电子为其 7 nm或更先进的工艺获得足够的客户,否则它可能会加剧投资者对三星电子未来业绩的焦虑。”

有业内人士表示,如果三星在基于 GAA 的 3 nm工艺中确保稳定的良率,它可以成为代工市场的游戏规则改变者。台积电预计将从 2nm 芯片开始引入 GAA 工艺,并在 2026 年左右发布第一款产品。对于三星来说,未来三年将是关键时期。

本文参考自Businesskorea、TrendForce等报道