日前据韩媒 BusinessKorea 报道,韩国进出口银行海外经济研究所(OERI)表示,今年中国的 DRAM 制造商长鑫存储正在推动第二代 10nm 级(1γ 或 16 nm至 17 nm)DRAM 的大规模生产。另一方面,三星电子和 SK 海力士正计划在今年年底或明年大规模生产第五代 10nm 级(1β或 12 nm至 13 nm)DRAM。

所以OERI认为:

考虑到每一代DRAM技术差距约为两年到两年半,两国的技术差距超过五年。

不过据日媒TECH+消息,华为即将在6月13日至17日在夏威夷举办的集成电路领域顶级会议VLSI Symposium2022上以演讲的形式介绍论文,公布其与中科院微电子研究所合作开发的最新3D DRAM技术。(EETC编按:VLSI全称为Very-large-scale integration,中文可以理解为“超大规模集成电路技术与电路研讨会”)。

HBM开启DRAM 3D化

动态随机存取存储器(DRAM)是一种易失性的、基于电容的、破坏性读取形式的存储器。自1966年被IBM研究中心的Robert H. Dennard发明至今,DRAM已经经过了数十年的发展,并成为存储器市场最大的细分领域,占据了58%的存储器市场规模。

长期以来,DRAM存储单元由单个晶体管和单个电容器制成,即所谓的 1T1C (1 Transistor -1 Capacitor)设计。这种存储单元在写入时打开晶体管,电荷被推入电容器 (1) 或从电容器 (0) 去除;读取时则会提取并度量电荷。这种传统系统速度超级快,价格便宜,并且功耗很小,但它的挑战是如何在不增加功耗的情况下,满足人们不断增长的对高容量、高性能、大带宽、低延迟、小存储单元尺寸的需求。

受限于传统计算器体系的冯-诺依曼架构,存储器带宽与计算需求之间的存储墙问题日益突出,HBM(High Bandwidth Memory,高带宽存储器)的出现是DRAM从2D架构转向3D架构的突破,它是非平面类型,具有立方体/长方体形式的 3D 形状。存储芯片堆叠形成立方体结构,占用空间更小、功耗更低、带宽更高,因此可以放置在 GPU 附近取代传统GDDR。

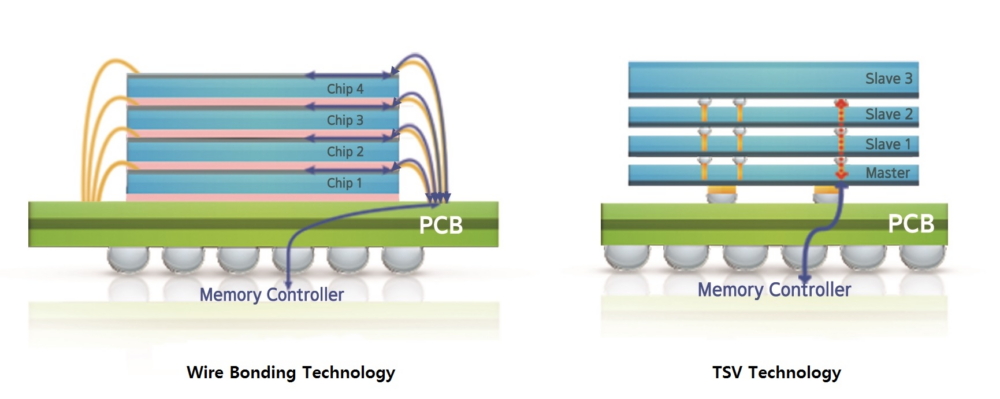

HBM使用TSV(Through Silicon Via,硅穿孔)技术将数个DRAM芯片堆叠起来。凭借TSV方式,HBM大幅提高了容量和数据传输速率。与传统内存技术相比,HBM具有更高带宽、更多I/O数量、更低功耗、更小尺寸,可应用于高性能计算(HPC)、超级计算机、大型数据中心、AI、云计算等领域。

利用TSV技术开发的3D DRAM技术,与之前堆叠的概念不同,后者是通过Wire Bonding将多个Chip堆叠在一起产生的

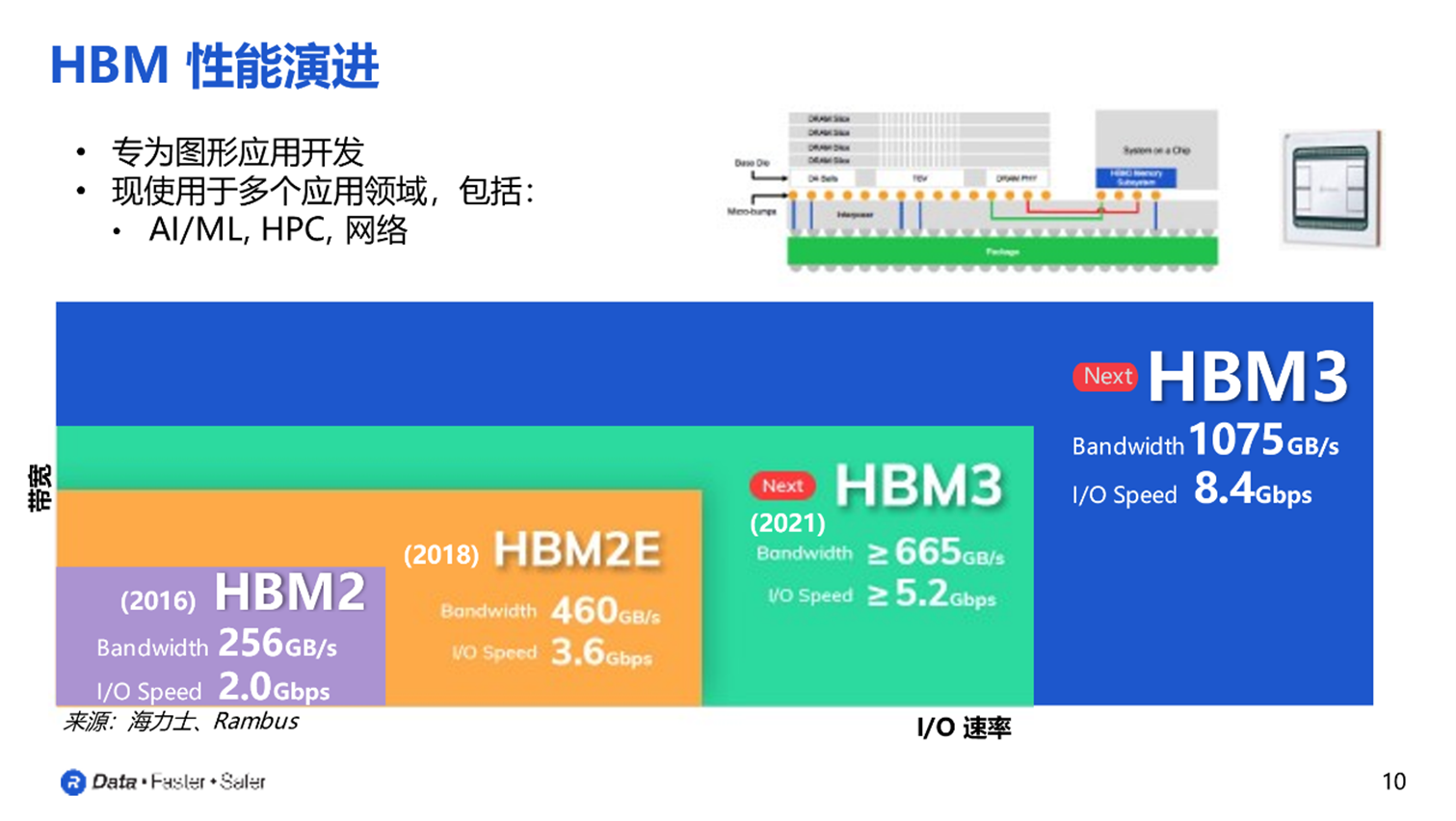

2014年,AMD和SK海力士宣布携手开发HBM,开启了DRAM 3D化发展道路。随后三星、SK海力士、美光等存储巨头也展开了升级竞赛,NVIDIA、Synopsys、Rambus等企业也在布局当中。经过HBM、HBM2、HBM2E以及HBM3几代更迭,目前,HBM内存技术已成功升级到HBM3标准(第四代HBM)。

HBM性能演进(图自:Rambus)

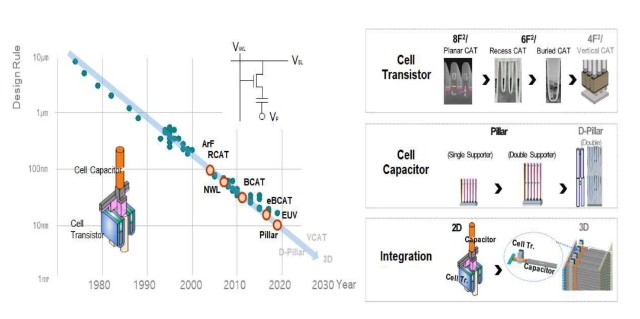

据介绍,随着极紫外光(EUV)技术在 DRAM 中的应用,下一个挑战是缩小存储单元。三星预计很快将投入两层电容器,预计在本世纪后期将转向垂直存取晶体管,随后是 3D DRAM。ASM、应用材料和东京电子等半导体设备公司的演示文稿以及本演示文稿中也频繁提及3D DRAM的结构,这表明该行业正在寻求解决方案。

三星DRAM 路线图 (图自:三星)

无电容技术也是3D DRAM的有力竞争者

除了HBM外,研究者们也开始在无电容技术方面下功夫,有Dynamic Flash Memory、VLT技术、Z-RAM等技术出现。

在2020 IEDM(International ElectronDevices Meeting)上,imec首次展示无电容DRAM并掀起热议。当时这款DRAM包括两个IGZO-TFTs并且没有存储电容,而这种2T0C (2 Transistor -0 Capacitor) DRAM架构还有望克服经典1T1C DRAM 密度缩放的关键障碍,即小单元中 Si 晶体管的大截止电流尺寸,以及存储电容器消耗的大面积。但在“概念性”演示中,IGZO TFT 并未针对最大保留率进行优化,并且缺少对耐久性(即故障前的读/写循环次数)的评估。

美国和比利时的独立研究小组IMEC在2021 IEDM 上又展示了一款全新的无电容器 DRAM,这种新型的DRAM基于铟镓锌氧(IGZO,indium-gallium-zinc-oxide),在去年的基础上进行了改进,保留率和耐久性都有了提高,可以完全兼容 300mm BEOL (back-end-of-line),并具有>103s保留和无限 (>1011) 耐久性。

佐治亚理工、圣母大学、罗彻斯特理工学院的研究者也提出了一种新型的无电容DRAM(2T0C-DRAM)。该研究小组表示,这种新型的DRAM在运行大型神经网络时可以提供较大的区域,节省大量能源。

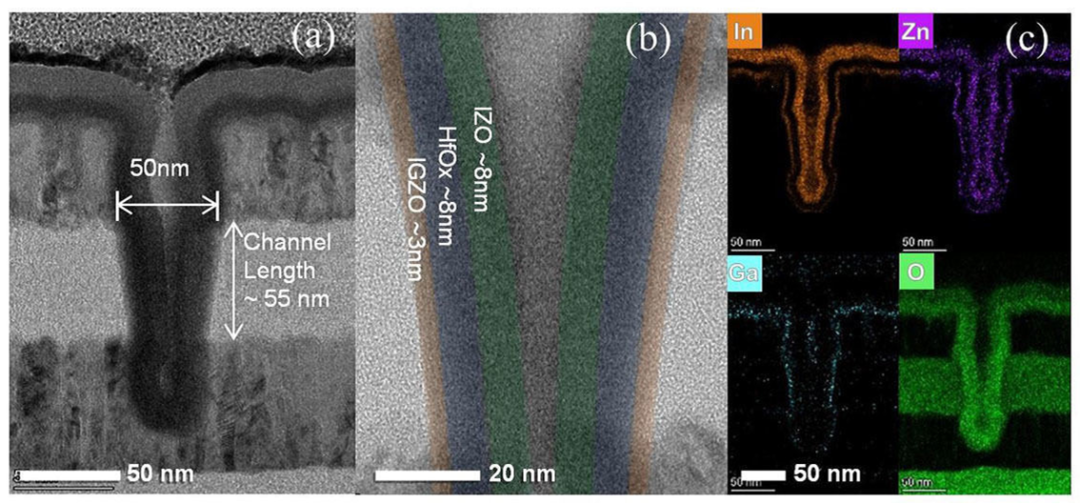

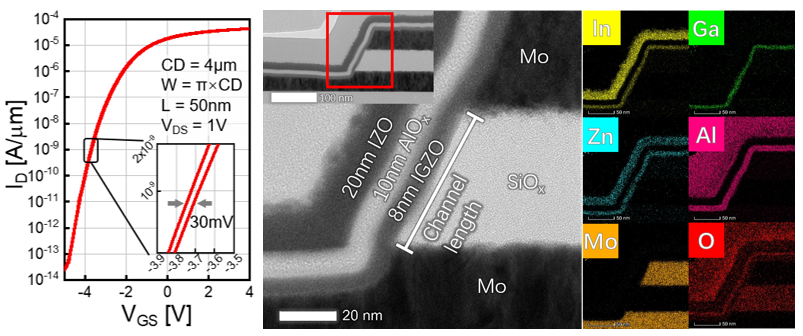

本次华为与中科院微电子研究所合作开发的采用垂直环形沟道器件结构(CAA,Channel-All-Around)晶体管3D DRAM技术,就是基于IGZO材料。

CAA型IGZO FET垂直截面SEM图像和EDX可视化元素分布(图自:VLSI symposium)

TECH+的报道指出,假设有效器件面积为50×50nm2(平方纳米)以下,IGZO厚度为3nm,使用HfOx绝缘膜的IGZO-FET在32.8μA/μm(Vth+1V)。它具有出色的温度稳定性和可靠性,在-40°C至120°C的范围内已确认PBTS(正栅极偏置温度负载)特性。

据中科院微电子研究所此前的文章介绍,在IEDM 2021上,中科院微电子研究所李泠研究员团队联合华为/海思团队,首次提出了新型CAA。据称,该结构有效减小了器件面积,且支持多层堆叠,通过将上下两个CAA器件直接相连,每个存储单元的尺寸可减小至4F2,使IGZO-DRAM拥有了密度优势,有望克服传统1T1C-DRAM的微缩挑战。

沟道长度50nm的CAA IGZO FET器件的转移曲线及截面电镜图(图自:中科院微电子研究所)

据悉,该团队实现了50nm沟长的CAA IGZO FET,其开态电流大于30μA/μm,关态电流小于1.8×10-17μA/μm,同层相连的2T0C单元可以达到300s的保持时间。该研究成果将推动IGZO晶体管在高密度DRAM领域的应用,并以题为 “Novel Vertical Channel-All-Around(CAA) IGZO FETs for 2T0C DRAM with High Density beyond 4F2 by Monolithic Stacking” 入选IEDM 2021,同时获选Highlight Paper和Top Ranked Student Paper。微电子所博士生段新绿为第一作者,华为/海思黄凯亮博士为共同一作,耿玓副研究员和李泠研究员为通讯作者。

CAA IGZO 2T0C电路及retention测试结果(图自:中科院微电子研究所)

华为之前也发表过与存储器相关的文章《华为麒麟带你一图看懂存储器》,文中写到随着芯片尺寸的萎缩,DRAM工艺萎缩将越来越困难,“摩尔定律”即将走到极限,因此各大厂商在研究3D DRAM作为解决方案来延续DRAM的使用。

图自:麒麟公众号

而在华为官网上,一篇题为《奥林帕斯(2021)难题二:下一代存储产业根技术突破》的文章中,就包括FeRAM/、MRAM、PCM、3D DRAM等下一代新型存储介质材料、器件、控制器技术的介绍。本次成果展示的3D DRAM正在其中,可见华为对存储器基础理论的研究早有渊源。

图自:华为官网

尽管HBM的出现开启了DRAM 3D化发展道路,无电容IGZO-DRAM 也成为了实现高密度 3D DRAM 的合适候选者,三星、美光甚至应用材料这样的半导体设备厂商也参与其中。但必须要指出的是,与NAND Flash闪存3D化的迅速发展不同,目前3D DRAM的发展尚处于探索阶段。瑞银投资银行全球研究部认为,3D DRAM最早可能于2027年开始初期生产,到2028或2029年开始实质性量产

EUV造DRAM目前性价比不高,良率很关键

可以看出,华为/中科院这项DRAM技术的基础研究十分前沿,不过正如韩国OERI所说的,制造技术仍是当前中国芯片公司面临的最大问题。

虽然目前DRAM领域最为成熟光刻工艺是采用193nm DUV,其最大极限在大约10nm,但是要突破10nm,就需要13.5nm EUV光刻机。三星和 SK 海力士已经引进了用于先进工艺制造的EUV设备,或正计划引进,由于美国限制,中国公司很难引进 EUV 设备,在一些先进的工艺验证上会比较麻烦。高昂的售价使得EUV经济效益低于DUV,同时如何将EUV技术投入量产也成为传统2D技术面临的难题之一。

另外在良率方面,中韩两国的芯片制造商也还都有进步空间。

OERI 分析说,2019 年开始批量生产第一代 10nm 级(1x 或 18 nm至 19 nm)DRAM 的长鑫存储,目前良率在 75% 左右。据了解,其第二代 DRAM 的良率在 40% 左右。分析师说,长鑫存储的 DRAM 市场份额,截至去年年底还不到 1%,市场排名不会出现大幅波动。

三星的DRAM工艺发展近日也被内部工程人员爆出遇到瓶颈,其基于12-13nm的第五代DRAM工艺1β进展不顺利,计划跳过该工艺,直攻基于11nm的1γ工艺,预计要花费半年的时间。三星曾希望透过采购EUV设备,超车美光基于DUV的1α工艺,但现实是美光利用成本较低的DUV就成功制造出密度更高的产品。

虽然此后三星辟谣,表示传言完全错误,目前 1β工艺 DRAM 开发工作稳定,至于之后 1c 工艺 DRAM 研发量产,将按计划完成。但从最新的DDR5产品上也能看到,美光已经可以提供到1z世代,但三星只能达到1γ。

这也看出,高昂的售价使得当前DRAM厂商购买EUV的经济效益低于继续使用DUV,同时如何将EUV技术投入量产也成为传统2D技术面临的难题之一。

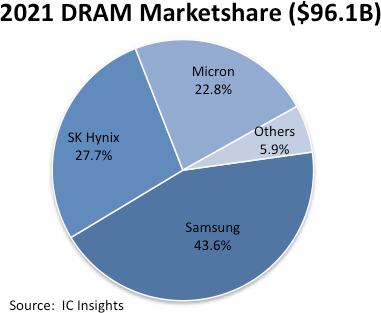

图自:IC Insights

根据IC Insights 发布最新报告指出,三星、SK 海力士和美光这三大供应商在 2021 年共同占据了 94% 的 DRAM 市场份额。其中三星和 SK 海力士两家占全球 DRAM 销售额的 71.3%,这样的数字相信世界上任何一个国家短时间内都是无法超越的。所以对于国产DRAM来说,踏实做好基础研发,从根技术上突破,随着DRAM产品技术逐渐更新换代一步步追赶是最明智的做法。

本文内容参考TECH+、BusinessKorea、IT之家、中关村在线、三星、Rambus、中科院、华为报道