近几年,美国的一纸禁令,切断了华为芯片供应链,也堵上了华为购芯的道路。然而,就在层层打压之下,华为仍然迸发出强大创新能力,近期连续公开了多个关于3D堆叠芯片的发明专利,似乎已为无法代工其芯片的窘境找到解决方案。据悉,这是一种仅利用较老的成熟工艺技术就可以开发出先进芯片的技术,相关信息也引起了业界的广泛关注与热论。

然而,在被传出开发3D堆叠芯片之后,有人高呼作为民族骄傲的华为终于找到解决的方法,但也有人“泼冷水”,不看好这种3D堆叠芯片,更有人把华为3D堆叠芯片与苹果的串联芯片做对比分析。尽管很多人从个人情感的角度,更愿意相信3D堆叠芯片是技术突围之法,但我们不坐井观天、夜郎自大,也不妄自菲薄,还是从客观、公正的角度探讨与分析这个技术,是华为未来芯片技术的发展方向,还是一种无奈的妥协选择。

用面积换性能是否可行?

大家都知道摩尔定律,其核心内容为:“集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍”。然而,随着芯片制程不断接近1nm工艺,行业进入后摩尔时代,芯片性能提升逐渐放缓,各大厂商也很早就开始探索和突破的这个定律的限制。

有人把28nm制程称作“黄金节点”。为什么28nm芯片制程能得此评价呢?因为28nm之后的先进制程,单位晶体管成本不降反升,即先进制程能够使芯片性能更强、功耗更低,但不能让芯片更便宜。因此,很多对性能和功耗要求不太高的领域,采用28nm成熟制程是最具性价比的选择。

不过,我们反过来也可以看到,虽然维持摩尔定律的难度越来越高,但直到目前摩尔定律仍然还没走到尽头。虽然先进制程的成本不断攀升,但晶体管密度上升功耗下降的路也还没走完。如果是单纯的性能落后,我们的确有不少手段可以弥补,比如用面积/成本换性能本身就是很常用的方式。而华为3D堆叠芯片就是典型的“用面积换性能”的做法。

继4月5日公开“一种芯片堆叠封装及终端设备”专利后,华为近日又公开了2项芯片相关的发明专利,即“一种多芯片堆叠封装及制作方法”和“芯片堆叠封装结构及其封装方法、电子设备”。其中,“一种多芯片堆叠封装及制作方法”,可以用来解决多芯片的应力集中问题,能够进行更多层芯片的堆叠。而“芯片堆叠封装结构及其封装方法、电子设备”,可以用于解决如何将多个副芯片堆叠单元可靠地键合在同一主芯片堆叠单元上的问题。

然而,芯片堆叠技术并不是华为最新布局的技术。实际上早在2012年,华为就已经对芯片堆叠技术进行专利公开。该专利为“芯片堆叠封装结构”(申请公布号:CN102693968A),主要涉及芯片封装技术领域,实现芯片的高密度堆叠,提高芯片堆叠封装结构的散热效率。其后几年,华为也在不断对外公开其芯片堆叠的相关技术,足以证明长期以来华为都在这项技术上深耕研发。

然而,除了华为之外,台积电、英特尔、三星等国际半导体厂商都开发了自己的3D芯片封装技术。比如,英特尔于2018年底推出了业界首创的3D逻辑芯片封装技术——Foveros;三星在2018年推出了名为“X-Cube”的3D IC封装技术;台积电则将旗下SoIC、InFO及CoWoS等3D IC技术平台进行整合,并命名为“3D Fabric”。

但特别提出的是,即使3D堆叠芯片是一种“老掉牙”的技术,也并不是物理层面的简单叠加,而是修改了设计逻辑和封装工艺,将双层芯片的技术做到低端制程、高端性能。同时,值得关注的是,今年3月,英国AI芯片公司Graphcore发布了一款IPU产品Bow,采用的是台积电两年前的7nm工艺,但是芯片性能却得以提升40%,甚至优于5nm工艺。该项技术就类似于华为提出的3D芯片堆叠技术。

据悉,Bow采用就是台积电研发的芯片堆叠技术——3D WoW硅晶圆堆叠技术,以类似于3D NAND闪存多层堆叠一样,将两层Die以镜像方式垂直堆叠起来,以更先进的封装技术提升芯片性能。

这也无疑证明了华为研发的3D堆叠芯片技术的可行性。要知道,华为与台积电的合作从16nm工艺一直延续至5nm工艺,或许当年台积电研发3D WoW硅晶圆堆叠技术就曾与华为探讨过。未来,华为借助中国大陆当前投产的14nm工艺生产出性能与7nm工艺相当的芯片也将成为可能。

华为无TSV技术方案

尽管国内外厂商都在3D堆叠芯片上已有相关的成功实践案例,但还是有人对华为3D堆叠芯片技术的应用存在质疑。其中,质疑的主要方向是3D堆叠芯片技术很难解决散热的问题。业界人士指出,芯片堆叠技术还需要解决散热问题,特别对于手机这类体积较小的电子消费产品来说,散热问题就更加重要。

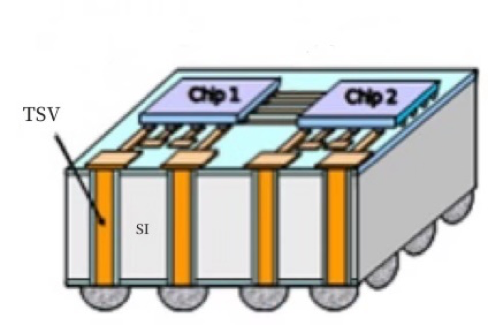

目前,创新的芯片封装和多芯片互连技术将在未来几年成为领先处理器的关键。芯片制造商通常使用两种封装和互连方法:一是2.5D芯片封装,为彼此相邻的小芯片实现高密度/高带宽的封装内互连;二是3D芯片封装,通过将不同的小芯片堆叠在一起使处理器更小。然而,3D芯片封装通常需要相当复杂的布线,增加了封装过程的复杂性和成本,因为小芯片必须使用TSV(硅通孔技术)进行垂直导通。

相对而言,苹果的2.5D芯片封装,即M1 Ultra SoC已有相关产品推出。也因此,有人对华为3D芯片封装和苹果2.5D芯片封装表现出了明显的“双标态度”,甚至出现了“两极化”的观点:一种是“14nm+14nm>7nm”,显然是一种错误的臆想;二是如果应用在手机上,3D芯片封装无法解决老制程节点能效低的问题,甚至认为华为3D芯片封装只是“实验室数据”,还没有实际的产品出来。

为此,我们先探讨一下苹果的M1 Ultra SoC,亦即2.5D芯片封装技术。今年3月,苹果推出了最新的M1系列芯片——M1 Ultra。这个被人称为“苹果有史以来最强大的芯片”的M1系列芯片通过一种名为UltraFusion的创新封装架构,也可称Die to Die Connection(DTD技术),将两个M1 Max芯片互联在一起,创建了前所未有的性能和功能水平的SoC,为Mac Studio提供了惊人的计算能力。

这种技术其实就是2.5D封装技术。有人分析,苹果的UltraFusion使用了1万条DTD连接,提供了高达2.5TB/s的内部互联速度,号称是竞品的4倍。M1 Ultra由两块M1 max拼接组成的,基本可以视为一体的一颗芯片,无论是跑分还是功耗,都能够看出这个拼接技术的效率非常高,以至于多核性能几乎没什么损失,而且理论上还能再拼接两块。还有,苹果简直又刷新了我们的认知:消费级平台单芯片达到1140亿晶体管!

因此,从苹果的拼接芯片案例,我们可以得出结论,2.5D封装主要用于减少Die之间的延迟增加带宽,或者说可以把一个大面积的芯片拆成多个小面积的(面积越大良率越低),拼接成一个大芯片,又不怎么损失性能。但尽管3D堆叠能减少占用面积,把一些功率不大的部分(SRAM或者非易失存储)堆叠起来,但是功率大的部分堆在一起发热会难以解决。

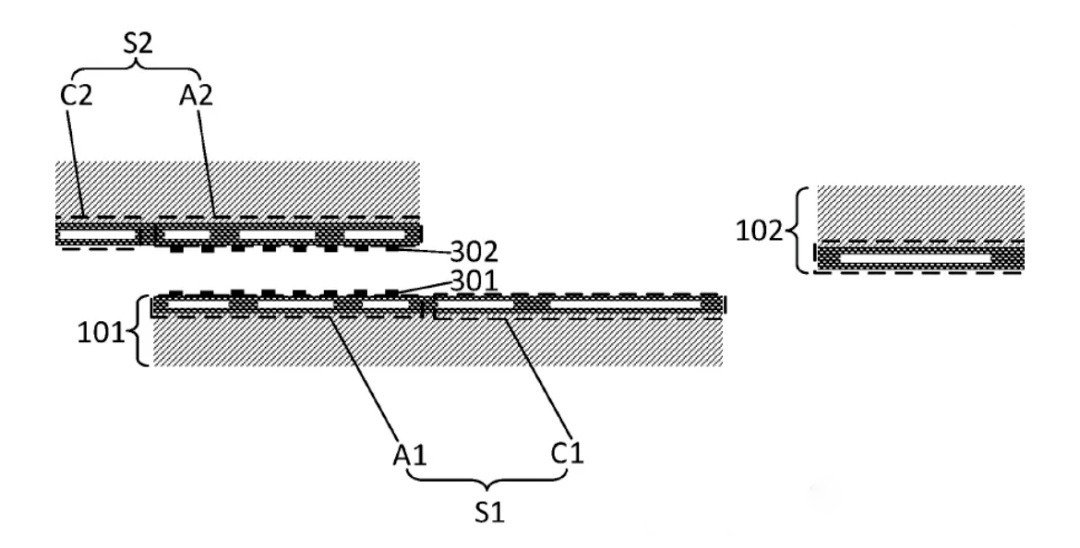

不过,值得我们关注的是,根据专利调查结果,Apple正在考虑以3D堆叠样式加入更多芯片,并使用这种微缝合技术。这从侧面进一步证明了3D堆叠芯片的可行性。甚至有人认为,华为应该开发了一种不使用TSV的替代解决方案。同时指出,华为的设计方案的本质上是2.5D和3D堆叠的混合体,因为两个小芯片在封装内相互重叠,节省空间,但不像经典3D封装那样完全叠放。

TSV示意图(图片来源:迈铸半导体)

实际上,华为在新闻发布会上公开发表的声明清楚地表明,其旨在为其即将推出的产品使用其混合无TSV 3D堆叠技术方案。根据专业人士的技术分享,华为的技术方案使用小芯片的重叠部分来建立逻辑互连。同时,两个或更多小芯片仍然有自己的电力传输引脚,使用各种方法连接到自己的再分配层 (RDL)。但是,虽然华为的专利技术避免使用TSV,但实施起来并不容易且不便宜。

华为混合无TSV 3D堆叠技术方案(图片来源:华为)

有专业人士进一步解释,华为的流程涉及在连接到另一个(或其他)之前将其中一个小芯片倒置。它还需要构建至少两个重新分配层来提供电力(例如,两个小芯片意味着两个RDL,三个小芯片仍然可以使用两个RDL)。由于这种技术流程增加了几个额外的工艺步骤,必然导致成本的增加,但好在其中一个芯片的再分配层可以用来连接内存等东西,从而节省空间。

根据以上专业人士的分析,华为的混合3D堆叠技术方案增加了堆栈的表面尺寸,从而简化了冷却,同时堆栈仍然小于2.5D封装。这对智能手机、笔记本电脑或平板电脑等移动应用很重要。

因此,从技术的角度,华为的混合3D堆叠技术实际上已经解决了很多人担忧的散热的问题。据悉,台积电、三星、英特尔、AMD也开发了自己的2.5D和3D小芯片堆叠和互连方法。因此,华为的技术方案只是顺势而为。不过,有一点还需我们担忧的是,即使华为已拥有这一技术解决方案,但是否能在不受美国严厉限制的前提下找到相关的代工厂商?苹果的2.5D拼接芯片可以找台积电基于其CoWos技术代工,而华为显然没有这个途径。

未来“真正的”芯片之路

根据以上探讨与分析,我们可以得出结论:无论是2.5D拼接技术,还是3D堆叠技术,都是可以切实解决一些行业问题的。但对于华为而言,即使抛开能否找到相关代工这个政治地缘因素,3D堆叠芯片技术能否解决断供的燃眉之急吗?

以华为目前面临的困难而言,3D封装芯片或许有一定辅助作用,但不可能成为根本的解决之道。毕竟这种3D堆叠方式仍然有提升的极限天花板,不太可能无限叠加。即使在一代制程差距内,通过芯片堆叠技术可以让低制程芯片在性能接近甚至超越高制程芯片,并且还能拥有良品率高、成本低等优势,但这也是有极限的。这并不是简单的“两杯500ml的水加一起得到一杯1L的水”的问题。

对此,有专业人士解释道,“通过芯片堆叠技术可以让7nm芯片拥有5nm芯片的性能表现,而14nm芯片则需要6颗芯片堆叠在一起,才能在晶体管数量上比得上一颗5nm芯片。”这带来的结果就是,不仅是体积大增,同时由于线宽过小,会导致极间漏电流增大,逻辑错误增加,极间电容因为布线增多也会大幅增加,从而导致整体功耗增加数倍,进而也导致发热情况非常严重。华为的2012年的专利便已经意识到芯片堆叠的发热问题。

即便这些问题都能够解决,但更关键的问题是,即便通过芯片叠加,使晶体管数量能够比肩高制程芯片,但算力利用率显然不是简单的“1+1=2”,大部分情况下最多只能得到1.3左右,即使苹果M1 Ultra也只能说是更接近2。这项技术想要真正走向成熟,还有不小的路程,只能说其有相对较大的发展潜力。

以苹果2.5D拼接芯片为例,有人认为,苹果之所以不选择更小规模的chiplet,比如改进以M1 pro为chiplet,两片拼接成max,四片拼接成Ultra,毕竟更小的芯片良率更好,比较直观的猜测就是,现有情况下实现拼接多于两片的芯片有困难。而苹果需要Ultra在性能上得到最大的保证。相信,华为3D堆叠芯片也面临同样的问题。

从广义的角度,3D封装技术早已经用在手机上。但如果将3D封装狭义的理解为“双芯或多芯叠加”,那么功耗和散热方面压力就比较大,能否用在手机上可能是未知数。因此,发展先进制程仍然是我们不得不走的必经之路。

只不过,这种技术方案,确实可以帮助华为应对当下缺乏先进制程芯片的困境。否则,华为终端CEO、华为车BU CEO余承东也不会说“2021年华为手机供应很困难,今年华为手机供应得到了极大地改善。”如果事实真是这样的话,那么华为可能已经找到代工3D堆叠芯片的渠道,同时也将逐渐解决芯片供给的问题,而解决供应问题的一项方法很可能就是3D芯片堆叠技术。然而,华为要“王者归来”,只有在先进制程、自研内核、3D封装多管齐下的前提下实现。

- 这不就来了嘛

- 华为手机还有吗?表示怀疑。。。