微处理器传统上一直主导着计算领域,在需求更多算力的推动下,硅基器件在密度方面不断得到提升。按照摩尔定律,每隔两年,晶体管密度就会翻番,这无疑是技术创新的金矿。在这场“淘金热”中,考虑到定制硅涉及的专业知识和费用,几家大型半导体公司已在市场上斩获了稳固地位。现在,随着对计算密集型器件需求的不断增长,ASIC、FPGA 和嵌入式处理器等都被要求执行更复杂的任务。而进入的壁垒一直高得令人望而兴叹。

在整个产业链的终端应用方面,系统的实施在很大程度上取决于利润。 IC 的开发成本、专利许可费和设计的便捷性都直接影响了创建现代电子产品的价格。设计师和开发者一般都依赖硬件加速电路与传统的嵌入式处理器来完成 和专用标准产品 (ASSP)中的核心功能,同时通用处理器众所周知的设计流程也提供了诸多便捷与可靠性。其根本目标是:以最低成本实现快速上市,同时满足现代应用日益增长的复杂计算需求。那么问题就变成了:哪种(些)芯片组合能够以最少的开发时间和成本,而最有效地实现这些应用?

这正是 易灵思 FPGA 一显身手的地方。 易灵思 FPGA 借助简单的软件方法进行软硬件分工,将 FPGA 的固有架构优势与流行的嵌入式处理器的便捷编程特性相结合。本文将介绍这种充分发挥 FPGA 潜力的新设计方法,如何使设计师能最大限度地提高系统设计能力和效率。

易灵思 架构的基本优势

易灵思 钛金 FPGA 在低端和高端 FPGA 之间取得平衡,是款兼具高密度、小封装、低功耗和低价格等优势的器件。通过 16nm工艺技术,钛金 FPGA可以在小至 5.5 × 5.5 mm的封装中集成了多达 100 万个逻辑单元 (LE)、以及大量存储模块和高速 DSP 模块。

这是由于 易灵思 的 Quantum 计算内核具有可重新配置的模块,即逻辑和路由可互换的XLR单元。这消除了传统布线,让 LE 更小、使用更灵活,与传统 FPGA 相比,利用率非常高。 当需要时,软RISC-V 核可在FPGA内核中被例化。在编译时,易灵思 的软件会动态选择是将XLR 单元用作路由还是逻辑功能,以优化其芯片资源。并且, 易灵思 FPGA 实现 的RISC-V CPU 架构,不受 ARM 等专有 IP 内核的约束,规避了任何专利许可费用。

RISC-V 的兴起

RISC-V 是一种免费的指令集架构(ISA),它附带多种软件参考设计、IP 软核和实体器件。 RISC-V 和 ARM 之间的主要区别在于: RISC-V 是一个开放标准,其中 ISA 没有定义任何特定的微处理器架构;其它流行的处理器技术(如:x86、x64 和 ARM)都是基于使用供应商提供的 ISA 和硬件架构而付费的商业模式。

模块化、开源 RISC-V 架构的日益普及,使开发者可以免版税使用这些内核并创建非指定供应商的计算方案。随着摩尔定律继续放缓,这为创新打开了大门。 RISC-V 处理核可以集成到 FPGA 中,以将便捷编程特性,与 FPGA 和 ASIC 架构的并行处理能力和灵活性/可重配置性相结合。

采用 易灵思 FPGA 的新设计方法

易灵思 FPGA 的优点并不仅限于其优化的成本和性能。“量子加速”概念还带来了与传统嵌入式处理器相同的编程便捷性。量子加速依赖于两种关键技术来简化和优化设计流程与设计本身:

1、使用RISC-V处理器

2、使用量子加速器

借助嵌入式RISC-V软核从RISC ISA的便捷编程性中获益

首先,高度可扩展的 RISC-V 处理器被用作系统主力,以确保系统功能最大程度的在软件中表达。使用 RISC-V 处理器的一个固有优势是其自定义指令,可用于扩展处理器的功能以满足应用要求。这确保在使用熟悉的 C/C++ 语言的同时,以最高效率由处理器在本地执行高度加速的任务。

因此,例如,要用C 语言对没有自定义扩展指令的的传统嵌入式处理器编写卷积任务程序,设计师必须将其分解为几条更简单的指令。而使用 RISC-V 自定义指令,则可以在一次执行中完成上述任务。这些基于特定应用的指令大大减少了标准指令所需的周期数,并通过降低功耗大大提高了系统效率。对于人工智能算法中通常使用的卷积,使用自定义指令可将卷积加速 40至 50倍。从而显著提高了系统性能。

定制指令还能让更广泛的产品组合,更快的上市。 易灵思 的一个合作伙伴创建了一个包含数百个自定义指令的库,这些指令可被例化并按需调用。这给他们带来的效果是:可以在一个通用的硬件平台上,定义、创建和快速交付众多的用户产品,而产品间的差异仅靠 RISC-V 处理器的软件优化就可实现。

借助 FPGA 的架构灵活性进行直捷加速

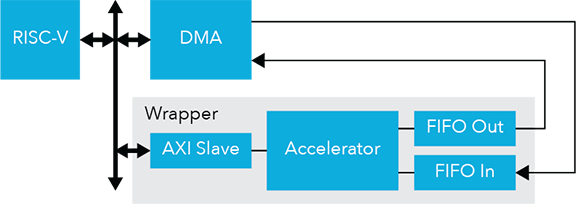

然而,自定义指令往往适合较少量的数据处理。如果用户希望对更大数据块执行数学函数运算。量子加速器套接字(socket)定义了一个框架,使用户能够根据应用的要求轻松地“指向”数据、检索数据并编辑其内容。此加速器套接字具有针对加速器功能、RISC-V 处理器、直接内存访问(DMA)控制器和其它处理模块的特定输入和输出(见图)。 DMA、回调(callback)和与 RISC-V 处理器的连接都在 C 中调用,并几乎替程序员自动执行。所需要的只是一点用于加速的VHDL代码,而易灵思 也已经提供了许多相关示例。

图1

说明: 易灵思 量子加速器套接字具有特定的输入和输出,使用户能够指向大数据块对其检索和编辑并进行硬件加速。该套接字只需最小的 VHDL 设计就可以无缝地进行后续数据移动,因此设计师可以简单地只需紧盯性能瓶颈就好。

这种方法的好处体现在极大地缩短了上市时间。使用这种预定义的加速建构,易灵思 的一位合作伙伴设计了一款相机系统,包含输入传感器、人工智能引擎、目标检测和分类、以及输出显示子系统。从项目启动到功能齐全的样机以及量产,整个过程才耗时一周多一点。

硬件加速的微方法和和宏路径

总之,易灵思 FPGA 既利用了开放式 RISC-V 标准的固有优势,又结合了使用定制指令或能快速修改大块数据的定制加速器框架的长处。这使电子设计公司和制造商能够实现以下目标:

- 通过优化的软件设计流程,使产品最快上市

- 通过软件定义的架构化灵活平台最大限度地降低设计和生产成本

- 创建一个面向未来的设计,既满足现代应用的计算需求,又可以通过附加功能轻松升级

易于编程的 FPGA 的价值

易灵思 把 FPGA 从传统的不起眼的设计替代品转变为设计必需品。这些设计技术模糊了传统系统架构的界限。随着可配置、经济、低功耗 、具传统嵌入式处理器方案速度的FPGA 的推出,借助以下方式可推动大众市场采用这些平台:

- 用集成的 FPGA方案完全替代 ASSP 设计

- 扩展现有 MCU 的功能以适应新要求和新市场

- 在保有传统嵌入式处理器(例如 ARM)设计流程简单性的情况下替换嵌入式处理器

与 ASIC 等定制芯片相比,构思和生成基于FPGA的方案所需的时间已大为缩短。 在成品足够便宜时,在适应性强的 FPGA 上实现定制功能,是可以取代ASSP。 易灵思 嵌入式 RISC-V 处理器也可以进行定制,以模仿和扩展现有 MCU 的功能。从模仿一款熟悉的 MCU 开始,可以在 FPGA 架构中例化增强的自定义功能以及自定义加速模块和 I/O 信号调整。

使 FPGA 成为设计要素

最重要的范式转变在于能够利用传统嵌入式处理器(例如 ARM)设计流程的简单性进行快速创新。高度集成的 易灵思方案包含了已为人熟知的控制器架构和高度加速的配套模块的各种衍生品,所有这些都在同一个硅芯片中。这为 易灵思 FPGA 在边缘计算之外——从基本的物联网设备到数据中心卡——的更多样化市场打开了大门。

对于很多以往需要用到通用嵌入式处理器+强大的FPGA的设计,设计师们现在可以用更简单的方式在 FPGA上实现。传统上利用标准 CPU 或 MCU(例如物联网传感器节点)的项目现在都可以被 FPGA 所取代,且功耗相当(如果不是更少的话),外形小巧、成本低廉以及可以直接采用软件设计流程。还有最大的好处是:基于 易灵思 FPGA 平台的架构灵活性,这些设计自来就是面向未来且可升级的。

推动器件向高算力迈进的设计师也可以借力 易灵思 FPGA。这使业务能够从传统的物联网和宽带用例(如家庭自动化、机器监控和移动设备上的常用高清视频流)转向下一代应用,如自动驾驶汽车、无缝沉浸式现实体验(AR/VR头戴设备) , 等等。 易灵思 FPGA 还可以满足这些基于边缘、高带宽或时间敏感的用例。企业可以通过正确的处理能力来满足未来计算要求,从而有效地训练、运行和升级各自的机器学习算法。

结论

易灵思 FPGA 可以显著简化设计周期,立即摆脱对 ASIC 的硬件开发要求,并简化相对CPU 和 GPU 不够直接的硬件加速过程。 这种FPGA 产生了巨大影响,将 FPGA带入了很多以往不可企及的新市场。 在向熟悉的软件技术开放硬件设计环境的过程中,易灵思 极大扩展了可移植到 FPGA 的设计范围,进一步缩短了上市时间并提高了最终用户应用的灵活性。 由此带来的成本和密度优势将使 FPGA 在市场上的拓展远远超出传统的应用范畴,并推动其进入可触及我们生活方方面面的应用。

- 就是把 CPU做得事, 用 FPGA内置的RISC-V核,再做一遍吧~~~~

- 【ICCAD2024】AI时代,先进数字芯片设计下的国产EDA新路径 面对AI时代带来的差异化趋势、软件应用及开发时间长、软硬件协同难、高复杂度高成本等挑战,国产EDA仍需不断探索和创新。

- 美国最高法院驳回英伟达上诉请求,被控诉涉嫌误导投资者 股东诉讼指控英伟达的首席执行官黄仁勋隐藏了公司记录性收入增长主要由其旗舰产品GeForce GPU的挖矿销售驱动,而非游戏销售,导致投资者对公司的盈利来源和风险敞口产生错误认知。

- 为什么说机器人的“ChatGPT时刻”将至?从ROSCon看当代机器人开发… 今年初的GTC上,黄仁勋就说机器人的“ChatGPT时刻”要来了。也就是说这波AI驱动的机器人热潮要来了...最近的ROSCon China 2024大会似乎也能看到这种迹象...

- 华为Mate 70系列实现芯片100%国产化 近日,华为终端BG CEO何刚在和紫牛基金创始合伙人张泉灵的对话中表示,华为Mate 70系列每一颗芯片都有国产的能力。此外,日前在深圳宝安中学的一场讲座中,华为终端BG 董事长余承东也自豪地宣布Mate70实现了芯片的100%国产化。

- 华为Mate 70 RS拆解:麒麟9020芯片现身 华为Mate 70系列中的Mate 70搭载了麒麟9010芯片,而Mate 70 Pro/Pro+/RS则首发了麒麟9020芯片。近日,百万粉丝的网红博主@杨长顺维修家 对华为Mate 70 RS进行了拆解……

- 英特尔开始从外部寻找新CEO:陈立武等在候选名单上 常情况下,英特尔的CEO在65岁时退休,而现年63岁的基辛格突然被退休,让市场感到意外。为了确保平稳过渡,英特尔董事会立即着手寻找新的CEO人选……

- “一碰交互,共触未来”ITMA峰会盛大 目前,智能终端NFC功能的使用频率越来越高,面对新场景新需求,ITMA多家成员单位一起联合推动iTAP(智能无感接近式协议)标准化项目,预计25年上半年发布1.0标准,通过功能测试、兼容性测试,确保新技术产业应用。

- 中科院微电子所在忆阻神经-模糊硬 中科院微电子所集成电路制造技术重点实验室刘明院士团队提出了一种基于记忆交叉阵列的符号知识表示解决方案,首次实验演示并验证了忆阻神经-模糊硬件系统在无监督、有监督和迁移学习任务中的应用……

- 直角照明轻触开关为复杂电子应用提 C&K Switches EITS系列直角照明轻触开关提供表面贴装 PIP 端子和标准通孔配置,为电信、数据中心和专业音频/视频设备等广泛应用提供创新的多功能解决方案。

- 投身国产浪潮向上而行,英韧科技再获 投身国产浪潮向上而行,英韧科技再获“中国芯”认可

- 项目动态|长飞先进武汉基地首批设备搬入 今日,长飞先进武汉基地建设再次迎来新进展——项目首批设备搬入仪式于光谷科学岛成功举办,长飞先进总裁陈重国及公司主要领导、嘉宾共同出席见证。对于半导体行业而言,厂房建设一般主要分为四个阶段:设备选型、设

- 投资20亿!路芯半导体掩膜版生产项目首批工艺设备机台入厂 来源:苏州工业园区12月17日,江苏路芯半导体技术有限公司掩膜版生产项目迎来重要进展——首批工艺设备机台成功搬入。路芯半导体自2023年成立以来,专注于半导体掩膜版的研发与生产,掌握130nm至28n

- 拜登拟对成熟制程芯片启动301调查 来源:观察者网12月18日消息,自12月2日美国发布新一轮对华芯片出口禁令以来,不断有知情人士向外媒透露拜登政府在卸任前将采取的下一步动作。美国《纽约时报》12月16日报道称,根据知情人士以及该报查阅

- 华为Pura80细节曝光:麒麟9020跑分能上130万分 对于华为来说,今年的重磅机型都已经发完了,而明年的机型已经在研发中,Pura 80就是期待很高的一款。有博主爆料称,华为Pura 80将会用上了豪威OV50K传感器,同时电池容量达到5600毫安时。至

- LGDisplay引入AI处理OLED质量异常效率提升90%,每年节约超2000亿韩元 来源:IT之家12 月 18 日消息,LG Display 韩国当地时间今日宣布,已将自行开发的“AI 生产系统”投入到 OLED 生产线的日常运行之中,该系统可提升 LG Display 的 OLE

- JNTC宣布在印度开发和量产车载盖板玻璃 12月18 日,据报道,JNTC与印度Welspun BAPL就车载盖板玻璃的开发及量产签订了投资引进业务合作备忘录(MOU)。资料显示,JNTC是韩国的一家盖板玻璃厂商。Welspun的总部位于印度

- 超60GW!飙升12倍,储能机会来了? 又一地,新型储能机会来了?■ 印度:2032储能增长12倍,超60GW据印度国家银行SBI报告,印度准备大幅提升能源存储容量,预计到2032财年将增长12 倍,超60GW左右。这也将超过可再生能源本身

- 高科视像、新视通等持续扩大COB产能 近期,高科视像、新视通、江苏善行智能科技等企业持续扩充COB产能。插播:加入LED显示行业群,请加VX:hangjia188■ 高科视像:MLED新型显示面板生产项目(二期)招标12月18日,山西高科

- 巨头疲软行业内卷,极越为谁而“亡”? 在上海嘉定叶城路1688号的极越办公楼里,最显眼的位置上,写着一句话:“中国智能汽车史上,必将拥有每个极越人的名字。”本以为这句话是公司的企业愿景,未曾想这原来是命运的嘲弄。毕竟,极越用一种极其荒唐的

- 扎克伯格39岁华裔爱妻罕见炫舞,丰韵身姿尽显“女王”气场,宠溺深情令人动容 在科技浪潮翻涌的硅谷,马克·扎克伯格不仅是“脸书”帝国的掌舵人,更是以其谦逊低调的形象,在公众心中树立了独特的领袖风范。然而,在镁光灯难以触及的私人领域,扎克伯格与39岁华裔妻子普莉希拉·陈的爱情故事