自Intel默秒全时代结束之后,PC、数据中心CPU市场的竞争格局在发生变化。很多人将其归因于Intel制造工艺从原先的称霸全场,到如今俨然落后于台积电和三星。这个说法无论对不对,似乎从Intel被AMD蚕食市场,到苹果Mac弃用Intel处理器,起码从时间上来看的确是自Intel 10nm和7nm工艺难产,以致逐渐跟不上台积电的步子开始的。

Intel十多年的技术霸权,在短短2年间就不见了。虽说像Intel这种大公司,业务范围、营收量级并非AMD这类企业可比;而且在市场大趋势下,其营收表现也远远谈不上岌岌可危;但前年在谈到Intel的时候,我们就说其状态是“struggling”的;即便今年的12代酷睿,以及Sapphire Rapids、Ponte Vecchio的确是为Intel讨回了不少颜面。

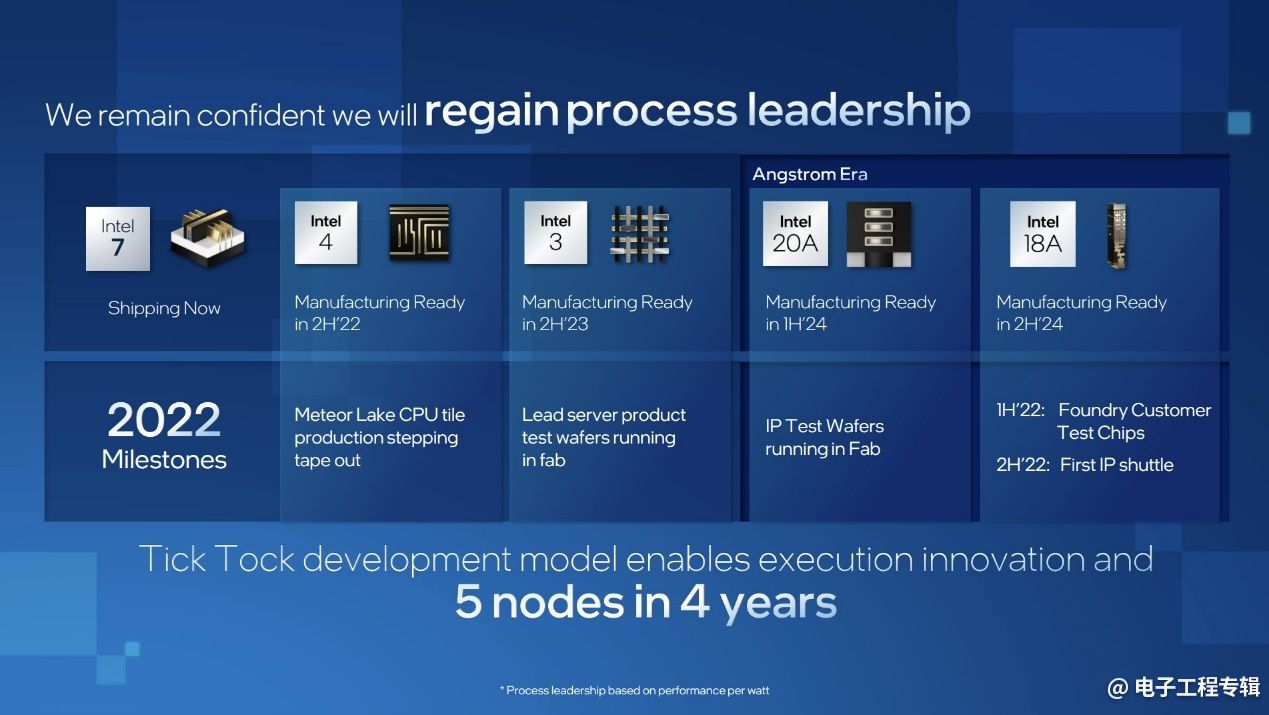

IDM 2.0计划诞生,Pat Gelsinger接任CEO,并表示要带Intel重回技术领导者地位。这条路可一点都不好走,尖端制造工艺的难度和成本投入都在加大,要追赶绝非一朝一夕可成。去年7月,Intel Accelerated活动宣布工艺改名,以及后续包括Intel 4、Intel 3、Intel 20A、Intel 18A在内的工艺节点迈进计划,我们就评论说该计划表对Intel而言是巨大考验,尤其要求Intel严格按照其中的时间规划推进工艺节点,本身就潜藏相当大的挑战。

上个月Intel召开投资者会议,再度展望了未来计划,也谈到了如何夺回技术制霸地位的问题。这对我们理解Intel这家公司,以及尖端半导体制造工艺未来的发展是很有价值的。

制造工艺,一份激进的计划表

先来看看大部分人关心的工艺问题。虽然去年的Accelerated活动已经谈到了不少的未来规划,也提到了2024年追上竞争对手,2025年重回领导者地位;但Intel这次又把时间提前了。其中Intel 18A(A是指angstrom埃,1纳米=10埃)原计划于2025年问世,但这次Intel宣布将其提前到了2024年下半年(应该是指量产,或准备好量产)。

而且Intel还表示当前已经给一家客户提供了18A的测试芯片,并预计在今年会有2次18A工艺的流片,明年上半年会有4颗测试芯片。这表明18A的规划真的很早,Intel是铁了心要在18A重回昔日领导者地位。投资者会议上,Pat Gelsinger还展示了一张据说是18A SRAM测试晶圆。

如此一来,Intel的工艺节点更新计划表就显得更激进了,4年要推进5个主要工艺节点,虽然这其中还是有工艺上的小改款。我们再来回顾一下接下来一段时间内Intel的工艺推进计划:

• Intel 7,原10nm Enhanced SuperFin工艺,去年到今年已经大规模量产。我们对12代酷睿桌面版、高性能笔记本版已经有过体验。Intel 7相比10nm SuperFin有10%的每瓦性能提升。

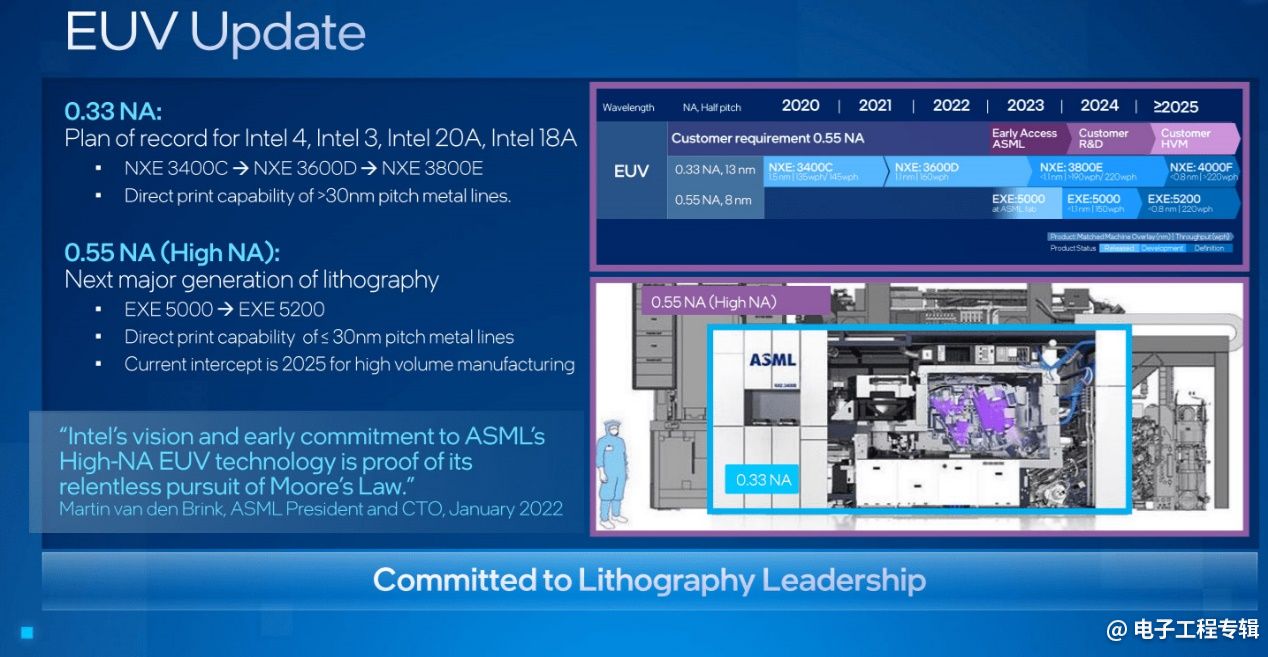

• Intel 4,原7nm工艺。很久以前Intel对于这代工艺的预期是达成2倍的晶体管密度提升,但现在好像Intel基本不再提这茬,可能是路线有变。就像去年Digitimes公布的晶体管密度预估,似乎也没有2倍提升。Intel表示Intel 4相比于Intel 7会有20%的每瓦性能提升,也是Intel首个采用EUV的工艺;今年下半年量产(或准备好量产)。

• Intel 3,从Intel的规划来看,Intel 3属于Intel 4的同代演进,也就是半代改款工艺;预计会有密度更高的库,优化过的金属堆栈、更低的VIA电阻、应用更多的EUV层;实现18%的每瓦性能提升;计划量产(或准备好量产)时间为2023年下半年。

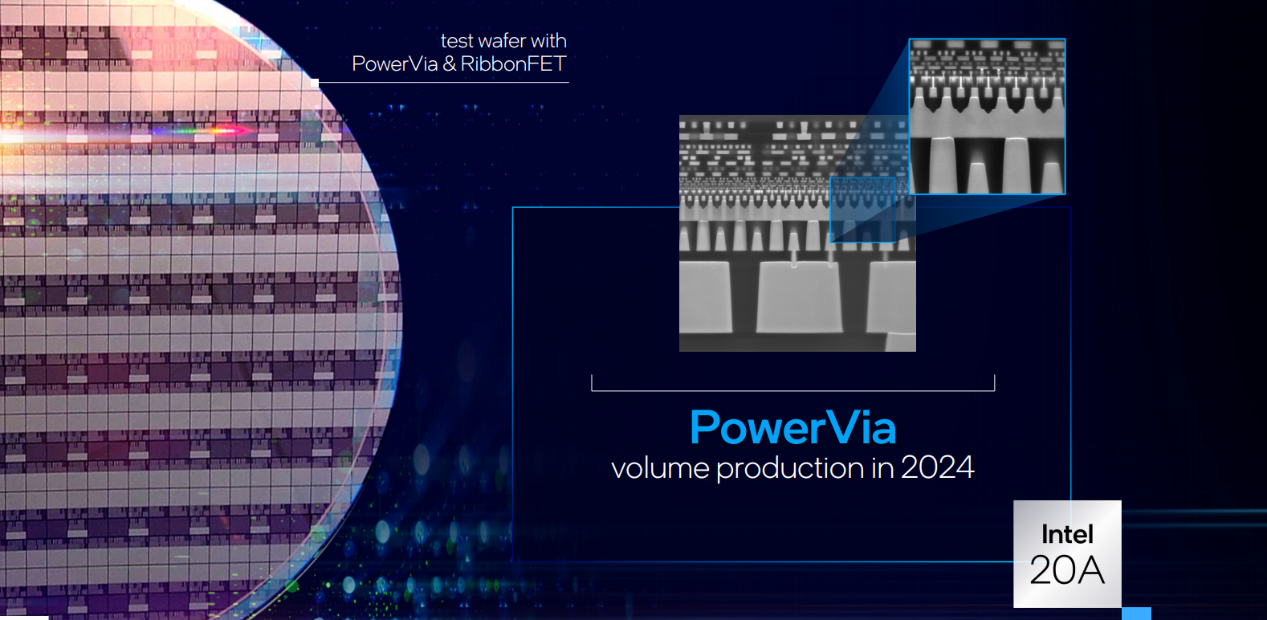

• Intel 20A,Intel首个要采用GAAFET晶体管结构的工艺,Intel将这种晶体管称作RibbonFET;另外会有一种名为PowerVia的Backside Power Delivery技术随之而来——这种技术我们在此前的文章里已经做过解读。20A预计实现15%的每瓦性能提升,量产(或准备好量产)时间设定在2024年上半年。

• Intel 18A,18A相比20A又算是个半代工艺,实现大约10%的每瓦性能提升,如前所述2024年下半年量产(或准备好量产)。从这个时间来看,Intel 18A量产的时间将早于台积电和三星的2nm工艺。

这张计划表进度之快,基于现在的行业现状,似乎是很难想象的。毕竟我们都知道在此之前的14nm和10nm浪费了Intel多少年的时间。尤其10nm走向成熟真可谓一路跌跌撞撞,坎坷不断。

这其中比较值得一提的是,要夺回领导者地位的18A工艺节点,Intel很早之前就强调会率先用上ASML的High-NA(高数值孔径)EUV设备,0.33NA。不过从Scotten Jones的消息来看,这台设备固然能够提供一定的竞争优势,但台积电预计也能很快拿到(在Intel拿到的1个月之后),那么Intel在工具方面的优势或许就没那么显著了。

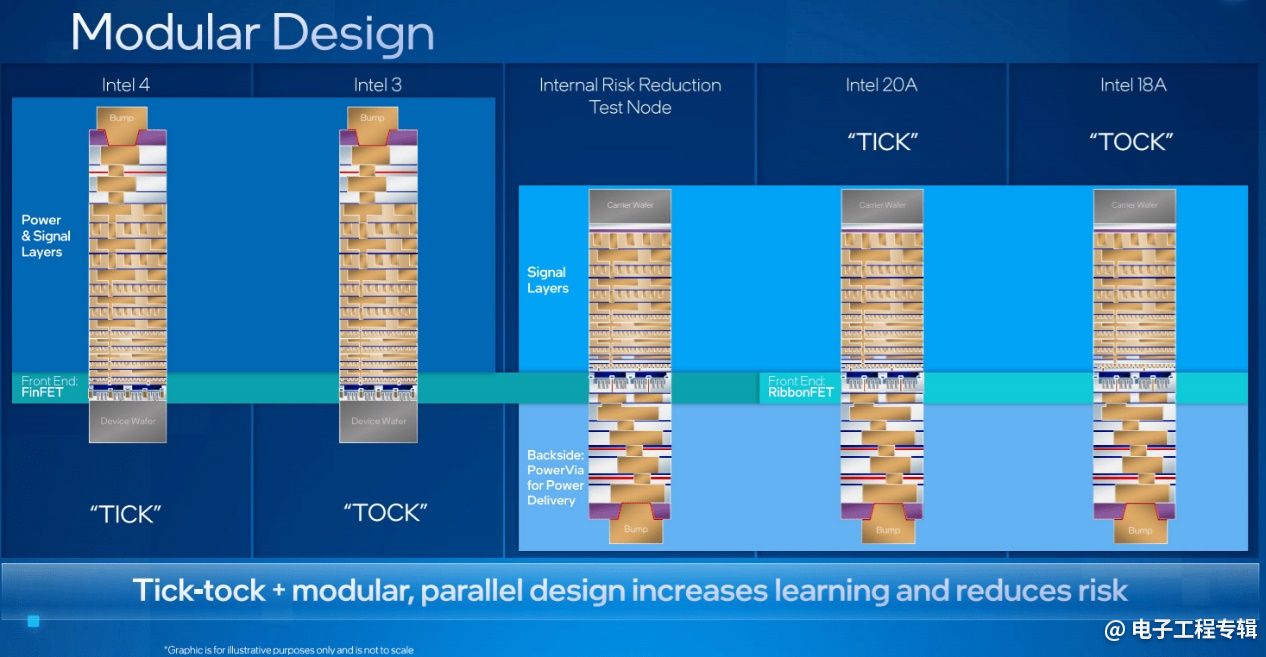

这来得及吗?工艺的模块化方案

在如何快速实现工艺推进的问题上,Intel在投资者会议上也是给出了一些信息的。除了后文将会提到的人才回流及与供应商搞好关系之外,Intel引入了一种“模块化设计架构”,并称之为Tick-Tock。这个Tick-Tock和早年Intel处理器的嘀嗒更新计划是不一样的。

在此,主要的晶体管pitch scaling称为tick节点,而tock则是指基于此的优化和更新。Intel 4、Intel 20A都属于tick更新;而Intel 3和Intel 18A就是tock节点了。

为了确保工艺升级不受制于某些瓶颈,Intel对开发工艺流程做了简化,而且对创新、执行和可预测的一些变量做了反复考量。也就是要让工艺开发的不同组成部分,实现更大程度的解耦或者独立,让某一部分的进度不至于影响到整个工艺的更新。比如说信号、供电、晶体管这几个部分就可以由不同的团队去做,实现工艺的“模块化”。

举个例子,PowerVia——也就是backside power delivery网络。以前的文章已经解释过这种技术,简单来说现有绝大部分方案是把供电和信号层放在同一个互联堆栈中的,而PowerVia是将所有的供电部分放到了晶体管的后方,不仅可以让信号互联更密集,信号传输效率、延迟表现也有了提升,供电互联的电阻也降低了,实现了性能、功耗、面积的优化。

Intel 3工艺节点有个定制版本,可用于测试工艺流程,包括晶体管层、信号互联,以及键合到载体晶圆(carrier wafer),并翻转晶圆后,再去后方构建供电网络。那么这个测试流程就能完全地独立于RibbonFET晶体管之外去进行了;两者的开发进度受到彼此的影响更小。

这类风险比较大的工艺流程,也就会相对更少地影响到整个工艺节点的更新了。还有像20A、18A的开发就有不同的团队在执行,应当都属于加速工艺更新的组成部分。

另外,Intel的IDM 2.0计划中提到更积极地对外提供foundry代工服务。在投资者会议上,Intel提到对外只提供tock节点,而tick节点是完全对内的,确保芯片设计客户拿到的是成熟版的工艺。这其实某种程度上消除了客户所需承受的工艺风险;也让最尖端的技术始终掌握在了自己手里。

传说中的foundry代工业务如何?

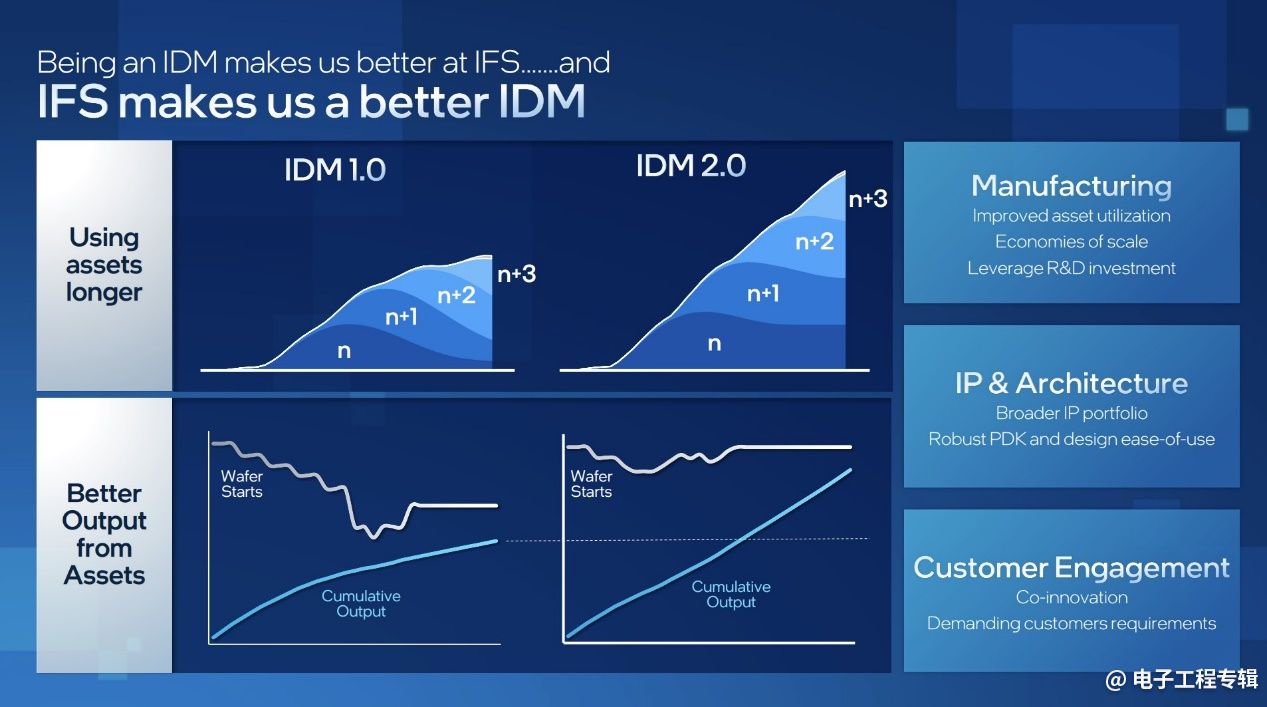

作为IDM 2.0计划的重要组成部分,Intel此前就宣布foundry厂更积极地接外部的单子(也就是所谓的IFS服务)。这部分Intel谈到了如何充分利用旧工艺的制造设备,实现更高效的资源转化和复用;以及尽早实现较高的产能输出和工厂利用率。Intel表示自己在这些领域都是有经验和优势的。

这对Intel的价值很重要的一点,在于让现有资产的使用寿命更久,这对于提升Intel的毛利率是有价值的。2001前后,Intel和台积电都开始上线130nm工艺。到现在为止,台积电也还在运作130nm、90nm、65nm、40nm工艺产线,但Intel就全线转向32nm和更新的工艺节点了。而更大程度给外部芯片设计企业提供foundry服务,也就实现了资产更高、更长时间的复用,如上图所示。

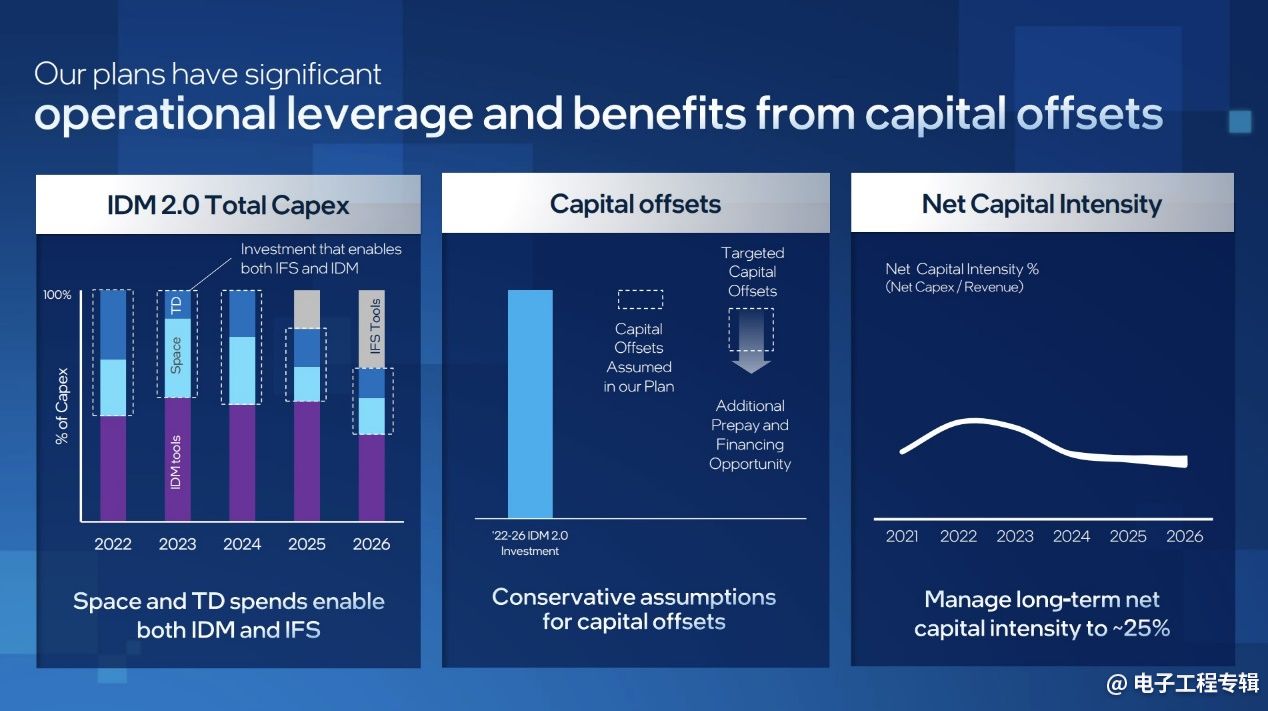

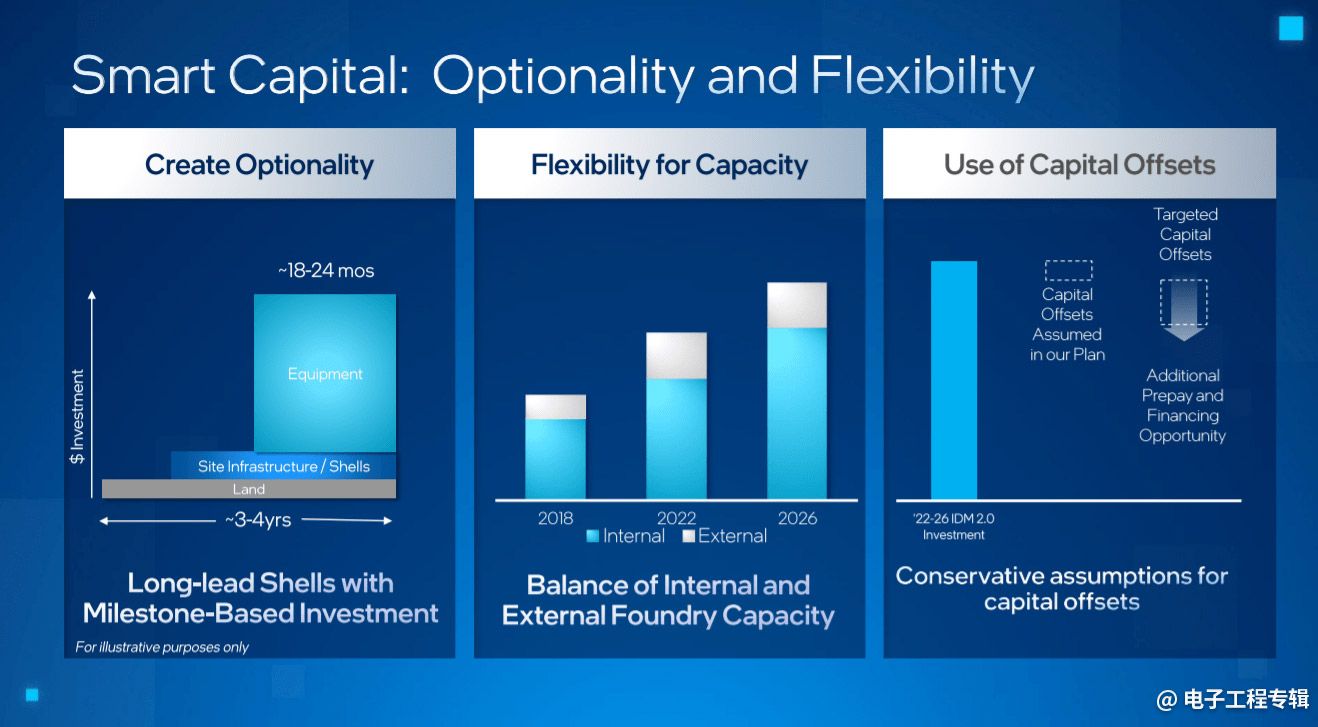

针对foundry服务的开展,Intel也强调了会建更多的fab厂;建厂资金部分来源于现有业务、借贷、政府补助和客户的预付款;在建厂资金问题上有可能会和Brookfield Asset Management资产管理公司合作。

在foundry代工计划方面,2022年Intel可能更多将投资集中在技术开发上;今明两年是大范围地把厂(所谓的fab shell)盖起来,虽然可能在真正需要扩充产能的时候才会全面启用;这两年当然同时也会购置生产工具和设备,但2025、2026年会是工具资金投入上的主要年份。

Intel长期计划在CapEx资产成本投入大约是25%,其中2022、2023年会有35%。这在Intel历史上应该都是前所未见的。

上面最左侧的图展示的是建一个fab厂各个部分的时间和资金投入。先是把fab shell盖起来——这在整体成本中是占比相对较少的组成部分,但所需时间跨度比较久;然后往工厂里填充设备(equipment)。这套方案其实在台积电就已经有了较长时间的实践。

另外如前文所述,CapEx投入会部分由政府补贴、客户预付款之类的组成部分抵消。不过Intel强调如果这部分资金抵消有更多盈余,则Intel还会持续做进一步的CapEx投资。

而对Tower的收购(以及此前传言说Intel考虑收购GlobalFoundries)事实上都能为其foundry业务提供不少助力。比如近期对Tower的收购就很好地填补了尖端工艺之外的工艺节点技术;与此同时在PDK方面,Intel一直以来以IDM为主的运营模式,致其工艺流程都是为其内部需要所设——Tower这方面的能力就能弥补Intel Foundry Service先天的不足;而且Tower本身涉足的领域涵盖到了RF CMOS、锗化硅功率IC、CMOS图像传感器、SOI等…

在收购Tower之后,Intel说现在全球只有两家foundry厂横跨了微米级节点到<10nm工艺节点。其一自然就是台积电;Intel显然是将台积电作为自家foundry服务的直接竞争对象了。

据说去年Intel在foundry服务上的营收达到了8亿美元。不知道这笔收益的具体构成情况如何。Intel Foundry Service现有的大客户至少包括了思科(Cisco Silicon One)、亚马逊、高通、美国政府机构等。

时代在变,文化在变

上个月SemiAnalysis的分析文章提及Intel的企业文化转变,其中谈到了很有意思的一点:21世纪10年代中期,Intel的半导体制造工艺仍然领先于其他竞争对手好几年。当时的Intel是相当不可一世的,对上游设备供应商都是爱答不理的态度。

比如此前我们分析Intel 10nm工艺技术文章就谈到,10nm工艺的一大特色在于引入了钴材料。当时美国应用材料曾告诫Intel,具体的工艺尚未完全准备就绪,Intel完全没有理会。当然我们不能说后来10nm工艺的难产一定与钴材料的应用有关,但当年的Intel真是有着学霸的架势。

不过现在的Intel情况就很不一样了。现在Intel会去主动强调和上游企业之间的合作,比如Intel对外发声很积极地提到与ASML之间的合作,ASML帮助Intel共同解决EUV工艺的量产问题,还有反复提及的Intel成为第一个获得High-NA EUV设备的企业。

Intel说:“我们不仅采用来自设备领域的专业知识,还有EDA领域,而且正转向行业标准设计工具和PDK……”“这是个全新的Intel,比以前都更加开放、积极和主动。”

另一方面,近一年涉及Intel的人才回流报道相当普遍。电子工程专辑几乎每隔一阵就有类似的新闻报道,包括供应商的、客户的、竞争对手的(还有苹果的),以及此前业界知名的行业人才流向Intel。近1年时间里,Intel扩招了超过17000人。企业内部的变化是实实在在在发生的。

以Intel的PC业务为缩影做观察,我们此前就说在这一市场上,今年Intel应该会比前两年好过不少,因为12代酷睿Alder Lake处理器总算在性能表现上抢回了些风头。去年和前年Intel是被AMD和苹果先后戏谑的。只不过2025年之前,PC处理器市场恐怕会表现为不同参与者的差拍竞争,彼此各有看点,短时间内很难再有Intel“默秒全”的局面出现。

在这次投资者会议上,Intel就PC处理器产品已经展望到了16代酷睿(Lunar Lake,Intel 18A),给人以非常美好的展望和向往;被很多人形容“曾经的学霸终于发愤图强”。我们认为Intel公布的路线图更多的是给投资者以信心,规划真的不可谓不激进。

未来几年内的市场对Intel而言还有很大的不确定性和机会,比如说Intel准备大规模上市的GPU产品——无论是面向消费用户的,还是面向数据中心的,这对Intel而言是全新的领域(而且还涉及到与台积电之间的合作);究竟好不好也待市场检验。在服务器CPU的市场竞争中,Intel在堆核大战里相较AMD暂时还处在弱势。Intel在networking领域新开辟的IPU战场又充满机遇……

Intel为自身和市场发展传达了很积极的信号,但如此前我们多次谈到的: 2025年重回王座的基础,就是严格按照这份计划表执行。这对Intel而言是有机会、却也充满挑战的一条路。

- 机会都i摆在所有企业面前,唯有从事科学研究的企业,就有机会,科学研究越强,王座的机会更大,Intel是有较大的机会的。

Intel的现况其实是人类现况——没有新材料的缩影之典型。