虽说3nm这两年时常被我们挂在嘴边,但目前有关3nm工艺制程的信息仍然不多,毕竟三星、台积电和Intel的3nm今年都不会正式问世。不过从目前这些foundry厂已公开,和其他已知的信息来看,3nm的竞争格局其实已经相当明朗。

我们在4nm文章里也明确表达过:3nm时代,台积电仍将保持高歌猛进和技术上的绝对领先;而且领先地位将十分明确。

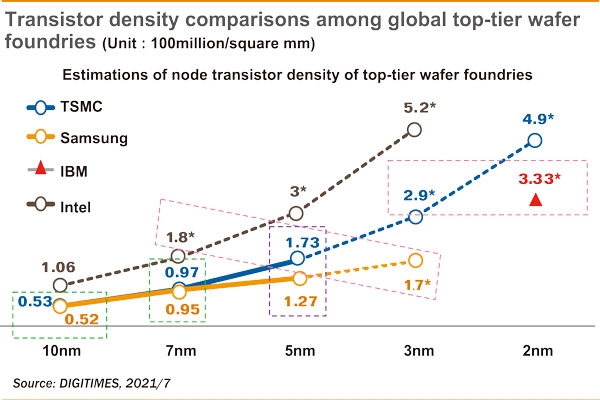

去年7月Digitimes发布过一份尖端工艺制造厂在这几代工艺上的晶体管密度演进曲线,可明确感知三星和台积电在尖端工艺的晶体管密度方面的差距正在5nm之后的代际上拉大;Intel的问题则在于随其原10nm工艺的延后,后续工艺的更新时间具备极大不确定性。

来源:Digitimes

不过在看这张图时需要注意两点,其一在于Intel去年7月底对其工艺进行了改名操作,所以以上图片中Intel曲线对应的7nm现名为Intel 4——后面的工艺也随之变化;其二,Digitimes对晶体管密度的预估未必是准确的,某些值与其他研究机构(如Wikichip)的预估存在差异。

还有一点也是我们反复强调的,代表每个工艺节点的最高晶体管密度的确有参考价值,但不应成为判定其先进或优秀与否的唯一依据。而且“晶体管密度”这个值也有其特定的计算方法,它无法代表真实的芯片实际的晶体管分布情况。但从大方向来看,起码现在看晶体管密度来对比不同foundry厂的工艺节点,好像也基本靠谱。

3nm的时间:大家都在拖

尖端制造工艺仅剩的市场参与者也就只有台积电、三星和Intel了。Intel自10nm工艺难产和遭遇良率问题后,原7nm(现Intel 4)工艺也延后了。明年3nm竞争之年开幕后,Intel与另外两名竞争对手可正面对决的也就是Intel 4。从Intel去年年中更新的消息来看,Intel 4计划于“2022年下半年量产”。

这个时间点其实和另外两家的3nm工艺量产与上市的时间差不多。所以Intel基本是被排除在3nm竞争之外的了(虽然只是以3nm这个称谓而言)。Intel 3的量产要等到在2023年下半年。而按照Intel的计划,其foundry厂要实现反超的工艺节点预计会是2025年的Intel 18A——按照台积电和三星的计划,2025年开推的是2nm工艺节点。

台积电方面,去年10月台积电CEO魏哲家提及台积电N3工艺将于2022年下半年大规模量产。但采用N3工艺的首批芯片出现在市场上需要等到2023年第一季度。按照当代完整节点工艺迭代的节奏,这么算来N3可能比计划晚到了半年。

三星应该是目前3nm工艺节点宣传最积极的一家企业了。从最初2019年4月3GAE的PDK 0.1(Process Design Kit)问世开始,三星就在不遗余力地推广GAA(Gate-All-Around)结构的晶体管,毕竟三星是头一个准备在3nm节点迈入GAA结构的。

不过三星也没能按照此前的预期时间达成3nm量产。目前有关三星3nm何时量产的消息似乎并不十分统一。三星Foundry在去年的中国IP与定制芯片生态大会上公布的一张路线图上,原本的初代3GAE不见了,而加强版3GAP预计于2023年进入HVM(高产量制造)阶段。AnandTech此前的消息提到,3GAE仍计划于2022年量产。不过AnandTech认为3GAE可能仅面向三星自家的LSI业务,属于某个试产的节点。Digitimes去年8月份的消息也提到,2023年可能是三星3nm GAA技术规模量产的可靠时间。

无论如何,3nm节点上,台积电和三星仍将呈现正面对决的态势。

3nm工艺晶体管密度:差别好像有点大

基于我们此前多次提到的,如今的“5nm”“3nm”这些工艺节点数字不再代表晶体管的任何物理尺寸,而仅是一个用于表示工艺迭代的标识;不同foundry厂同样标识相同的数字,可能其背后的含义与技术是大相径庭的。比如同为5nm,三星和台积电对各自5nm节点的定位和定义就完全不同,这一点在此前的文章里已经多次强调。

我们还是不可免俗地用晶体管密度来说明,明年两家foundry厂的3nm工艺差异几何。文首其实已经给了Digitimes的数字。Digitimes认为,三星3nm工艺可达成的晶体管密度大约为170 MTr/mm²(百万晶体管每平方毫米);而台积电早在5nm时代就已经将晶体管密度推进到了173 MTr/mm²;Intel 4(原Intel 7nm)的晶体管密度则可达180 MTr/mm²。

其实我们不清楚Digitimes对于晶体管密度的计算方法。且在3nm芯片还没上市之际,不同研究机构对于3nm工艺的晶体管密度的公开数字也顶多是个估值。不过这张表中的值虽与Wikichip预估的值有出入,但其中的大部分是差别不大的。

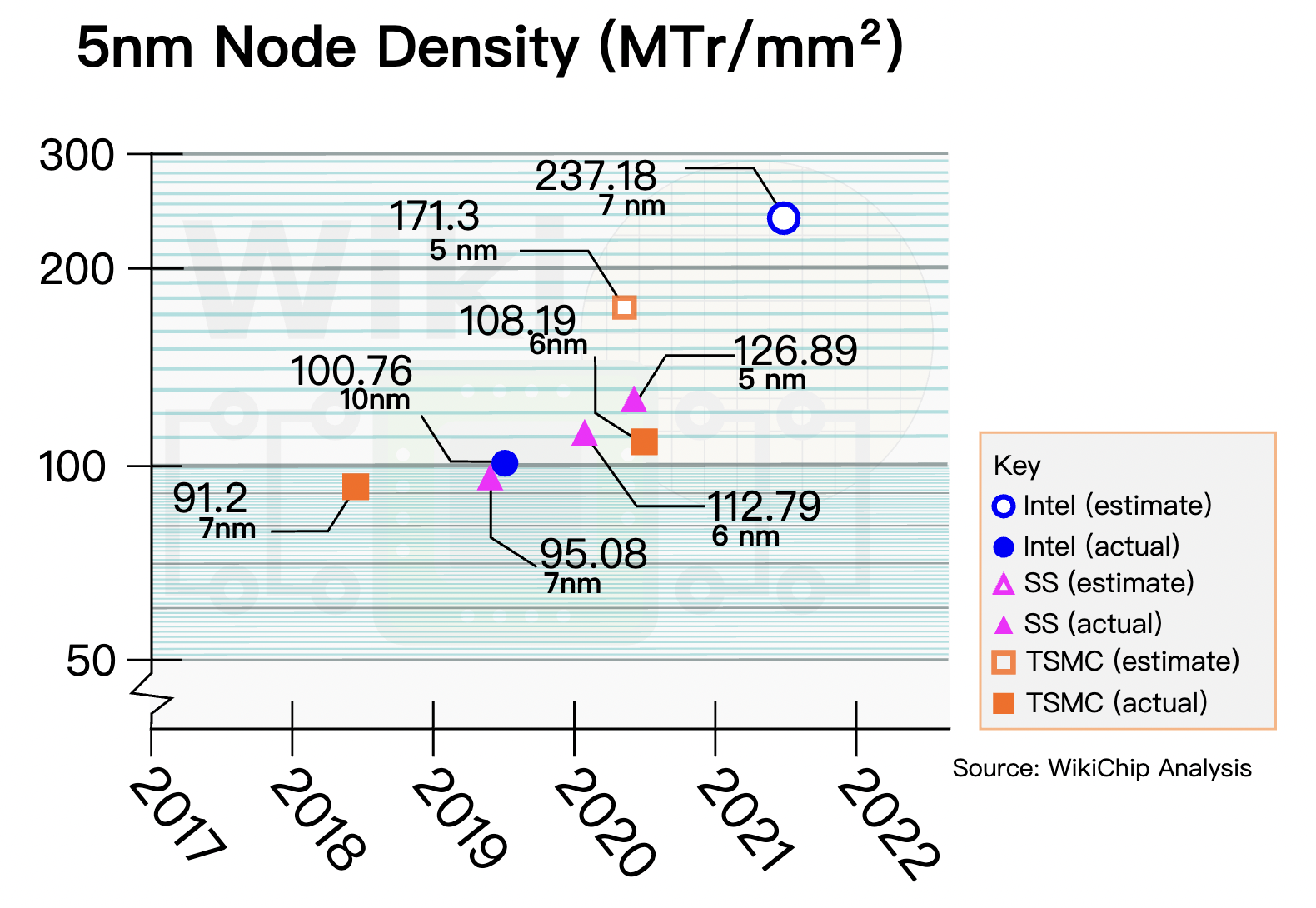

来源:WikiChip

Wikichip的数据,在7nm和5nm两代节点与Digitimes的数字相似的。不过Digitimes认为Intel 4(原Intel 7nm)的晶体管密度大约是180 MTr/mm²,Wikichip的数据是237.18 MTr/mm²(还有一些机构也预测了200+ MTr/mm²的值),这俩值相差还是比较大。

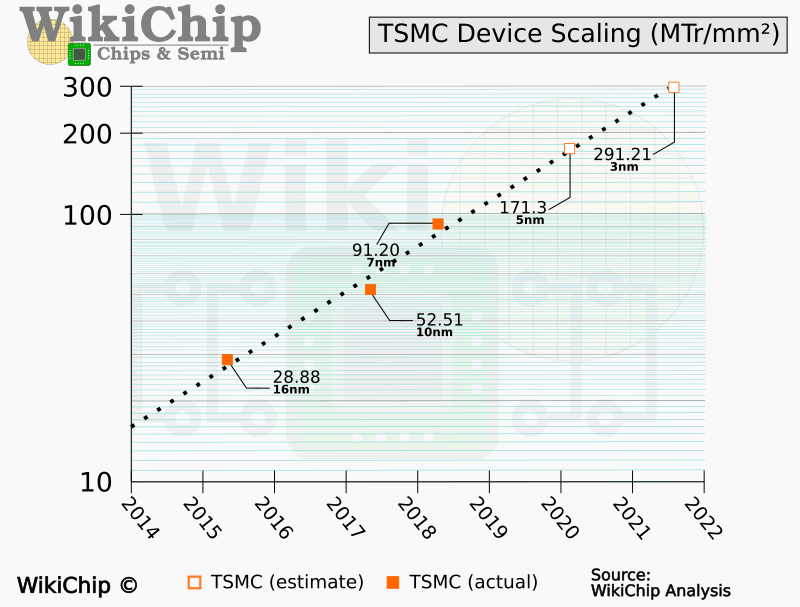

另外Wikichip去年年中预测,台积电3nm工艺的晶体管密度可以达到291.21 MTr/mm²,在Digitimes的这张表里看起来也差不多。不过Wikichip目前暂未公布对于三星3nm工艺晶体管密度的预估数字。如果真的只有表中170 MTr/mm²的程度,那么和台积电的差距就相当大了。

但我们还想再度重申“晶体管密度”的概念。晶体管并不是均匀排布在芯片上的,一方面类似手机SoC这样应用尖端工艺的芯片,其上逻辑、模拟和SRAM存储部分,这三者的晶体管尺寸及密度进化就是完全不同步的。我们现在常说的“晶体管密度”特指逻辑电路。

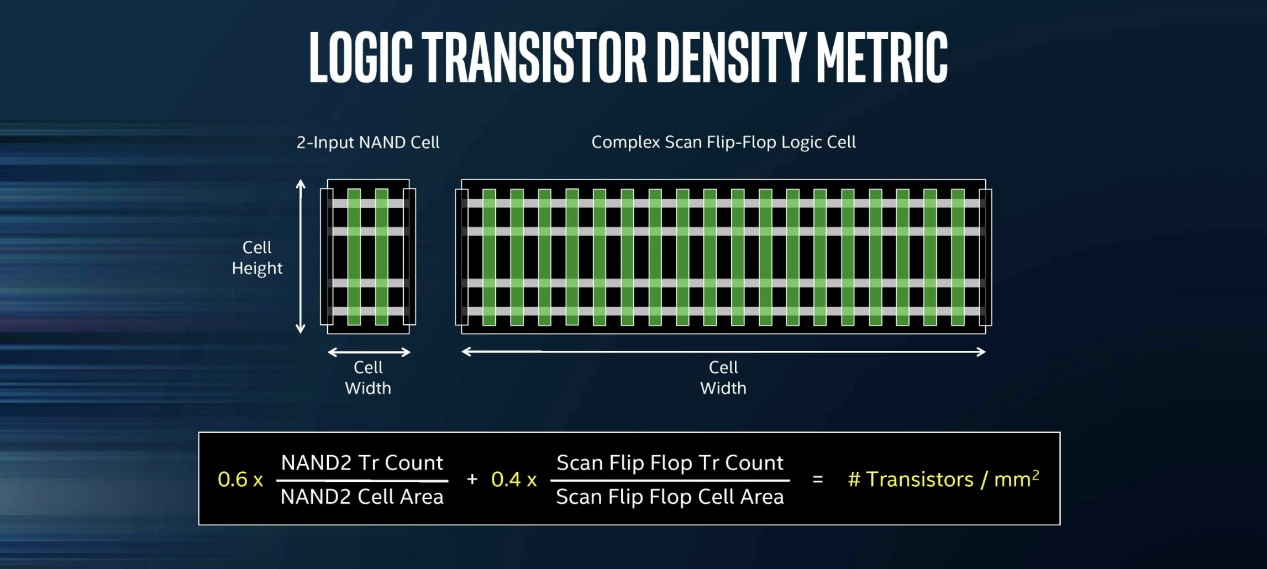

与此同时,即便都是逻辑电路,应用的单元库也是不同的——对于某一个节点的工艺而言,可能涉及到超高密度单元、高密度单元、高性能单元等——它们的晶体管密度就差异甚大。比如Wikichip说,台积电N7工艺晶体管密度是91.2 MTr/mm²,这是特指N7工艺的HD(低功耗)单元——实际上N7的HP(高性能)单元晶体管密度就只有65 MTr/mm²。

Wikichip选择的是此前Intel采用的晶体管计算方法,即选择每个标准库中都有的两种单元(4个晶体管的2-input与非门,与Scan Flip-Flop扫描触发器)密度做个加乘得到最终的一个值。这个值对于工艺先进性而言有一定参考价值,但几乎不能反映实际芯片的晶体管密度情况。

三星的3nm GAA晶体管

可以确定的是,三星是最先将要采用GAA(gate-all-around)FET晶体管的foundry厂。台积电要到2nm才会用这种晶体管,Intel也要等到20A节点,这两家近两年还将继续用FinFET晶体管。这可认为是三星3nm节点的先进性所在。

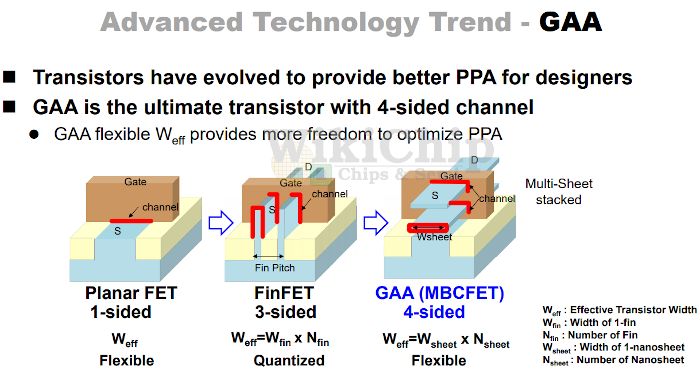

在 20nm 节点以前,行业都在用平面 FET 晶体管结构。而转向 FinFET 之后,这个“fin”极大增加了沟道的接触面积——上面这张图应该是来自三星(via Wikichip),有效沟道宽度(Weff)也就成为相关 fin 的函数——不过它也受制于 fin 数量(Nfin)。而从 FinFET 转向 GAA,就有更大的接触面积了,此前横置的 fin 数量更大的占地面积限制了 Weff,在 GAA 晶体管上就得到了缓解。而且 GAA 在功耗、性能的平衡选择上有更大的灵活性。

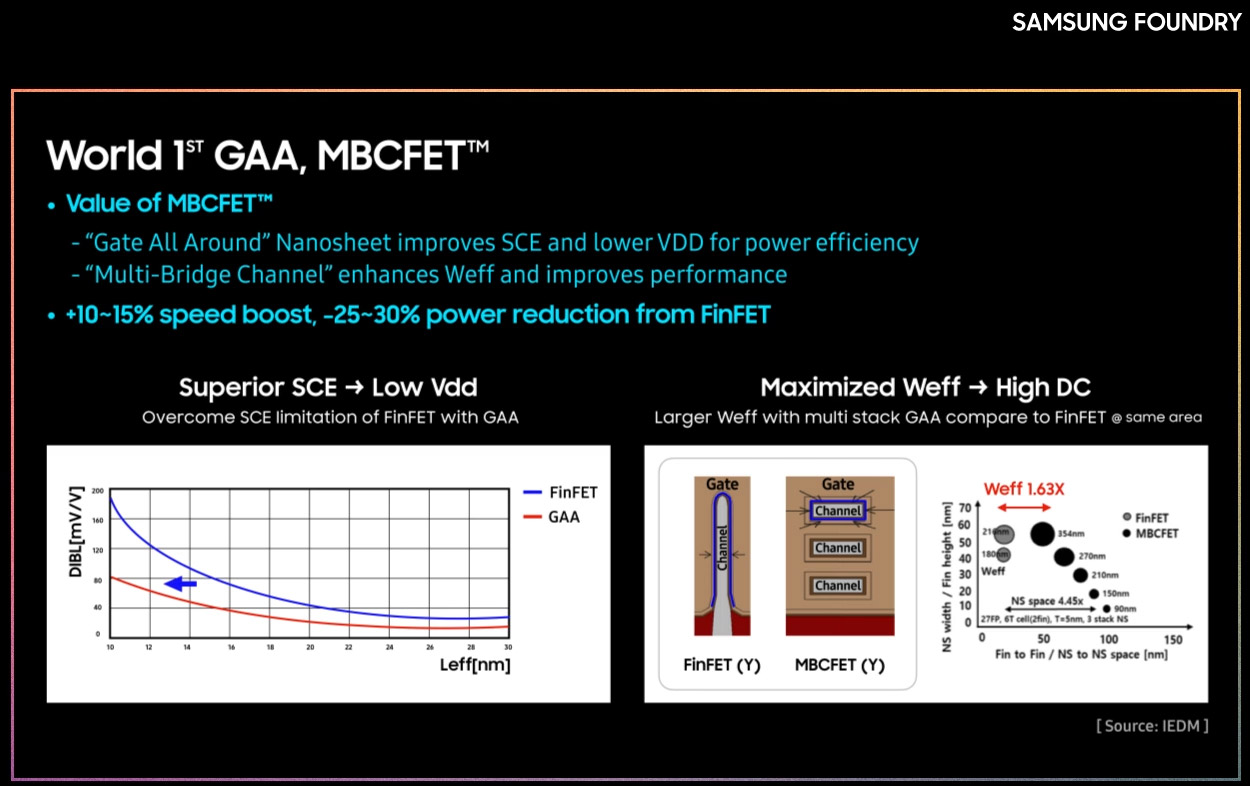

而且三星强调自己用的是nanosheet的MBCFET,每个堆栈达成更出色的电流表现,而且可弹性控制nanosheet的宽度达成不同的设计和目标。三星在去年的一场研讨会上说:“FinFET开启了移动SoC的新时代,我们相信MBCFET将引导数据中心时代,如高性能低功耗计算、AI和5G应用。”

不过三星对自家3nm获得的性能、功耗表现提升似乎在宣传数字上是摇摆不定的。去年三星提到相较7nm工艺,其3nm能够实现10-15%的速度提升与25-30%的功耗降低。注意比较的是7nm,而不是5nm(虽然在三星的路线图上,7nm和5nm都是同一个家族,而非完整迭代关系)。有可能是因为试产的3nm技术并没有那么成熟。

2019年三星宣布3nm的时候,最初可是说3GAE工艺可实现至多45%的芯片面积缩减,50%的功耗降低以及35%的性能提升的,对比的也是7nm。但在其去年上线的Green processes for green chips页面上,又说逻辑电路面积缩减25%,降低20%能耗,以及达成10%的性能提升。咱也不知道这些值是否基于同一个对比维度。但这其实很大程度表明了,三星对自家3nm工艺可能是缺乏信心的。

还有一点值得一提:三星4nm工艺在三星的路线图里,原本也是放在7nm工艺家族之下的(即三星7nm、6nm、5nm、4nm属于同一家族的同代演进);但不知为何(可能是为了宣传pitch scaling),去年更新的路线图里,4nm又变身为独立的一代完整工艺节点。给人的感觉始终是从最初于3nm节点的斗志昂扬,到逼近发布时间的信心逐渐缺失,乃至需要更早的工艺来填补市场空白。

不过去年年中,三星与Synopsys联合宣布首个基于三星3nm GAA工艺技术的高性能与多子系统SoC流片成功,大约是给了三星提振士气的依据的。去年的IEEE ISSCC 2021大会上,三星展示了其SRAM测试芯片,只不过并未透露任何具体的数字。

有关其3nm GAA技术更多已公开的信息,将放到本文的下篇去谈。

台积电N3:还是寂寞高手

2020年第一季度的earning call上,台积电首次谈及有关N3工艺的一些实质性内容。当时台积电表示N3将于2021年走向风险生产阶段,且目前状况一切良好。尤其强调了,基于成熟度、性能和成本优势方面的考虑,N3仍将继续采用FinFET晶体管。

魏哲家说FinFET也仍然有完整节点迭代的余地。与此同时,他当时还说预计2021年N3工艺的流片量会达到N5工艺第一年的2倍之数,所以对N3是非常看好的。

从晶体管密度的角度来看,台积电表示N3将作为N5之后的一个完整迭代工艺节点出现。N3相比N5实现了1.7倍的晶体管密度提升;在同功耗的情况下N3实现10-15%的性能提升,在相同性能的前提下功耗可降低25-30%。

单纯就这个数字来看,结合三星最晚公布的3nm GAA工艺提升数字,以及目前N5和5LPE的实际性能、功耗与密度差异,三星的3nm几乎可以说是被台积电3nm全面吊打的。(不信再回头去看看前文的数字)

其实去年台积电更新尖端工艺路线图的时候,也谈到了更多有关N3节点的细节信息,比如说单元库、SRAM与模拟电路部分的密度提升等。因为篇幅关系,这些内容我们也放到本文的下篇去谈。

最后顺带聊聊Intel 4,也就是文首出现那张图中列出的原Intel 7nm。去年的Intel Accelerated活动上,Intel宣布Intel 4将在同功耗下实现至多20%的每瓦性能提升。有关Intel 4的消息目前还非常少,比较重要的一则是Intel 4将是Intel首个将要采用EUV极紫外的一代工艺。

Intel在其10nm工艺(及Intel 7)节点之上,还在用传统的193i。虽说EUV对三星和台积电而言也用了至少2个完整节点了,但Intel表示随着EUV的进化,Intel计划采用最新的来自ASML的工具。“将要EUV应用于量产,需要围绕设备的整个生态。我们对于构建这套生态投入了大量努力。”其中mask-writing技术是Intel的优势技术所在。

另外在于Intel此前就表示行业内最早的high-NA(高孔径数值)EUV设备将为Intel所用,是Intel与ASML合作定义、构建、部署的。不过这样的设备需要2025年的Intel 18A工艺上才会正式投入生产制造。

即便不看最终疗效,就目前的市场前期宣传和有限的数据来看,台积电在2023年3nm时代的领先优势仍是不言而喻的。Intel的问题在于当前需严格按照此前制定的路线来做工艺迭代,则的确有较大的机会在2025年的2nm时代重回半导体尖端工艺制造的领导者地位。

三星Foundry目前的前景其实相对不乐观。他们的机会也在2025年的2nm节点上。三星的机会在于,这家foundry厂到2025年理论上应该已经在造第三代GAAFET晶体管了,相较台积电和Intel具备了更多的经验,或许有反超的机会。

本文的下篇将着重谈谈台积电和三星3nm工艺目前已公开的部分细节信息。

- 看上去像是军备竞赛,实际意义除了手机外,基本就是烧钱了。