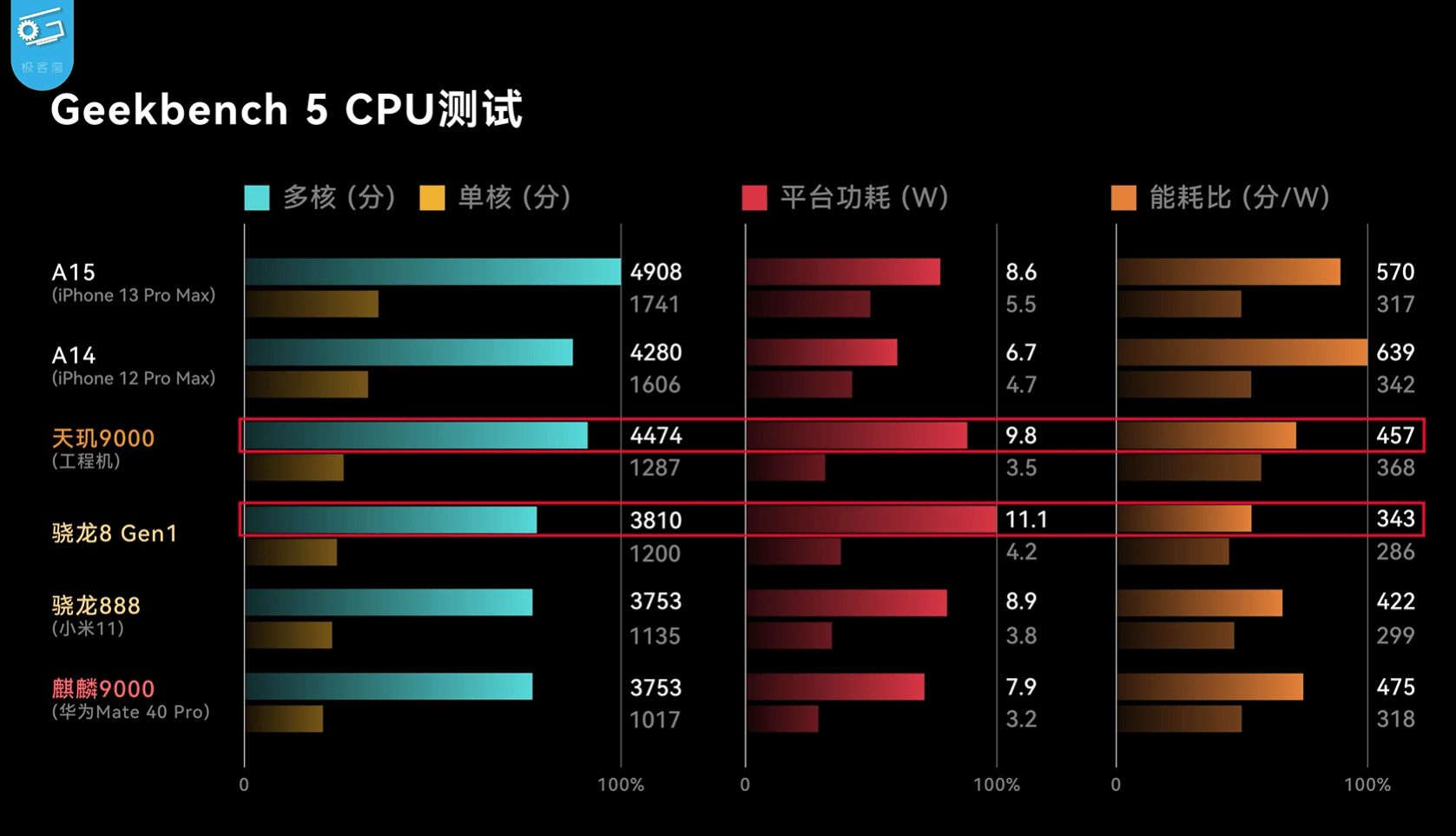

作为半导体制造尖端工艺的4nm之年的2022年,三星4nm弱于台积电4nm应该是在大部分人的意料之中的。这一点从发布还不久的高通骁龙8 Gen 1与联发科天玑9000这两款手机芯片,在能效方面的明确对比就能看得出来。

最近连SemiAnalysis都援引了国内极客湾的测试结果。这两颗芯片分别对应了三星4nm与台积电4nm,在CPU IP方面也比较相似(都是Cortex-X2、A710、A510组合)。但这两款SoC芯片之上的CPU所表现出来的功耗、能效却有着显著差异。当然这也未必都是工艺的锅,高通与联发科具体的设计在其中也占到相当的比重。

值得一提的是,从多个消息源来看,今年年中高通预计会上市一款采用台积电4nm工艺的高通骁龙8 Gen 2芯片——当属Gen 1的改款。届时来对比三星与台积电4nm,应该会有更具说服力的数据呈现。

明确两个4nm的定位差异

虽然我们无法从材料、结构等微观层面来细致对比两家foundry厂的4nm工艺,不过依然有一些宏观数据和产品路线等方向可明确两者的显著不同。

首先有个前置条件还是需要重申,尖端制造工艺所谓“5nm”“4nm”“3nm”这些数字,并不具有指代某个物理尺寸的实际意义。也就是说4nm工艺的晶体管,并不存在任何一个维度的尺寸是4nm,包括FinFET晶体管的gate length也并非真正做到了4nm。所以这里的数字只表明了foundry厂制造工艺的代际变化。

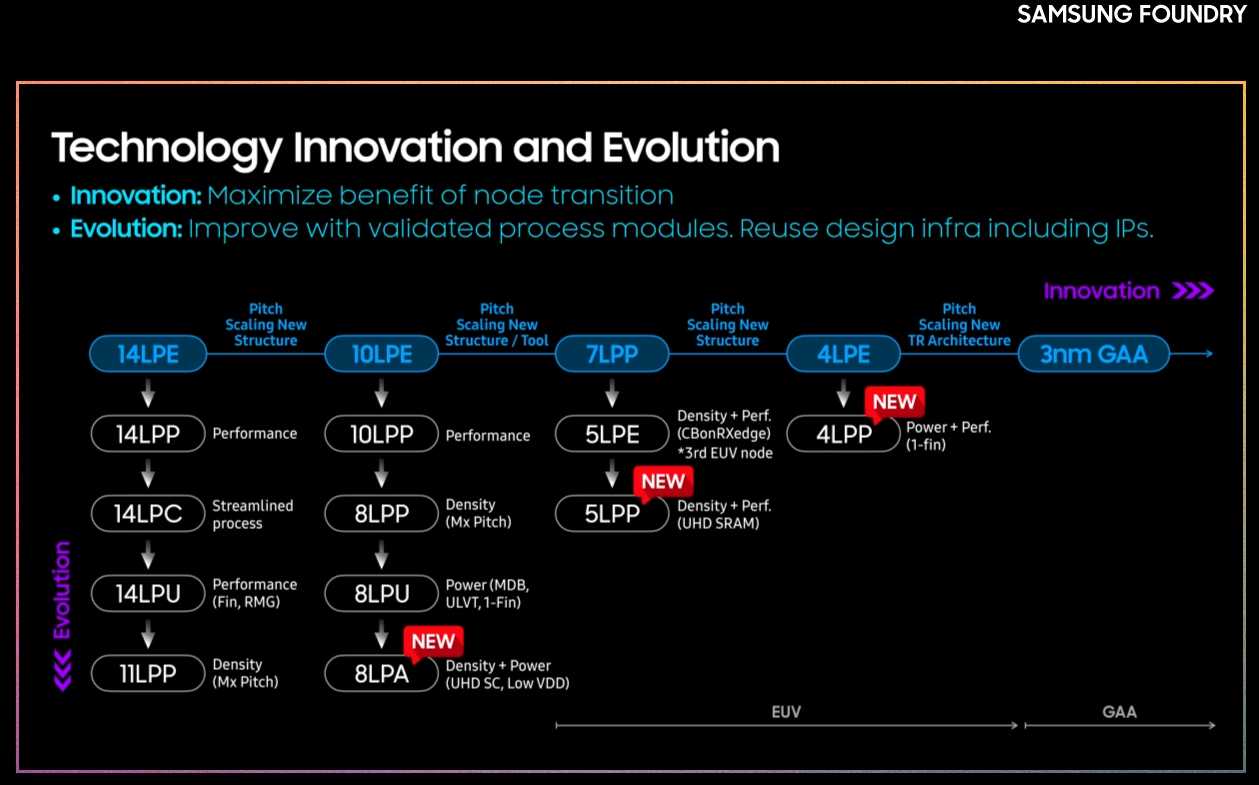

其次还要明确一个问题,就是4nm相对于5nm、3nm而言究竟是何种工艺定位?一般来说,对于完整(full)工艺迭代而言,工艺名称数字是以0.7倍为节奏进行演进的(严格遵照摩尔定律的话,应该是√0.5)。比如说14nm工艺之后,完整工艺迭代应当是10nm(14nm x0.7≈10nm),10nm之后是7nm,7nm之后是5nm。

按照这个规则演进,5nm之后是4nm还是3nm,在四舍五入规则下似乎得摇摆一下。不过主要foundry厂的约定俗成下,5nm的完整工艺迭代应为3nm。那么我们也默认了,4nm应当属于5nm→3nm的过渡工艺。其角色定位应该和8nm(10nm→7nm的过渡工艺)、6nm(7nm→5nm的过渡工艺)是类似的。

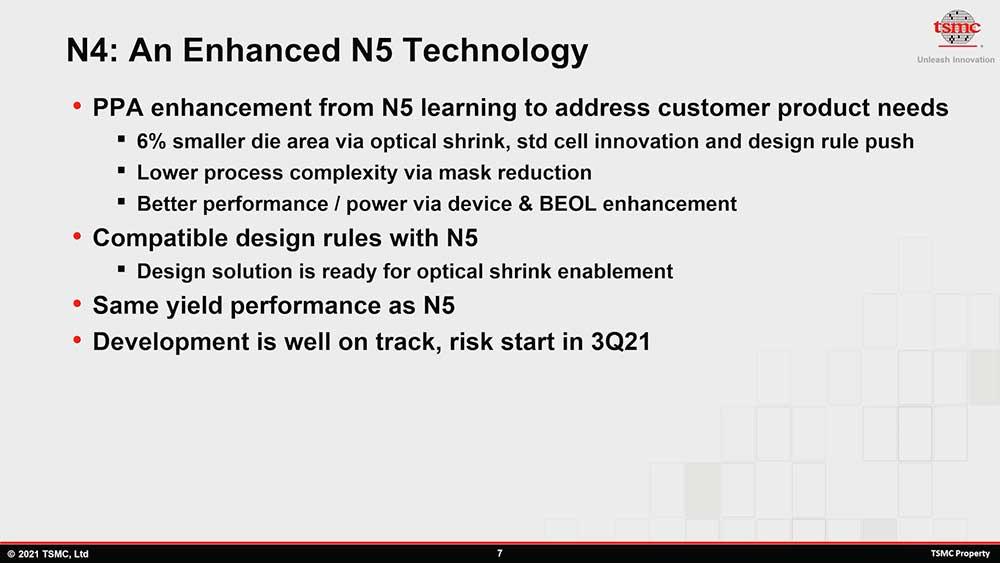

但实际情况已经变得复杂很多。对于台积电而言,上面的规则是完全适用的。台积电N7、N5、N3工艺都属于完整工艺迭代,N6、N4都属于过渡工艺,或者说N4本质上是N5的小改款。在所有foundry厂3nm工艺都延后的情况下,N4的价值在于填补这一时间段的市场空白。

三星这边的情况则略有些不同。此前5nm对比的文章里,我们就已经谈到过,在三星的路线图上5nm并不是其完整工艺迭代。三星5LPE属于7LPP的同代演进或改款。在三星后续调整过的市场规划中,4LPE才是7LPP的完整迭代。由于5LPE的演进幅度,以及4LPE在路线图定位上的不同,三星4LPE与台积电N4所扮演的角色实际上是有较大不同的。

究竟什么是工艺迭代?

这就衍生出了一个问题,就是以什么样的标准来判断工艺的“同代演进”和“完整迭代”?换句话来说,为什么说5LPE是7LPP的改款,而4LPE才是7LPP的迭代?为什么说N4是过渡工艺,而N3才是一个明确的代际?

一个比较简单的回答是:这是foundry厂自己决定的,foundry厂想叫它什么就叫它什么,因为反正5nm、4nm这样的数字也没什么现实意义。不过就目前的工艺更新情况来看,除了从设计规则兼容与否来做判断,似乎还有一条明确的规则可寻。那就是工艺的完整迭代,至少需要存在明确的pitch scaling。

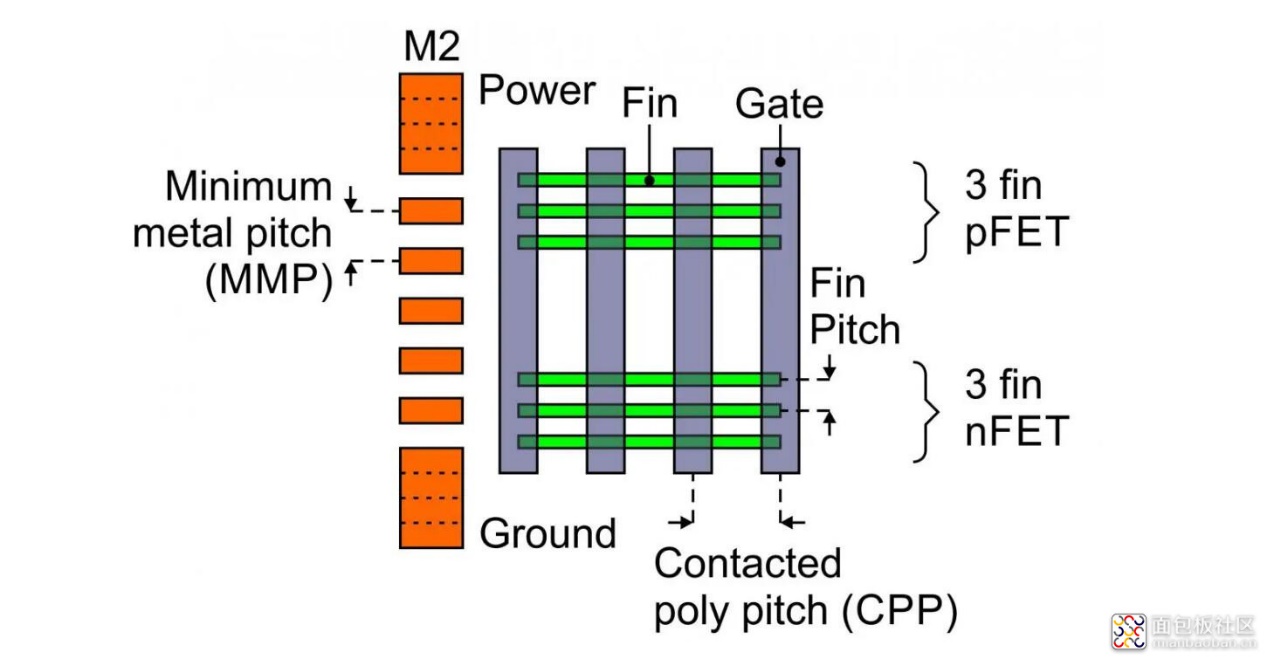

所谓的pitch scaling,可以简单理解为晶体管(及互联金属层)的物理尺寸变化。比如说对于FinFET晶体管而言,晶体管之间的最小fin间距要有变化,或者gate间距需要有变化,才能算得上工艺迭代。

比如说在Wikichip的数据库里,台积电N5工艺的MMP(minimum metal pitch,最小金属间距)为30nm,相比N7工艺的40nm缩减幅度为0.75倍;CPP(contacted poly pitch,一般可理解为栅间距)则从此前的57nm缩减至48nm,缩减幅度0.84倍。

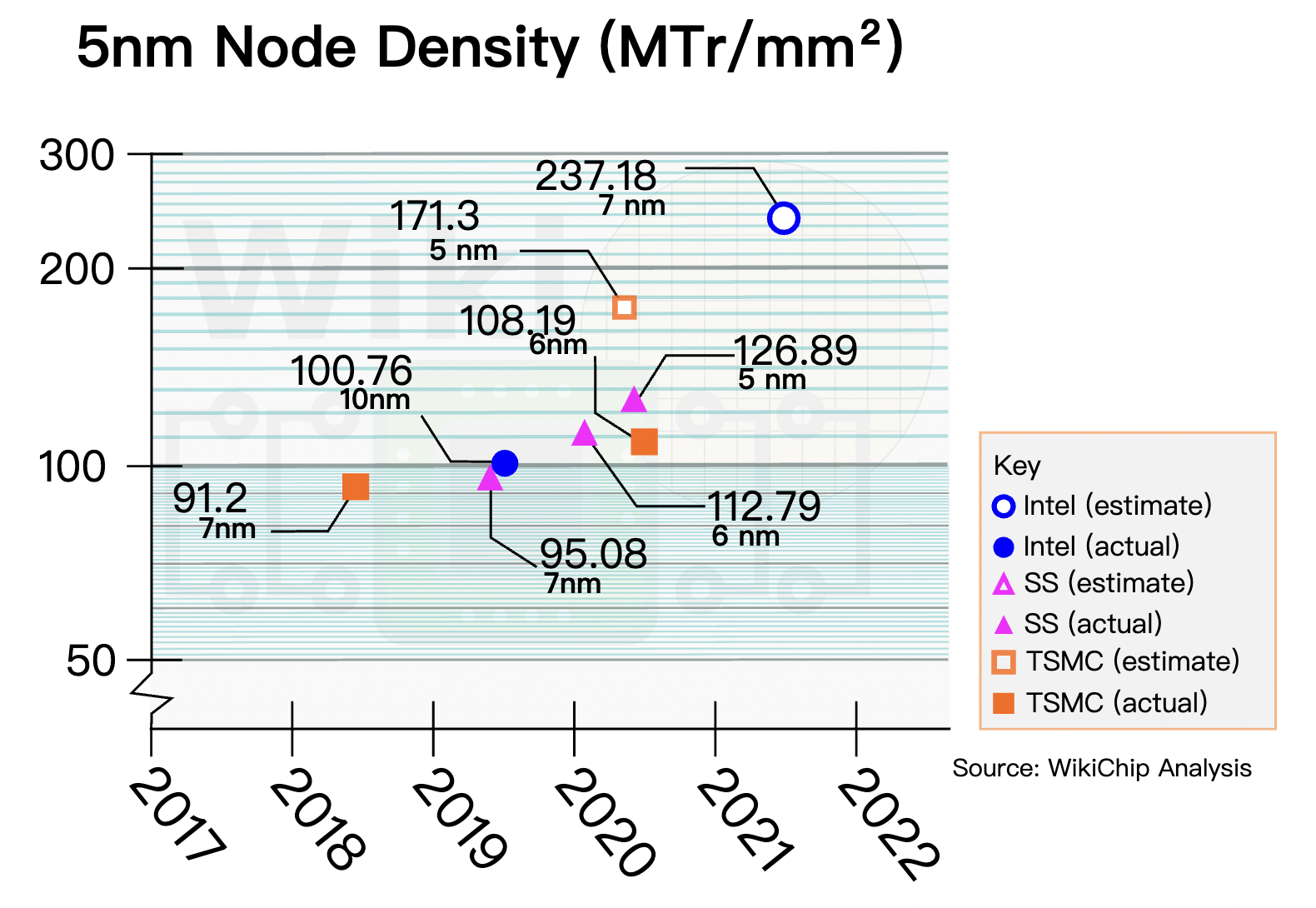

Pitch scaling因此就能带来晶体管密度的提升。那是不是也可以理解为晶体管密度提升了,也就意味着工艺迭代了呢?答案是不一定。实际上,三星5LPE相比7LPP,也是存在晶体管密度提升的;而且纸面上的提升数字还不小,Wikichip此前给出7LPP可达成最高的晶体管密度为95.07 MTr/mm²(特指HD高密度单元库);而5LPE的UHD超高密度单元则可以达到126.89 MTr/mm²的晶体管密度。

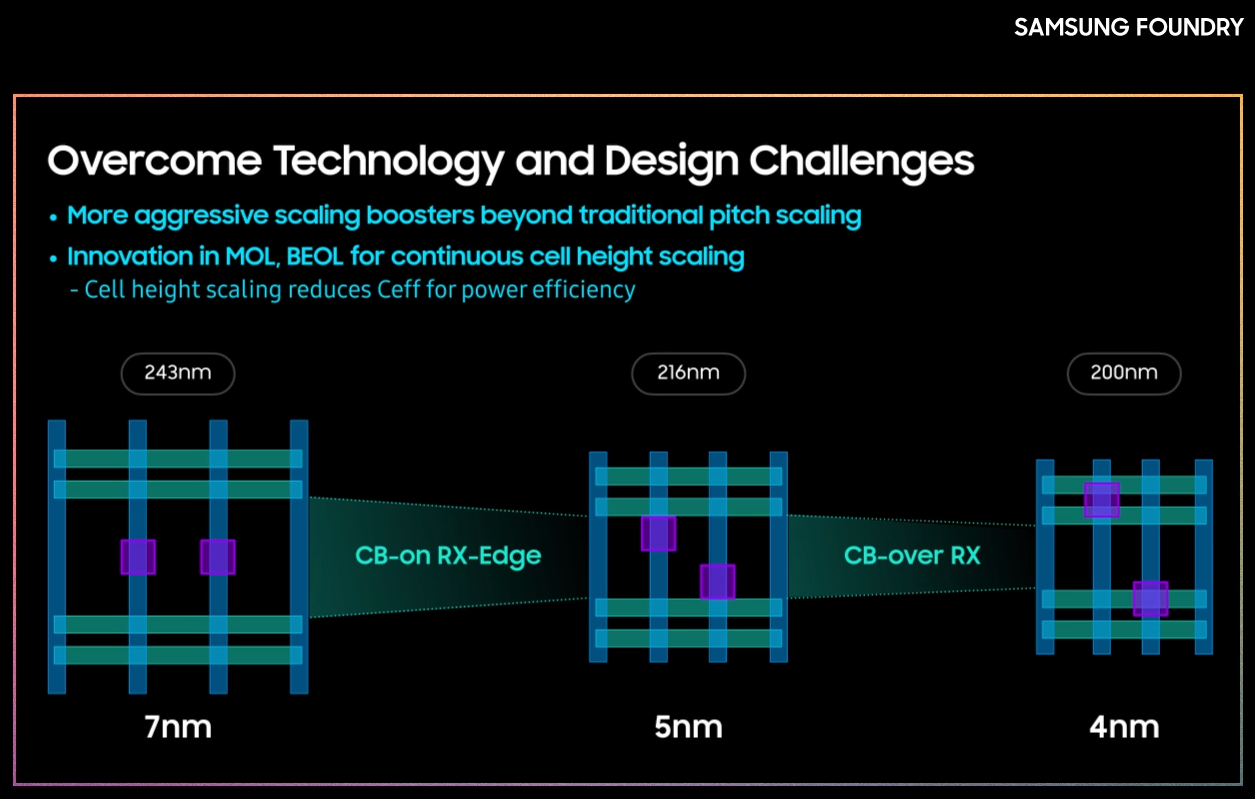

来源:Wikichip,这张图中的Intel 7nm后续已改名为Intel 4

即便有如此晶体管密度提升,三星依然把5LPE划归在7LPP工艺家族之下(而不算作一次完整迭代),这是因为5LPE基本没有做pitch scaling。那是怎么实现晶体管密度提升的呢?主要是一些被称作scaling booster的方案,也包括了单元(cell)层级的一些调整。比如说5LPE的UHD标准单元去掉了一个fin...不过这样的方案实际上也要求材料层面的改进,这些在以前的解读文章里都已经提过,此处不再赘述。

而4LPE相比7LPP则是存在pitch scaling的,虽然底层晶体管层面的变化比较小——Wikichip消息称,4LPE工艺的fin pitch从27nm缩减到了25nm,但并未得到三星官方确认。除此之外,金属层部分M1 pitch从40nm缩减至28nm,M3 pitch从36nm缩减至32nm。

所以4LPE哪里不如N4?

从这些信息,我们至少可以知道,虽然都叫4nm,但4LPE和N4对两家foundry厂而言却在定位上有着相当的不同。先于4nm工艺之前的5nm,N5就是领先于5LPE的,因为后者甚至都不能算是完整的工艺迭代。当时的同代芯片对比,麒麟9000和骁龙888的表现是很能说明问题的。

N4和4LPE其实很难做直接、明确的对比。大部分人关注的晶体管密度其实并不能直接说明问题——从材料到最终功耗、性能之类的表现上;而且高密度单元达成的理论最高晶体管密度,对电路设计的高性能部分价值也不大——因为芯片设计的关键路径并不会用这种高密度单元库。

我们可以来大致看看双方给出、和已知的一些数据。去年5月份,Wikichip给出对于三星4LPE工艺晶体管密度的预期为137.04 MTr/mm²。如果单从晶体管密度的角度来看,这个值其实还比不上台积电N5的171.3 MTr/mm²——台积电方面表示N4工艺相比于N5,还能够实现6%的die面积缩减(通过标准单元“创新”和设计规则变化)。当然我们也反复强调了,不应太过迷信晶体管密度;但这个值还是可以作为参考之用的,借此也能看到双方实质上所能达成极值的差距。

三星和台积电针对4LPE、N4还有一些其他数据。N4如前所述是N5的同代演进,相比于N5能够实现更好的面积效益。N4对台积电而言,比较重要的一个价值是缩减成本。因为N4用到了更多的EUV层,这样一来也就减少了工艺步骤和掩膜数量,或者说工艺复杂度更低。另外台积电还比较模糊地提到,通过器件和BOEL方面的提升,也能实现更好的性能和功耗表现(虽然这话约等于没说)。N4作为N5的延伸,整体设计规则实现了兼容性。

值得一提的是,去年10月台积电宣布N4会有个扩展的N4P工艺。台积电表示,N4P在性能方面会比N5提升11%,比N4提升6%;能效表现上,N4P相比N5则会有22%的提升。N4P相比N4,在晶体管密度方面应该不会有什么变化。预计N4P将于今年较早时间进入风险生产阶段,基于N4P的首款产品流片会是在今年下半年。

三星4LPE如前文所述,属于7LPP之后的完整迭代工艺,因为有pitch scaling和结构上的调整。4LPE是三星的最后一代FinFET晶体管工艺节点。上面这张图表征了4LPE在pitch scaling和单元结构上的变化(不过这张图的5nm呈现应该是夸张过的)——scaling booster包括MOL、BEOL方面的调整,实现单元高度的缩减。

另外4LPE后续有个同代演进叫4LPP,三星在宣传中提到相较4LPE会有5%的性能提升和10%的功耗缩减。

基于台积电和三星公布的这些数字,仍然很难对这两个工艺做微观上的对比。我们目前掌握的信息是N5原版工艺的晶体管密度依然远高于4LPE/4LPP。而且基于7nm、5nm时代双方的实际表现,以及后续台积电和三星宣传的4nm的性能与功耗表现变化,三星的4nm几乎无望和台积电4nm相比。

即便三星4LPE相比7LPP是一次工艺迭代,实际其较5LPE的变化却并不算很大;而台积电接着N7时期的领先优势,在N5节点上扩大了这种差距,并且对N5做改良后得到的N4也仍然得以领跑,步子走得相当稳。所以文首提到,骁龙8 Gen 1和天玑9000的表现差距是可预料的,只是没有想到这差距还略有点大(高通或许也需要为此担相当的责任)...

另外如我们此前的预期,三星3nm GAA晶体管虽将有结构上的大幅变动,但我们认为从三星当前公开的信息来看,这个节点的不确定性甚大,三星或将很难在3nm时代赶上台积电。三星真正的机会应该在2025年的2nm节点竞争上,届时三星将发展到第三代GAA晶体管。三星在GAAFET晶体管上积累的经验,是另外两个竞争对手暂不具备的。

半导体制造尖端工艺发展到如今,已经很难再凭藉厂商给工艺定的名字来判断其先进程度——所以Intel去年不是给自家工艺都改了名字么,也是在尖端工艺开发越来越难的时代之下,各家发展路线差异的反映。在迈入GAA时代之后,这种差异或许还会更大。

- 这边文章很专业啊

- 专业性有点强