引言

当今的功率变换器设计师正在努力寻找新技术新方法,以进一步提高变换器的效率极限和功率密度极限。基于宽带隙半导体技术的氮化镓(GaN)晶体管是目前最具潜力的技术方向之一。与硅器件相类似,单只GaN晶体管的电流处理能力仍有局限。在大功率变换器设计应用中,并联配置GaN晶体管是目前常用的解决方案。由于GaN晶体管材料和结构的特殊性,其并联配置方案与传统硅晶体管并联配置方案有所不同。

晶体管并联配置及驱动设计优化

理想情况下,在并联配置开关应用时,所用晶体管的通态电阻(RDS(on))需要严格匹配,以确保稳态电流在并联晶体管之间平均分配。同时,还必须考虑开关瞬态由于栅极阈值电压以及PCB布线阻抗不匹配等导致的并联器件之间的不对称性。配置不当可能会导致高频振荡电压,无法满足电磁兼容(EMC)要求,甚至导致晶体管损坏。

尽管传统硅晶体管的并联配置技术已经十分成熟,但对于GaN晶体管并联配置研究还鲜有涉及。并联配置GaN晶体管需要充分考虑到其高速开关特性所带来的优势和挑战。

英飞凌科技的CoolGaN 600V HEMT采用了栅极p型掺杂工艺,从而形成一个正向电压约为3.5V的pn二极管,并与栅极电容CG并联,其栅极驱动设计与传统硅晶体管有所不同。二极管将栅极电压钳位到其正向导通电压(VF),这意味着需要一个负电压来正确地关断晶体管。稳态导通和瞬态关断/导通期间所需的驱动也有所不同。

图1中所示的电路解决了上述问题。通过Ron的低阻抗、快速充电回路使器件导通,而RSS则决定了稳态二极管电流。当关断晶体管时,需要栅极负电压VG,可以通过确保Con大于CGS实现。

隔离型EiceDRIVER 1EDI20N12AF等单通道栅极驱动器是CoolGaN晶体管的理想驱动器。源极(OUT +)和漏极(OUT-)输出分别通过正确的电压实现晶体管的导通/关断,可确保晶体管不会误导通,即使在RC网络可能趋近于0V的低占空比下,也能保持VG的确定。

共享驱动电流路径对GaN晶体管并联配置的影响尽管每个并联晶体管都有单独的驱动电路,栅极驱动器环路(图2)中仍然存在部分共享路径,因为会有一些电流不可避免地从开尔文源极(Kelvin source)流出。即便存在毫伏级电压差也可能导致并联晶体管之间剧烈振荡。

在开尔文源极路径中加入高阻抗共模电感(CM)以及1Ω电阻能够解决这个问题。图3所示仿真结果显示了加入共模电感对共享驱动电流路径问题的抑制作用,同时共模电感并没有对栅极驱动器的驱动能力产生影响。

PCB优化设计

在GaN 晶体管高频和大电流应用时,PCB寄生电感和寄生电容可能会对晶体管开关运行产生影响,而在并联配置时其影响更大。但是,在SIMetrix中对CoolGaN晶体管进行仿真建模分析,在较小且对称的栅极驱动环路以及使用共模电感情况下,并联晶体管分流均匀与否仅与所选并联晶体管之间的RDS(on)差异有关。

积累实践经验

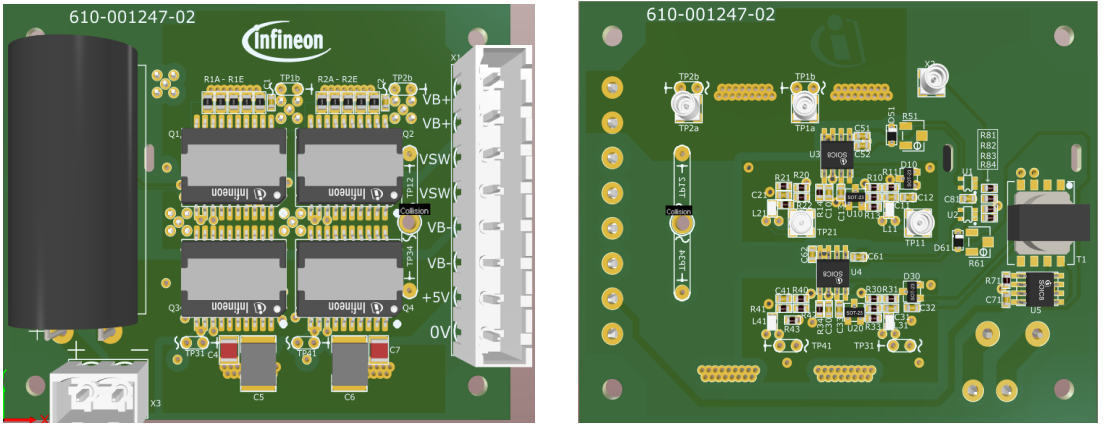

为了使工程师能够快速评估并联配置的GaN HEMT,英飞凌开发了具有四只70mΩ IGOT60R070D1 CoolGaN的并联半桥评估板。该评估板遵循以上讨论的设计准则,它能够提供大量的测试点。借助外部电感,该评估板可用于降压和升压模式测试以及双脉冲测试,还可以进行脉冲宽度调制(PWM)操作,并在高达1MHz频率或数千瓦功率水平下进行硬开关和软开关配置。采用合适的散热器,该评估板可以测试28A的连续电流和70A的峰值电流。

|

| 图4:并联半桥CoolGaN评估平台。 |

结论

在充分了解GaN晶体管栅极驱动电路后,可以相对轻松地实现GaN晶体管并联配置应用。其中最大的挑战来自于具体应用的高功率和高开关频率,而这些正是许多工程师采用现有硅器件时所从未经历过的。通过遵循良好PCB布局基本规则,在栅极和开尔文源极路径中使用共模电感,并平衡不同晶体管之间的电流,有助于最大程度地减小电压振荡。

作者:Yalcin Haksoz, 英飞凌科技首席工程师

责编:Amy Guan