电源转换或栅极驱动开关期间所生成的高压瞬态峰值可能有很大害处。在电动机驱动应用中,dv/dt瞬变可能会破坏绕组绝缘层,从而缩短电动机寿命并影响系统稳定性。在使用硅MOSFET、IGBT和SiC MOSFET的电路中,放缓瞬态响应的常见方法是提高外部栅极电阻的值。此类器件通常具有大反向传输电容(Crss)或栅漏米勒电容(Cgd)。在降低快速开关应用的dv/dt方面,提高栅极电阻(Rg)的做法十分有效。一个使用示例是图腾柱PFC,在此用例中,高dv/dt带来了较低的开关损耗。然而,在电动机等较慢应用中,要让dv/dt介于可接受范围内(例如5~8V/ns),所需电阻值会达到千欧级别。高Rg值可能会显著延长打开和关闭延迟。

本文重点而又全面地介绍了三种将dv/dt从45V/ns降至5V/ns而不会导致过长开/关延迟时间的方法:使用外部栅漏电容器、对器件增加RC缓冲电路,以及使用JFET直接驱动。在每种情况下,都是在T0247-4L封装中采用了一个1,200V SiC FET,且Rdson为9mΩ,并在75A/800V下开关。在探索每种情形时,都是先使用SiC FET的SPICE模块进行模拟,然后使用双脉冲电路实验测量打开和关闭时间,从而验证模拟结果。

使用外部Cgd电容

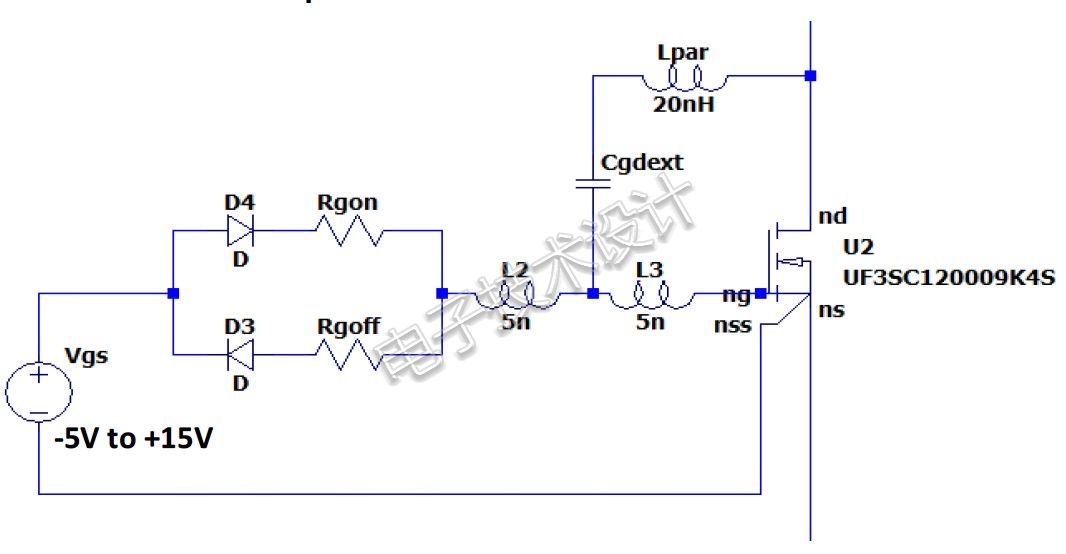

在此方法中,外部Cgd电容器Cgdext置于半桥配置的高侧和低侧FET的栅极与漏极之间,参见图1。

图1:带外部Cgd的栅极驱动,用于实现dv/dt控制。(来源:UnitedSiC)

对于SiC FET,Cgdext的计算值为68pF,而且在进行模拟时,电路中包含一个20nH的串联寄生电感(Lpar)。在使用分立器件而且Cgd电容器的连接位置尽可能靠近FET的真实情况下,该寄生电感可以小一些。如果使用FET模块,则电容器可能需要置于模块外,这表示寄生电感会接近20nH。

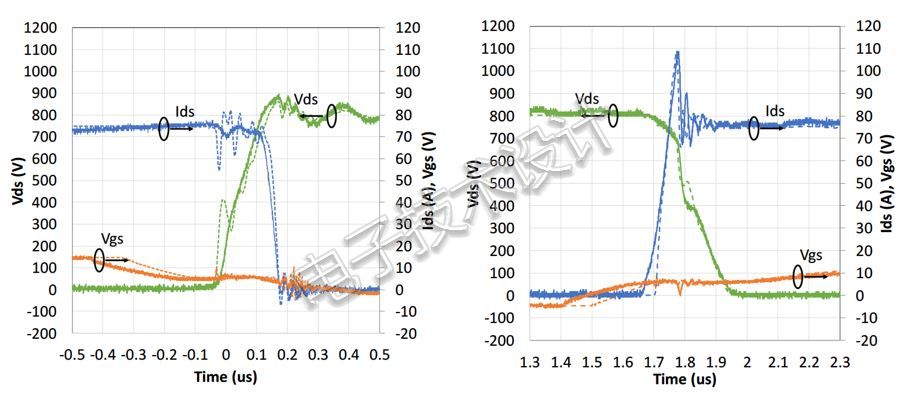

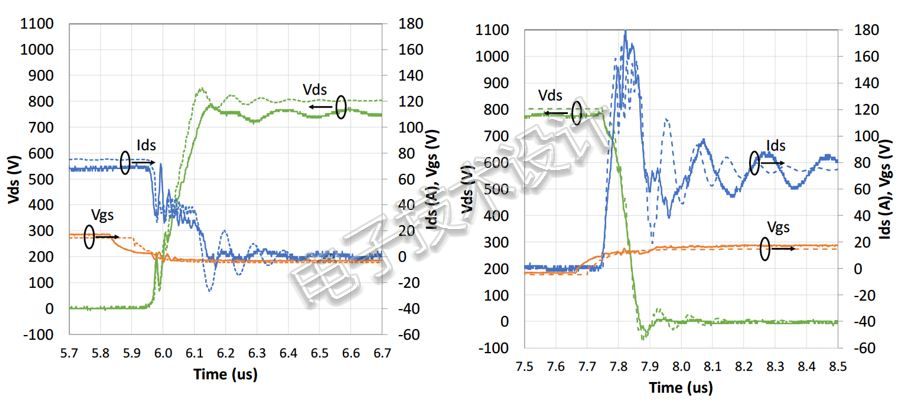

图2:使用68pF的外部Cgd电容器和33Ω的Rg。左边为关闭期间的Ids(蓝色)、Vgs(橙色)和Vds(绿色)值,实线为实验测量值,虚线为SPICE模拟值。右边为打开期间的值。请注意,本文全文都使用了上述追踪色约定。(来源:UnitedSiC)

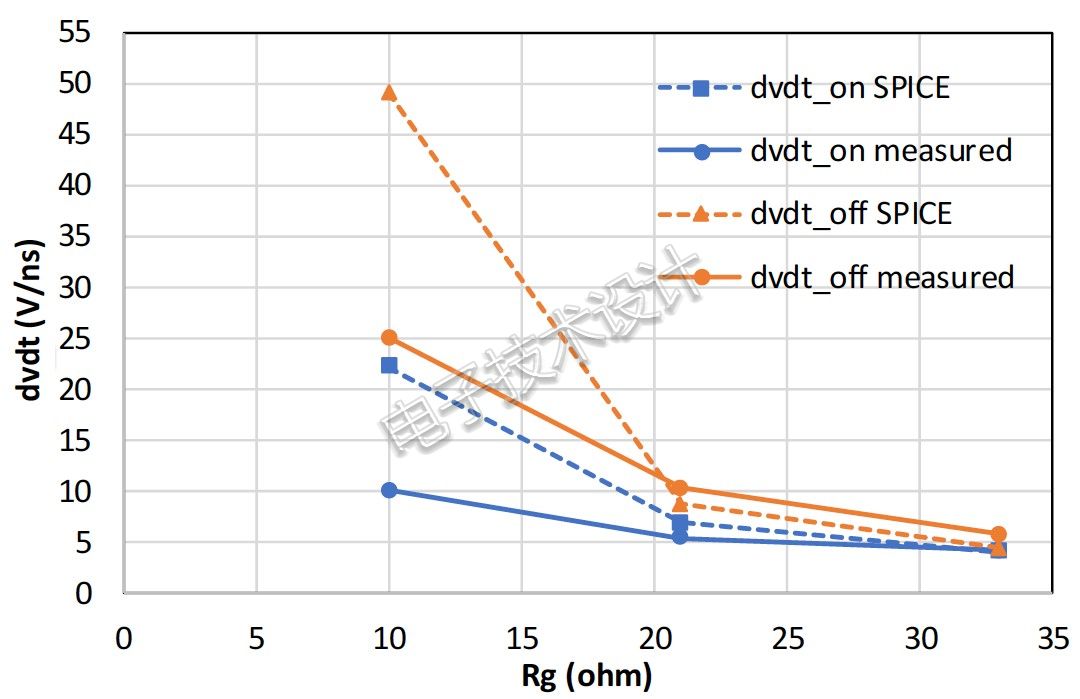

图2说明了外部Cgd电容器的SPICE模拟结果和实验结果。因为在开关期间,Ids相对较低,估计为0.54A,所以外部电容器可以容许20nH寄生电感。当使用68pF电容器且Rg介于10Ω至33Ω之间时,根据测量和计算,此方法的dv/dt介于25V/ns至5V/ns之间。参见图3。

图3:使用68pF外部电容器时,在实验和SPICE模块模拟情况下,依Rg而定的dv/dt图。(来源:UnitedSiC)

结果表明,当使用FET模块,将Cgd置于电路板上,且接受一定的寄生电感时,适合使用这种方法来降低dv/dt。

跨各FET使用RC缓冲电路

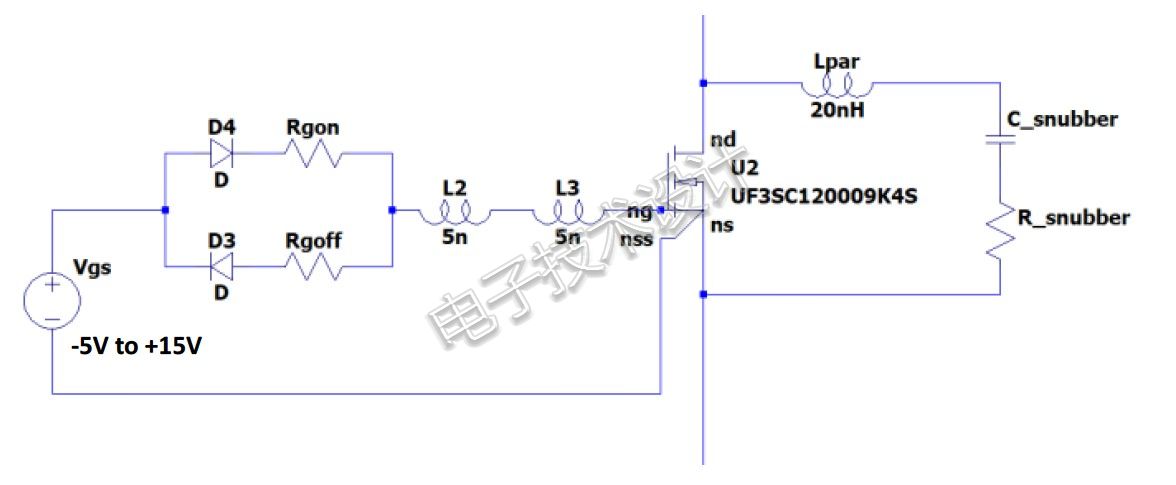

另一种控制dv/dt的方法是跨高侧和低侧FET的漏极和源极连接一个RC缓冲电路。参见图4。

图4:跨高侧和低侧FET并联的缓冲电路的示意图。(来源:UnitedSiC)

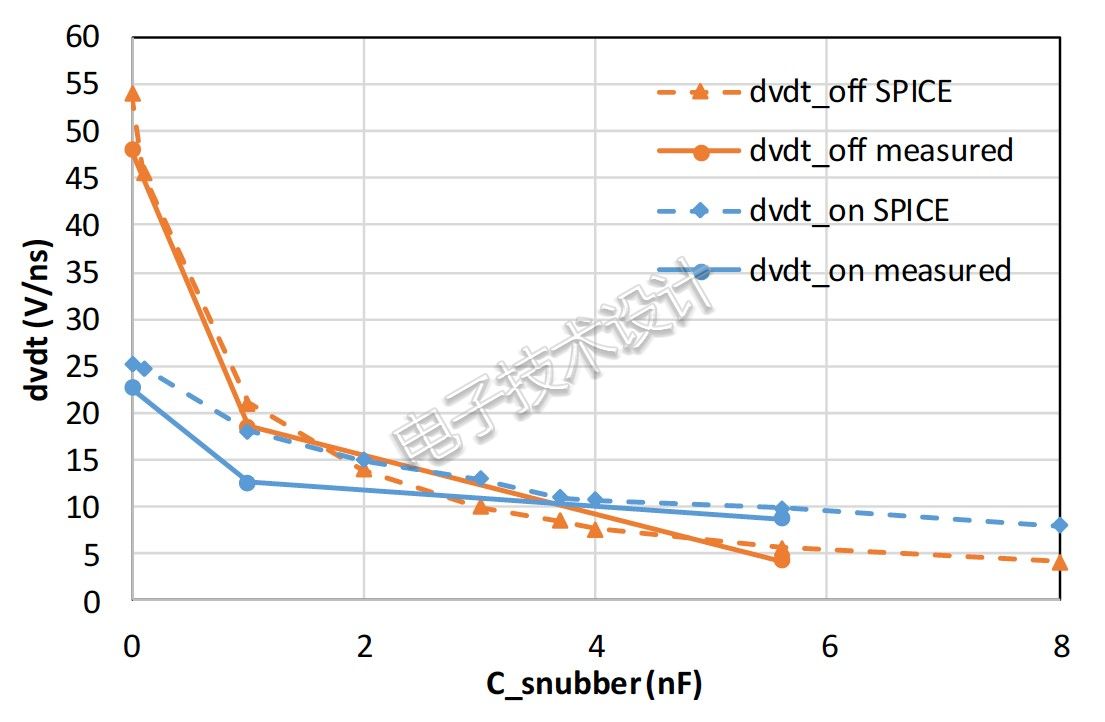

在这个示例中,如同外部栅漏电容器一样,电路中添加了一个20nH寄生电感,它与电容器(Csnubber)和电阻(Rsnubber)串联。当使用分立FET时,RC元件可以尽量靠近FET,理想的情况是直接与引脚连接,届时,寄生电感可以达到最小值。实验缓冲电路采用了一个5.6nF的电容器和一个0.5Ω电阻。SPICE模拟和实验结果均表明,这种方法可以将dv/dt从50V/ns降低至5V/ns。参见图5和图6。

图5:跨各FET的漏源使用RC缓冲电路。实验值以实线表示,SPICE模拟值以虚线表示。该测试在75A/800V栅极驱动下采用5.6nF电容器和0.5Ω电阻执行。左边为关闭波形,右边为打开波形。(来源:UnitedSiC)

图6:使用RC缓冲电路时,实验值和模拟值的dv/dt图。(来源:UnitedSiC)

由于电容值较低,增加缓冲电路带来的开关损耗非常小,在10kHz开关频率下仅仅约2W。相对较高的模拟寄生电感值(20nH)表明,RC缓冲电路的布置可能位于FET模块外,它可将dv/dt降低90%。

JFET直接驱动法

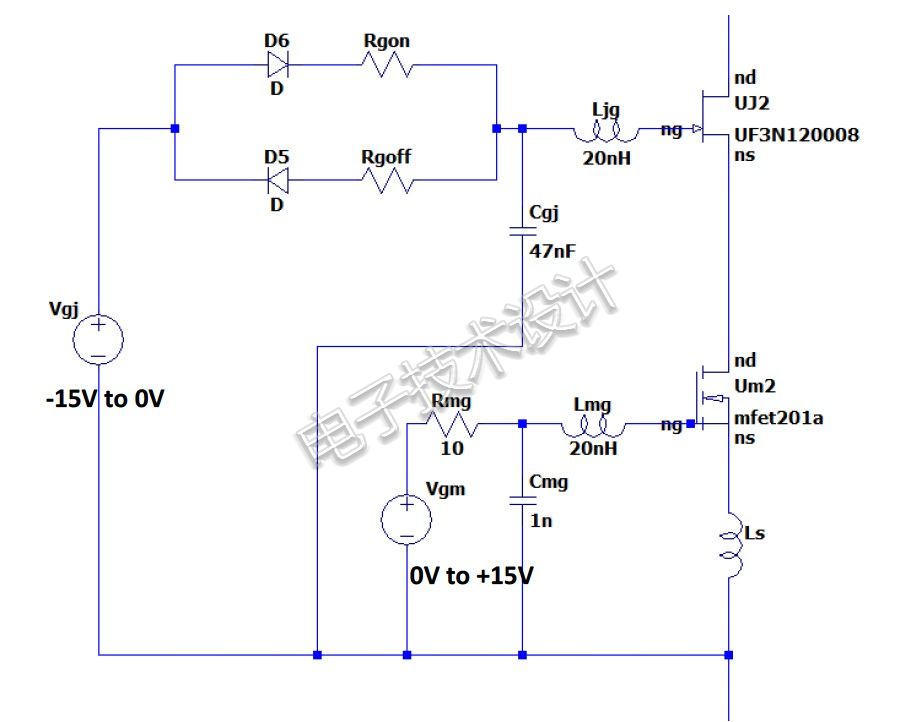

最后一种降低dv/dt的方法是使用直接驱动的JFET布置,参见图7。在这种电路中,启动时即打开Si MOS器件,且JFET栅极电压介于-15V至0V之间。

图7:直接驱动的JFET布置。(来源:UnitedSiC)

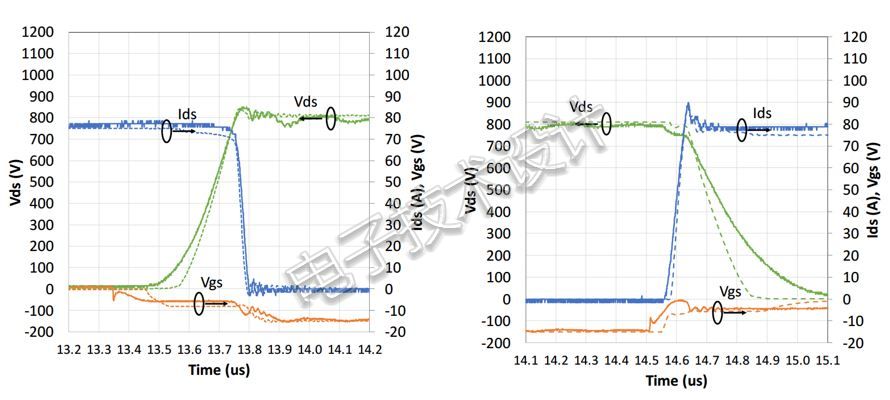

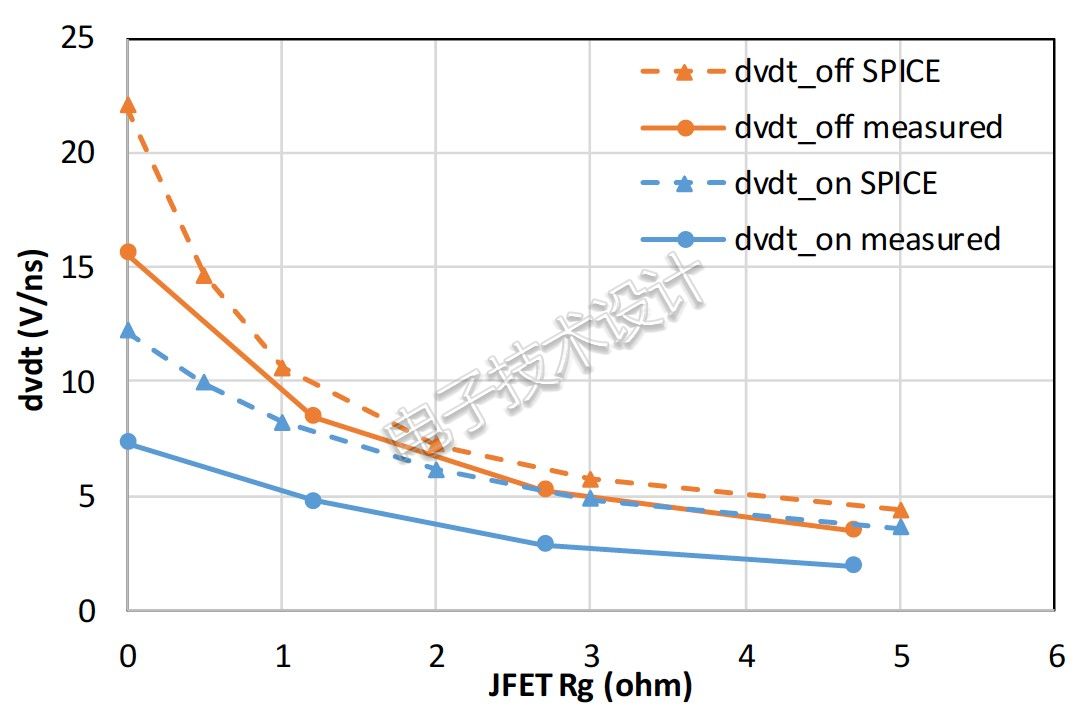

这需要PWM栅极驱动信号和启用信号,但是要维持常关状态。高侧JFET栅极电压为-15V,以保证在开关瞬态期间,它为关闭状态。同样,使用实验设置进行测量,并用SPICE模块进行电路模拟。结果请参见图8和图9。由于SiC JFET的Crss(Cgd)大,一个4.7Ω的小Rg就足以将dv/dt降低至5V/ns。

图8:使用JFET直接驱动法。实验值以实线表示,SPICE模拟值以虚线表示。左侧为关闭波形,右侧为打开波形。采用75A/800V电路,Rg为4.7Ω。(来源:UnitedSiC)

图9:采用JFET直接驱动法的dv/dt图,显示了实验波形和SPICE波形。(来源:UnitedSiC)

表1:三种dv/dt降低法的SPICE模拟性能摘要。(来源:UnitedSiC)

结论

表1重点介绍了在75A/800V电路中降低dv/dt的三种不同方法的SPICE模拟预测值摘要。在三种方法中,JFET直接驱动法的能耗最低。不过,直接驱动法需要-15V驱动信号和启用信号,增加了元件数和电路复杂性。外部Cgd电容器法和RC缓冲电路法的开关损耗略高,但是不需要到JFET栅极的通路。如使用分立FET,则这两种方法都可以在电路板上轻松实现。标准UnitedSiC FET不提供到JFET栅极的通路,但是采用TO247-4L封装的新双栅极产品已经在开发中。这种方法还适合与添加了JFET栅极引脚的模块配合使用。在所有情况下,SPICE模拟中都计入了20nH寄生电感的影响,结果证明,一定量的电感不会影响dv/dt的降低。

RC缓冲电路法的突出特点是无法分别控制打开和关闭dv/dt,参见表1。然而,由于Rgon和Rgoff电阻分离,Cgd法和JFET直接驱动法可以分别控制这二者。

本文展示了三种显著降低dv/dt的方法。鉴于UnitedSiC FET的低导电损耗和短路条件下的稳健特性,采用UnitedSiC FET能让这三种方法成为电动机驱动开发中高效且可靠的选择。

作者:李中达博士,资深研发工程师,UnitedSiC公司

(原文链接:3 methods to minimize harmful dV/dt transients in switching circuits,由赵明灿编译)

本文转载自《电子技术设计》网站