专用集成电路的应用使电流监控变得越来越简单。各种电流监控集成电路随时买得到,而且多数情况下都工作得很好,还有各种仪表放大器也是如此。使用分立元件构建电流监控器似乎显得多余,然而在某些情况下,特别是在有现成的低压元件时,使用分立元件的电路来进行电流监控可能是最好的方法。

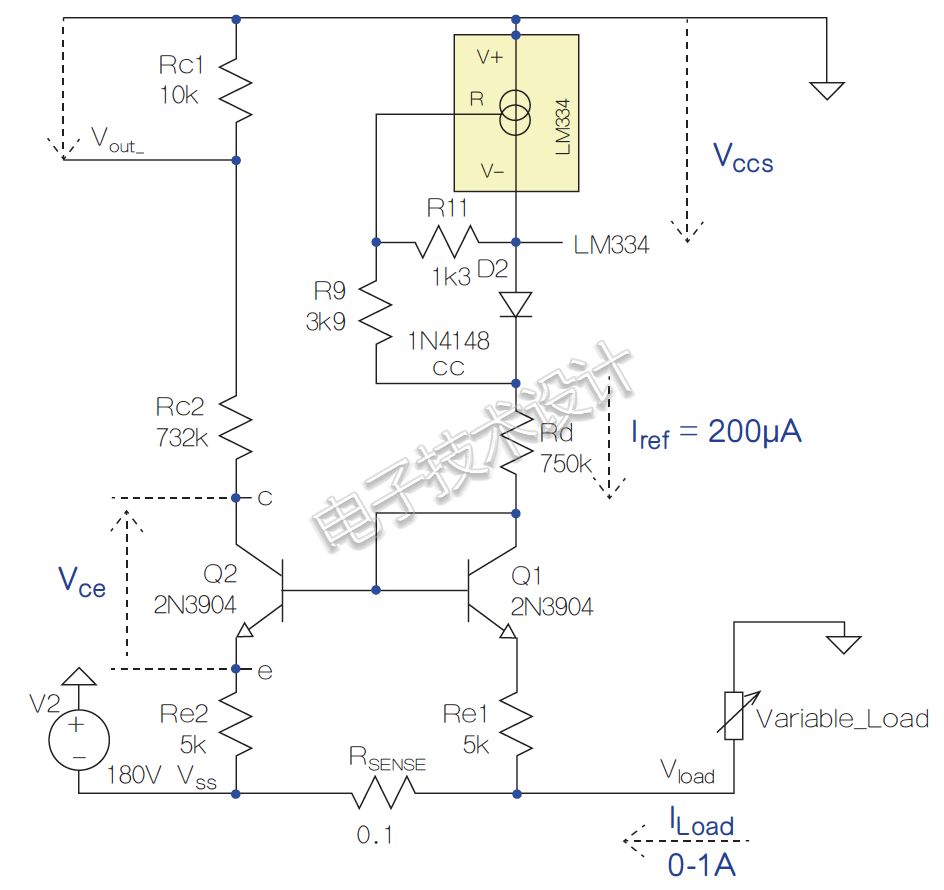

本设计实例中的电路用于监控伺服系统+180/−180V电源的两个电源轨中的电流。图1显示了用于监控负轨的电路相关部分。监控正轨的电路只需用PNP设备替换NPN即可。采用价格便宜的双晶体管和1%电阻来设置Iref以及Re1和Re2可获得最佳效果。Rsense应为0.1%并且具有足够的额定功耗。

图1:负轨监控电路。

图1所示电路和所有类似拓扑结构的设计灵感均来自电流镜拓扑结构,以及Re2上的电流随Rsense上的电流、Rc1上的电压随Rsense上的电压线性变化的这个概念。

该电路的作用依赖于Re1和Re2。让Iref相当小而Re2和Re1相当大,当Re2和Re1的值相等时,相对于Rsense上的电压,发射极的电压将增加。当负载在无负载和满负载之间变化时,这将反过来减小输出设备上Vce的变化。

因此,审慎而明智地选择Iref、Re1、Re2、Rc2和Rc1可以防止Q2进入饱和状态并且不会超过晶体管的最大工作电压。请记住,hoe=I(集电极)/VA(早期电压)意味着减少Ic的变化也会减少β的变化,从而改善线性度。Rc是Rc1和Rc2之和,因此比率Rc1/Rc确定无负载时Vout−处的偏移。满载时Rsense上的电压决定了Re2和Rc1的电流变化,从而决定了Vout−的满量程输出。一旦Iref值建立,就可以很容易计算出Rc和Rd上所需的无负载电压。通过使用发射极电阻,可以显著降低Vce变化对Q2的β的影响,而且从仿真数据可以看出,β的变化对负载电流和输出电压之间相关性的影响相对较小。鉴于这些结果,采用类似于Wilson电流镜的配置似乎并没有必要。

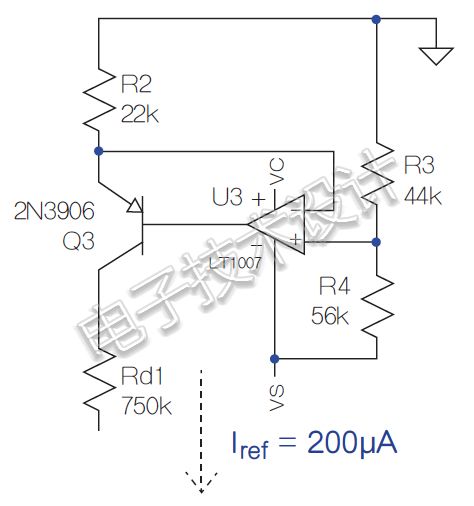

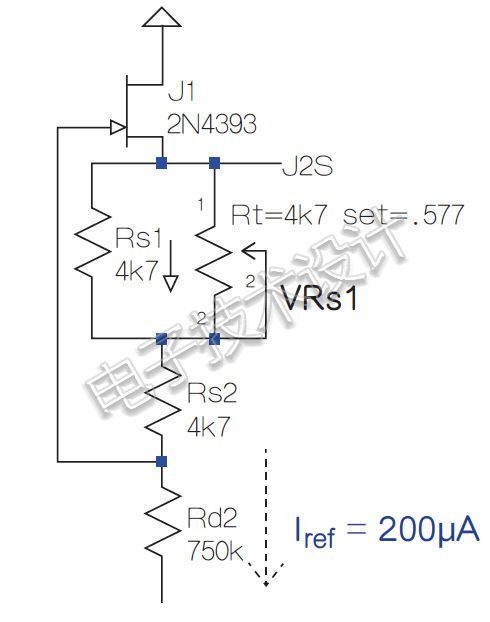

图2和图3显示了用恒流源产生Iref的替代解决方案。如果Vss稳定且没有纹波,则可以省略恒流源发生器,并且可以通过设定Rd值来提供Iref。

图2:用恒流源产生Iref的替代解决方案。

图3:设置FET偏置,使启动时Iref不会导致Vce或Vds超过最大值。

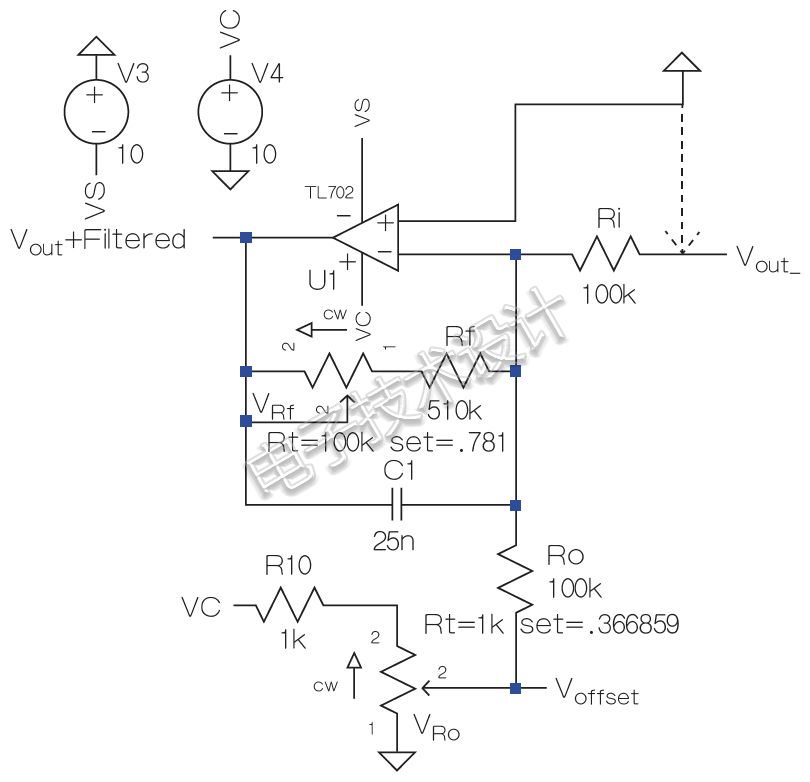

图4所示的电路反转了Vout-,消除了偏移,并将输出调整到所需范围,同时还可以过滤输出端出现的电源纹波或负载尖峰。若配以带有ADC的微控制器,则可以将电路简化为仅反转Vout-。

图4:反转Vout-消除了偏移,将输出调整到所需范围,并可以过滤输出端的电源纹波或负载尖峰。

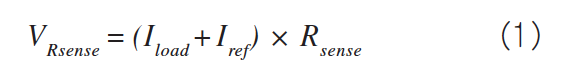

如果满载时VRe1至少比VRsense大10倍,那么Q2将不会进入饱和状态,并且:

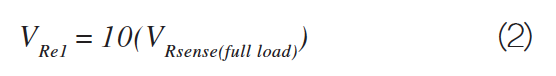

Iref=IRe1,无负载,即Iload=0,那么:

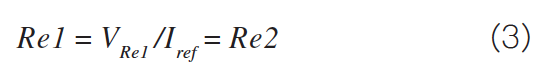

Vccs是恒流源两端的电压,IRe1约等于Iref,Vbe可以为0.6到0.65V:

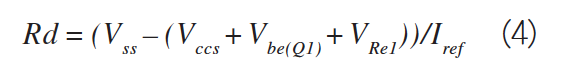

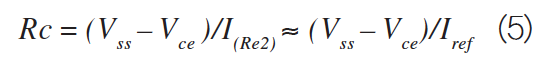

Vce是Q2上无负载时所需的最大电压。IRe2约等于Iref,那么:

Vout-无负载时所需的失调电压决定了Rc1的值:

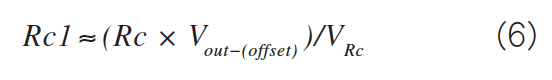

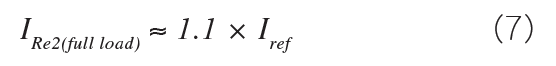

由于I(Rsense)=Iref/10,因此可以估算满载时的IRe2:

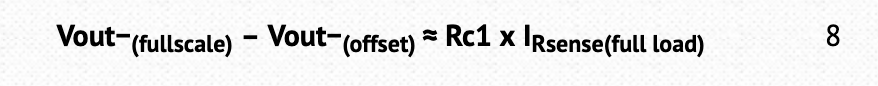

在最大负载电流下,Vout−的满量程值约为:

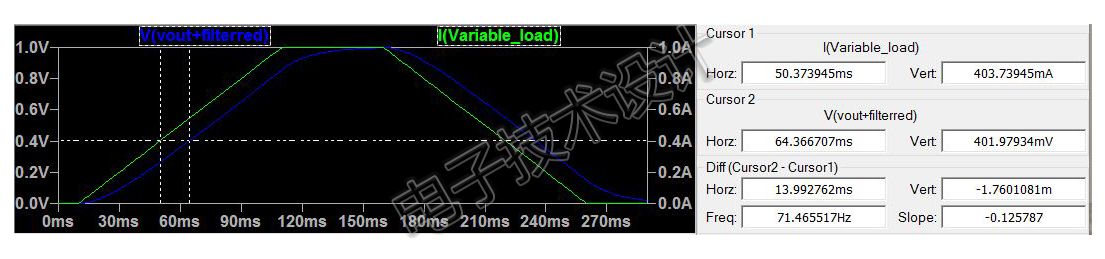

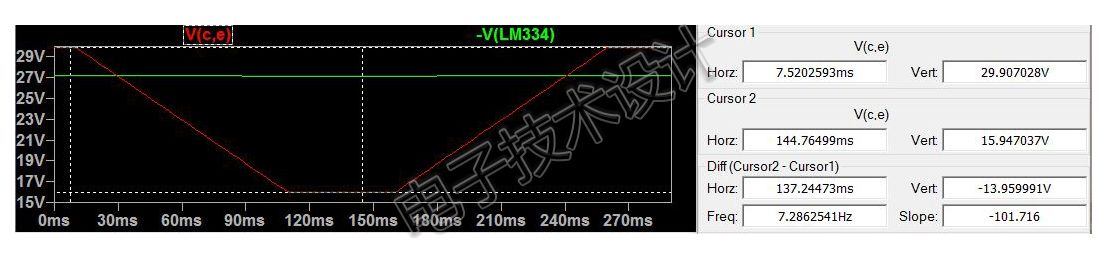

采用LTspice电路仿真软件产生图5、图6和图7的曲线,以显示电路工作期间的线性度、滤波效果以及Vce和Vds。负载电流从0增加到1安培,输出电压叠加在负载电流上。其结果与实际的电路性能非常接近。

由于负载电流尖峰值持续时间短,滤波防止了跳闸。隔离虽可能没有必要,但在设计高压电路时应始终予以考虑。

图5:将图4中25nF的电容C1去掉后的Vout。

图6:图4中加上25nF电容C1时的Vout。

图7:有源设备上的电压。

(原文刊登于ASPENCORE旗下EDN英文网站,参考链接:High-voltage current sensing with low-voltage transistors。)

本文转载自《电子技术设计》网站