此前我们花相当多的篇幅探讨过业界主流的10nm、7nm、5nm工艺,感觉探讨的广度还是基本到位的,虽然可能现在回头看有些地方存在一些贻笑大方的错误。不过跟进这些尖端制造工艺,对理解整个行业也是有价值的。

在3nm技术还没有特别系统、通俗的呈现,也尚无芯片成品出现之前,可以来谈谈3nm之前主要尖端半导体制造厂的制造工艺:其实也就是三星和台积电,毕竟对标台积电、三星5nm的Intel 7nm到现在也还没影。尖端工艺市场玩家减少,对我们探讨这类话题感觉也是极有好处的。

恰好前不久台积电也在一年一度的Technology Symposium之上更新了接下来的工艺规划;三星此前也谈到过3nm之前的工艺路线。借此机会我们做个简单的汇总,虽然可能在信息呈现上会比较零散。

在此之前,仍然建议有兴趣的同学阅读目前活跃在市场上的半导体制造工艺解读文章——其中Intel 10nm工艺上篇作了比较详细的有关工艺技术的科普:

当代尖端工艺技术更新

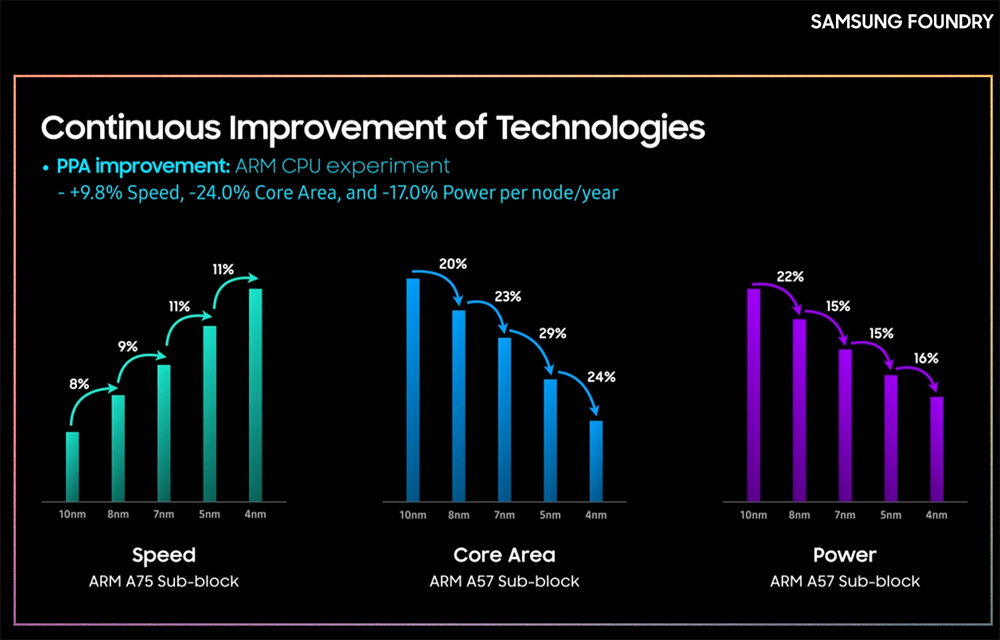

三星在IEDM 2020上给出了从10nm到4nm这几代工艺节点性能、面积、功耗上的变化。这个对比是基于相同的处理器核心IP(Cortex-A75/A57),应该是在逻辑电路上颇具代表性的。虽然下面这张图的柱状条也存在不成比例的问题,不过从中还是能够看出这些年半导体尖端工艺的演进,每年工艺迭代平均让性能提升了9.8%,CPU核心面积减少24%,功耗降低17%。这张图或许也能作为行业进步的大方向来看:

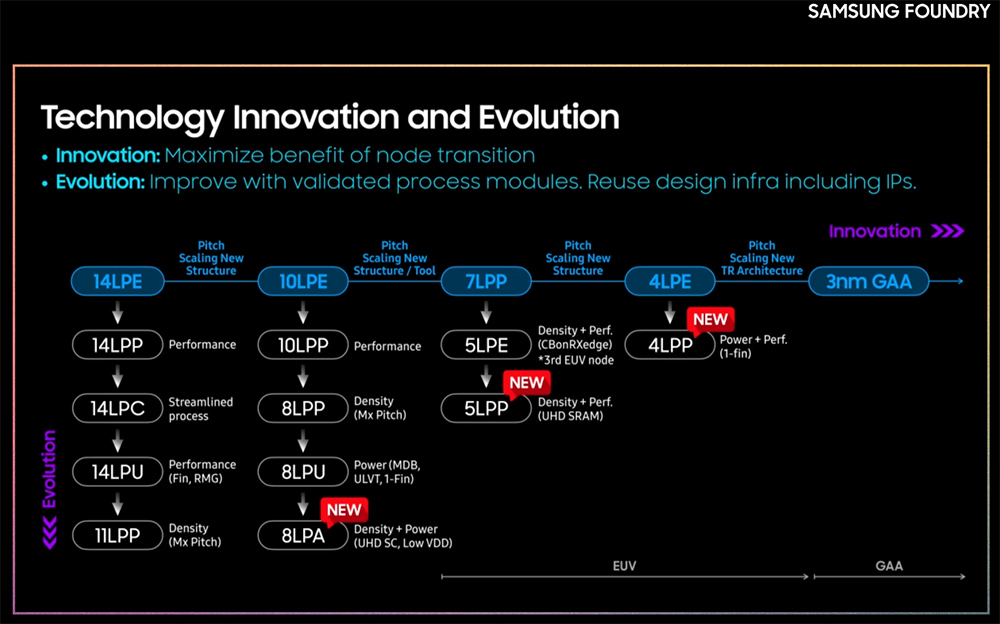

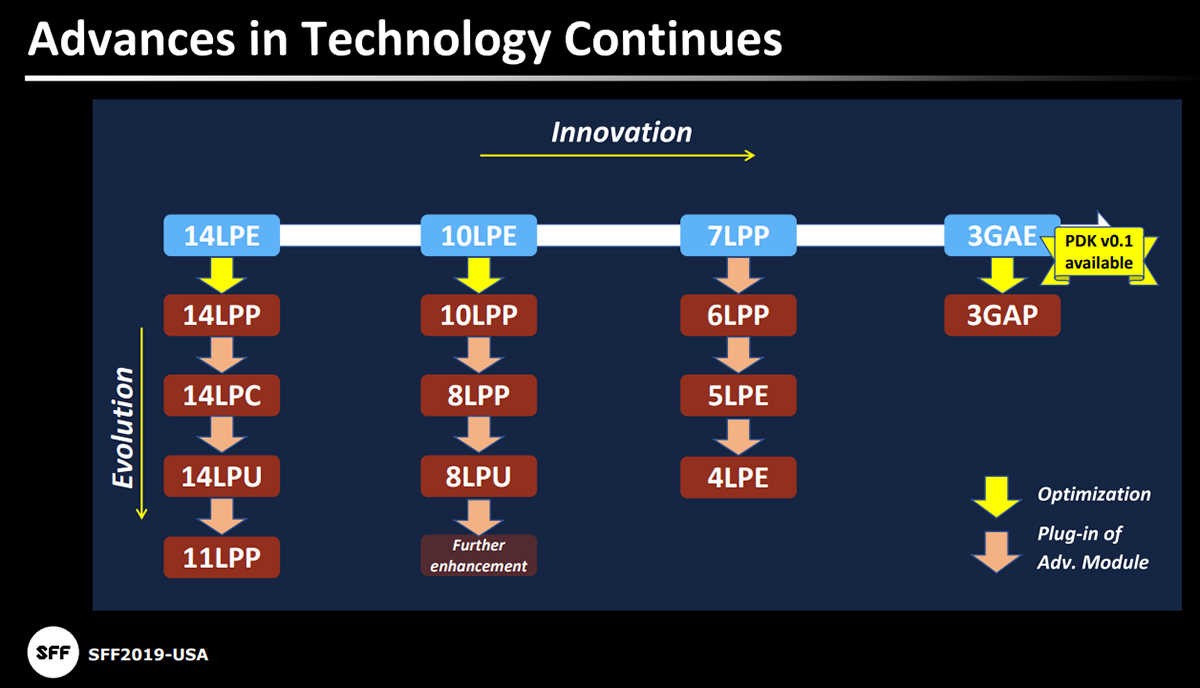

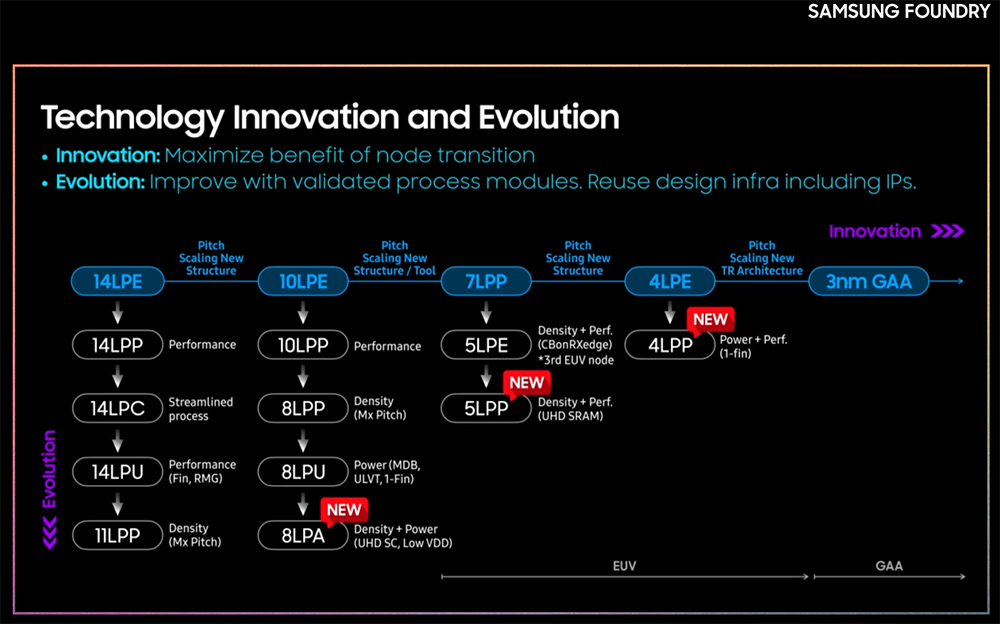

首先来看看当代工艺的一些改进,主要是现有7nm、5nm的技术更新。三星最新的路线图跟2019年在三星SFF公开的那张是有一些变化的。下面这张图中至少多出了3个新的工艺节点,还有节点位置上的调整,比如说相对显著的是4LPE/4nm,从原本从属于7LPP同代演进,改为一次完整迭代——这个会在下文中提到。

此前的工艺中,从属10LPE工艺演进中,三星增加了一个8LPA。三星表示相比于8LPU,8LPA实现了10%的性能提升和15%的功耗缩减。另外在7LPP工艺以下多出5LPP,算是改进版的5nm节点,相比5LPE有5%的性能提升、10%的功耗缩减。新增的4LPP演进会在下文中提及。

回顾一下三星的5nm工艺。之前的文章多次提过,台积电和三星在7nm之后的路线规划是存在较大差异的。尤其台积电N5工艺是属于N7工艺的完整迭代,而三星的5LPE(和新增的5LPP)本质上属于7LPP的同代工艺演进。所以N5和5LPE的竞技舞台其实还是有极大差异的。

三星在用词上一向都比较“考究”,完整工艺迭代叫innovation,而同代工艺的BKM更新叫evolution——可能叫BKM更新有点不合适,毕竟5LPE相比7LPP实际的性能、效率、晶体管密度提升还是远超一般的BKM更新的(0.75倍的逻辑电路面积缩减/10%性能提升/20%功耗下降)。

5LPE是去年下半年开始大规模量产的,高通骁龙888就是采用了该工艺的代表性产品。一个家族内的工艺演进通常也意味着可复用的IP,以及金属层方面的一些优化措施、标准单元的小幅变化等——晶体管和SRAM单元基本保持一致。三星原本的路线是更早地在7nm工艺上应用EUV技术,以及更早地在3nm工艺上应用GAA晶体管,这些都是众所周知的了。所以5LPE成为其中的一个过渡产品。

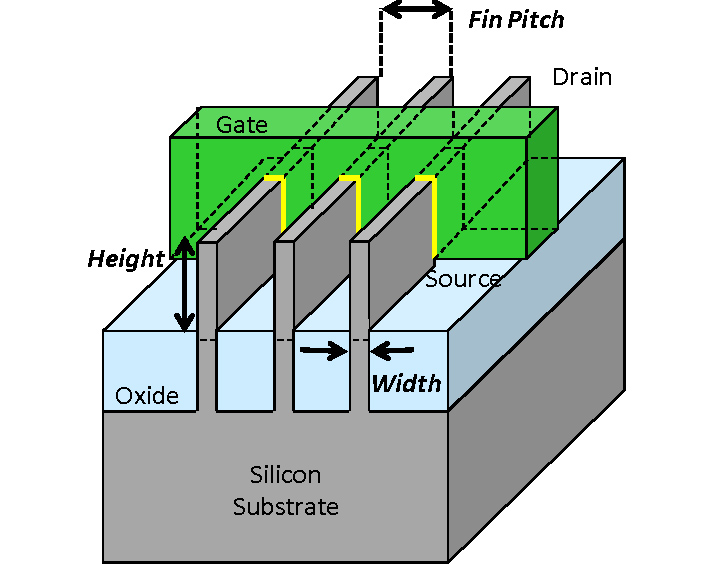

总体上来看,5LPE和7LPP的晶体管是基本类似的,fin pitch(鳍间距)为27nm,gate pitch为54nm/60nm(面向不同性能和功耗需求的两种单元),gate length(栅极长度)也在8-10nm(以前所谓的几nm工艺指的就是这个位置的尺寸,不过现在几nm工艺的说法更具象征意义,而不再指代任何实际的物理尺寸)。

从Wikichip最新的数据来看,5LPE和7LPP的SRAM存储单元尺寸也基本差不多,包括面向高性能的单元大小是0.032μm²,高密度单元则为0.026μm²,和台积电N7工艺基本处在同一水平线上,比N5工艺还是有比较大的差距。不过三星也提到测试中,SRAM部分Vmin等参数表现有提升。

5LPE标准单元方面的变化此前的文章已经多有提及了,主要是引入了一种新的6T UHD单元,实现了更高的密度(超高密度);而7.5T HP单元的基本情况不变。这里就不再费笔墨赘述了。

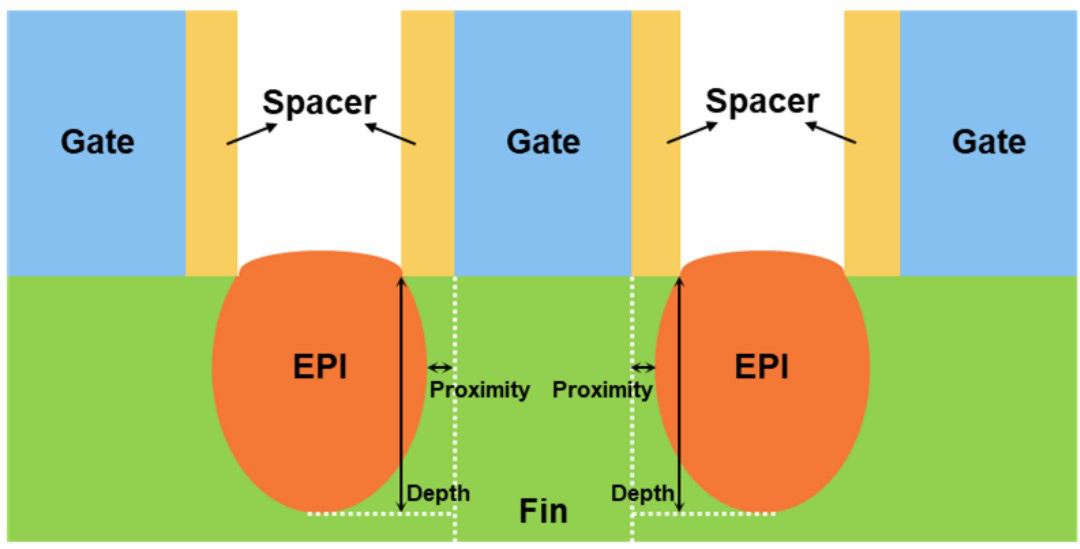

提供一个有关5LPE工艺改进的新资讯:7.5T HP和6T HD这两种单元有着不同的gate pitch,所以gate之间的结构自然就有变化。S/D cavity(源/漏极腔)会存在差异,HD单元的这个腔会更深、更长,于是沟道应力、寄生电容等都会有差别。这部分的变化对性能会有影响。这部分区域的Si与SiGe外延生长,对于减少寄生电阻、提升驱动电流是比较关键的;但也会增加gate和源极漏极之间的寄生电容从而在电路级别上对性能产生影响。

三星对此作了蚀刻工艺上的提升,主要强调减少沟道的电阻差异,令两种标准单元做到匹配。对于gate pitch更大的HP单元而言,在沟道电阻方面有大约20%的改进,βdc获得较大提升;HD单元的源极漏极掺杂改进,在接触电阻方面相比7nm分别有nFET 15%和pFET 25%的提升。如此一来两种单元接触电阻方面的偏差控制在了3%以内,据说此前7nm工艺中两种标准单元的偏差有10%。

总的来说,5LPE在nFET和pFET上都获得了15%的βdc提升,对比相同的7nm HP单元βac提升超过10%。三星另外提到他们测试了采用7LPP和5LPE工艺的相同设计的芯片,在相同IDDQ(静止状态下VDD供电的电流,即在一次开关完成后,下次开关之前的供电电流)之下,Vmin有10%的降低。

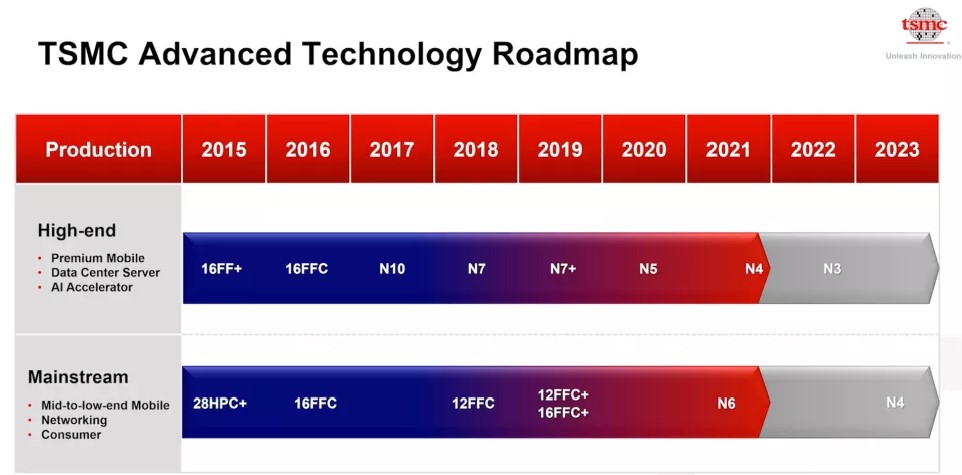

台积电这边,这次Technology Symposium上提及的N7、N5的演进情况似乎没有什么太大变化,如上图所示。N6同样是其7nm家族的工艺,相比N7+采用了更多的EUV层,这也不是新鲜事了。台积电也在会上提到,“2021年5G移动和AI加速器的增长下,N7仍然是供给的关键。”

N5家族同代演进中包含N5P、N4等。和N7时代的N7P一样,N5P也属于N5的性能增强版。台积电宣称N5P能够提升至多5%的频率,或降低至多10%的功耗。在设计或IP的迁移上,从N5到N5P应该也会比较平滑。

除此之外,针对制造工艺,这次台积电更多着眼具体的应用,做工艺上的改进——某些工艺的更新周期会相对比较久。不过这样一来,可能本文有关工艺更新的讨论,与上述三星工艺的讨论就不在一个维度上了,比如说台积电这次提到针对射频的工艺改进,其实三星也有(如前不久三星比较高调地推了8nm RF制程,还给晶体管取了个名字叫RFextremeFET,着意于5G市场)——只不过双方公开的信息是不对称的,很难直接比较。所以我们也只能对双方公开的信息做个基本的罗列了。

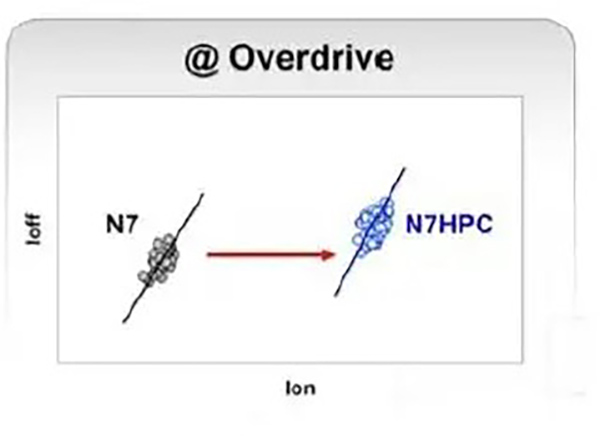

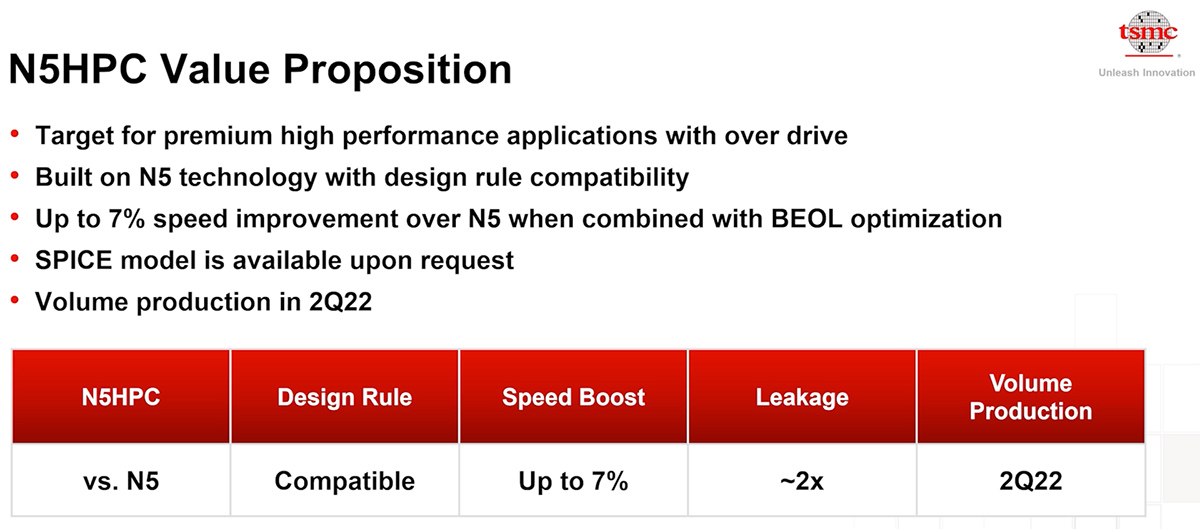

具体的应用上,首先是HPC性能需求,HPC应用方向比较关注供电电压的的overdrive,也就是高于标称的工艺VDD的需求。所以台积电预期会在今年第四季度提供N7HPC,明年二季度提供N5HPC工艺,来支持overdrive,上面这张图是对应Ion和Ioff,N7HPC相比N7的变化。台积电上次专门面向HPC推工艺是28nm时代的事情了。对应这两个面向HPC应用的工艺,台积电也会推SRAM IP设计。

对应的N5HPC也能提供更高的频率,对于需要高频的通用处理器也是适用的。

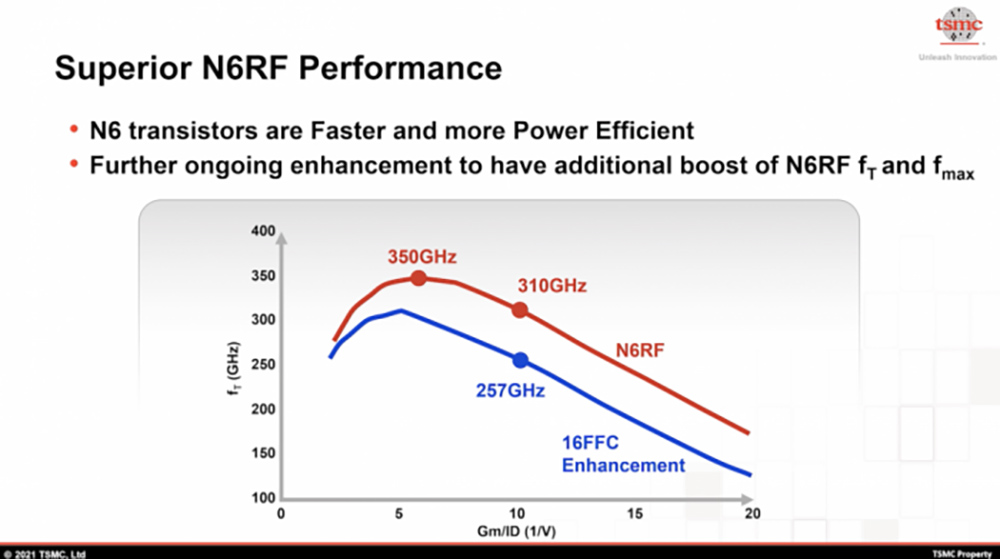

针对5G、WiFi 6/6E、蓝牙、雷达成像等市场需求,台积电也有对应的动作。N6RF是台积电在Symposium上特别提到的工艺,上面的曲线图是N6RF与N16FFC-RF的对比。这里Ft(cutoff frequency,与器件沟道长度成反比)和Fmax(maxium oscillation frequency,与Ft的平方根成正比)是两个描述RF性能比较重要的指标。

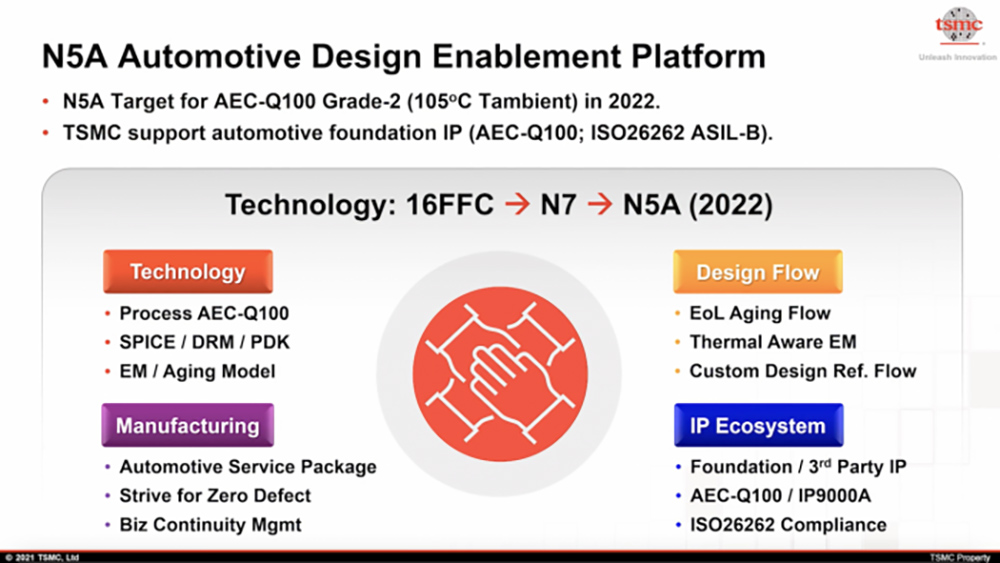

汽车应用中有个N5A工艺,把N5工艺的特定产能用于汽车应用芯片市场,计划明年第三季度之前完成所需的认证。据说N5A延续了N5的性能、效率、逻辑密度,当前处在开发阶段。

另外会上也有公布一些不属于尖端工艺上的改进。比如N28HPC+RF与N16FFC-RC工艺的加强,比如gate寄生电阻方面的变化。针对LNA应用,台积电也对SOI 130nm和40nm工艺的改进。针对IoT和边缘应用,台积电也提供对ULP(低功耗)与ULL(ultra-low leakage)静态功耗有要求、面向带电池设备要求的工艺平台。这些信息整体比较零散,不过也算是对尖端工艺未来应用方向的一个简单整理了。

过渡至3nm之前的4nm

在三星的计划表中,7nm和3nm之间的空档是用6nm、5nm、4nm来填充的。2019年的三星SFF论坛上,三星还是将6LPP、5LPE和4LPE都放在7LPP下面作为同代工艺的。但在IEDM 2020更新的路线图上,横向的innovation还是发生了变化的,主要是4LPE独立出来了——起码就这张图来看,是成为了一个完整迭代的工艺节点的。

2019年公布的三星foundry工艺演进路线

2020年公布的三星foundry工艺演进路线

这一点可能是早前三星计划之外的,毕竟7nm家族多出一个5LPP演进,4nm也多出4LPP演进——若加上之前的6LPP,感觉7nm这个节点延伸出了太多BKM更新。

不过其实这次的变动并不是营销方式上的简单变化,三星的4nm工艺的确将发生晶体管间距、结构方面的变化。那么将其放到横向的innovation上,好像也没什么问题。4nm也因此将成为三星的最后一代FinFET晶体管工艺。

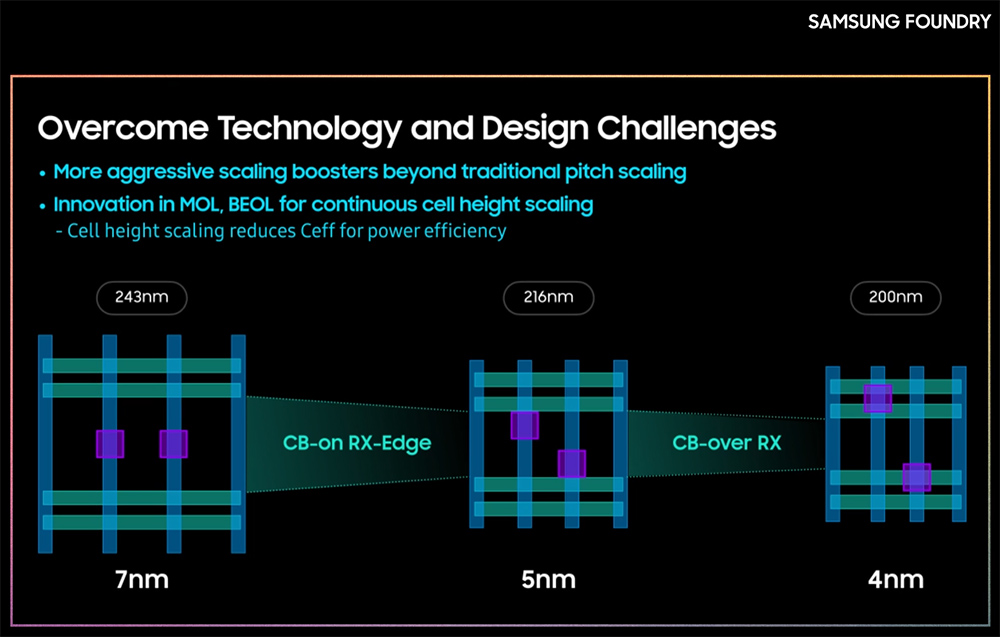

规划中4LPE的金属层M1间距会从此前的40nm缩减至28nm——这个变化还是比较大的,可能意味着这一层需要采用EUV双重曝光。M3间距也从36nm缩减至32nm。4nm节点标准单元高度会缩减到200nm。Wikichip另外给出数据称,三星4nm工艺的fin pitch会缩减4nm,达到25nm——不过这个消息并未得到确认。

基于此,Wikichip预计三星4nm工艺200nm高的单元,晶体管密度大约在137MTr/mm²左右;对比于三星5nm节点晶体管密度约为127MTr/mm²。其实这个值仍然是低于台积电N5的HD单元的(173MTr/mm²)。

值得一提的是,4LPE这一代工艺演进多出了4LPP。三星表示4LPP相比4LPE会实现5%的性能提升和10%的功耗降低;并宣称是“GAA之前,实现最佳PPA的第5代EUV节点”。

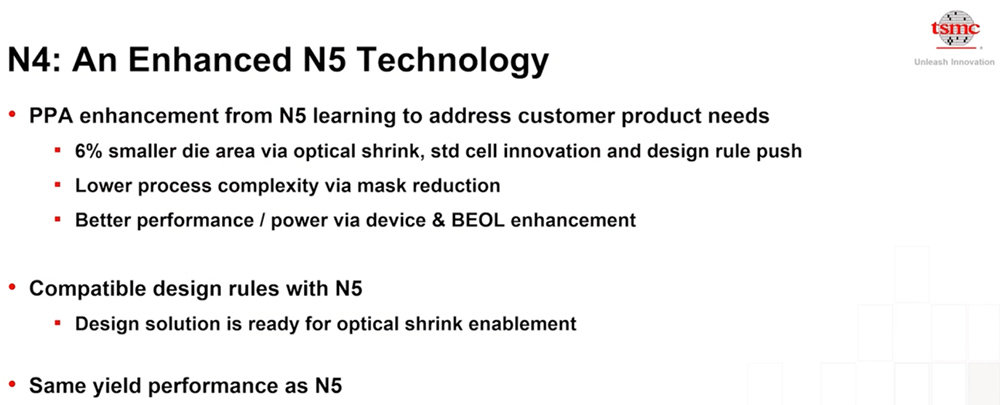

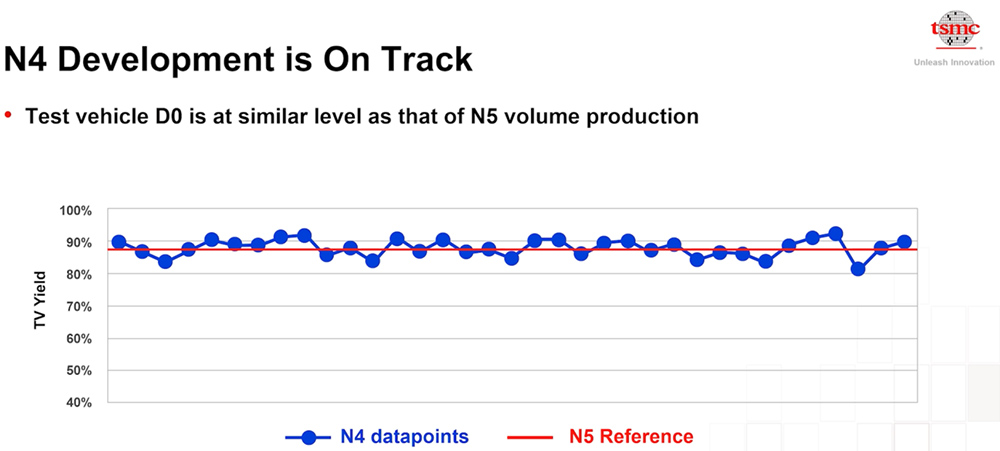

台积电N4工艺原则上还是属于N5工艺的同代演进,和N5、N5P、N5HPC都属于一个家族,也是以更好的PPA实现与N5设计规则的兼容和设计的平滑迁移。

有关台积电N4的公开信息也不多,通过BOEL的加强实现功耗、性能表现的加强;并藉由所谓的optical shrink来实现6%的die尺寸缩减——这个表达其实也挺模糊的;使用和N5一样的设计规则、设计基础设施、SPCE仿真程序以及IP。

N4也会用到更多的EUV层,减少所需的mask掩膜数量、工艺步骤和成本。N4虽然不是什么大版本迭代,但据说对台积电而言也会是未来主流SoC的重要制造工艺。台积电计划N4在第三季度实现风险生产,达成HVM会在今年末或明年初。

通往未来的3nm

3nm不是本文要谈的重点,不过就像之前说的,3nm对于三星而言是个跃进的重点。因为三星在3nm节点上就要开始用GAA晶体管结构了,就像当年7LPP早于N7开始用EUV一样。三星实际要在3nm上应用的是名为MBCFET的纳米片方案。

三星此前宣称明年其3nm工艺就能进入大规模量产,不过另外三星还在IEDM上更新了一组数字,即其3nm工艺实现了相比7nm工艺10-15%的速度提升和25-30%的功耗降低。注意对比的是7nm工艺。以这个数字来推算,可能最早的3nm GAA在表现上并不会太出色——迭代工艺弱于上代+++工艺原本是Intel的传统。而且这个数字也弱于三星在2019年给出的数字。

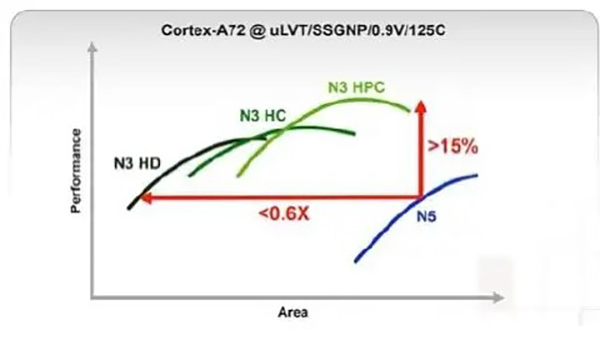

台积电的N3则明确仍是FinFET晶体管,预计量产是在明年的下半年,下个季度出v1.0 PDK,广泛IP授权是明年Q2/Q3。台积电给出的数字是N3相比N5实现了同功耗下10-15%的性能提升,同性能下25-30%的功耗降低,逻辑电路密度提升70%,SRAM密度提升20%,模拟电路密度提升10%。不同单元库的性能与面积效益提升如上图。就这些数字来看,在3nm节点上,台积电的领先优势仍然是相对明确的。

责编:Luffy Liu