今年是Linux核心发布三十周年。二十年前,程序设计人员认为Linux只是一种利基技术,猜测它应该行不通。然而,利用公开免费发布的Linux,开放原始码催生了数百项项目,从而涌现一大批稳健且灵活的产品,Linux成为开源软件开发的基石。

这种成功的模式是否可以复制到开源硬件上呢?RISC-V这样的指令集架构(ISA)是否也可以像Linux核心作为开源软件的基础一样,成为开源硬件发展的基石呢?

这个问题并没有标准答案。

当前的RISC-V是一种开放的架构,作为一项标准提供,让开发人员可以自由、灵活且迅速地用它来进行产品设计。但另一方面,硬件更加复杂,有多层堆栈,因此不像软件包那样简单。

本文针对RISC-V硬件生态系统的利益相关业者进行了调查,包括OpenHW Group、RISC-V International、恩智浦半导体(NXP Semiconductors)、晶心科技(Andes Technology)、Nvidia和西部数据(Western Digital;WD),描述开源软件的相似性、导入的障碍以及支持社群和生态系统的重要性,最后并探讨开源硬件对商业芯片制造商的意义。

关键在于质量与生态系统

OpenHW Group总裁兼首席执行官Rick O’Connor

OpenHW Group总裁兼首席执行官Rick O’Connor认为,RISC-V相当于Linux核心,他在接受采访时说:“RISC-V ISA一开始就像核心之于Linux一样,其结果是催生其他开源软件项目和计划如雨后春笋般涌现。当然,如果说Linux核心为20年前的软件播种,那么RISC-V ISA就是硬件的种子。”

然而,采用开源硬件仍然存在障碍。“障碍之一就是质量问题。”O’Connor补充道:“例如,如果你在一个芯片或SoC产量较高的公司工作,肯定不会把宝押在这个从网络下载来的IP模块上,然后直接走进老板办公室说:‘我们准备好使用这个大学开发的酷炫核心了,它应该可以导入我们的量产SoC中。’”

因此,OpenHW Group倡议开放的验证流程。O’Connor说:“人们可以查看生态系统达到的质量并使用所得到的结果——如果完全自行开发,应该就能获得高产量SoC公司所期望的结果。”

O’Connor还指出业界对于RISC-V和RISC-V International的误解。RISC-V International是监督核心ISA规范的基金会。

O’Connor说:“人们总是误以为RISC-V International基金会是开发核心的,实际上并不然,它是专注于开发一系列定义ISA的规范。这些规范适于各种用途:商业、开放或封闭、营利或非营利,设计人员可以根据自己擅长的逻辑撷取语言,采用不同的语言编写。”

就这方面来说,他强调OpenHW Group并不只是开发RISC-V核心。“我们真正专注的是异质丛集计算所需的构件,用于各种大小的SoC。我们将不同类型的核心、加速器以及所需的各种模块汇集在一起。”

O’Connor表示,RISC-V ISA在此发挥了关键作用,它开拓了“一个创新的领域。任何人只需下载ISA规范就可以在设计中使用核心,而无需与任何人签署协议。从这个角度来看,RISC-V ISA是推动RISC-V发展的关键因素。回想20年前,基于Linux核心的建置方案非常多,远远超过今天基于RISC-V ISA的方案。”

“硬件产业面临的挑战在于,如何才能围绕着RISC-V持续提供五至六个核心系列的建置方案。”

恩智浦半导体软件工程副总裁Rob Oshana

恩智浦半导体(NXP Semiconductors)软件工程副总裁Rob Oshana表示,开源硬件的发展轨迹与开源软件几乎完全相同。从Linux Kernel Archives网站可以知道,“Linux是成千上万开发人员共同开发和使用的实际源代码。”

Oshana说:“RISC-V International拥有的是规范,而不是具体的实施方案。这些规范是经过开发人员通力合作制订的,在当前的RISC-V社群和生态系统下运作良好。”

“由于基金会目前还没有开放的实施方案,因此,OpenHW Group正在填补这一空白,以开发免费、开放、免授权费的实施方案以及其他类似Linux基金会(Linux Foundation)的担保。”

不只是规范…RISC-V也需要社群支持

随着开源从软件扩展到硬件,越来越需要社群或合作伙伴生态系统的参与。Oshana说:“任何一个开放的社群都需要培养、照顾与供给。随便扔点东西进Git就称其为‘开放’,这样注定会失败。它需要一个社群。”

“如果不是经过社群的努力,建构了核心、开发板、软件和参考平台,OpenHW Group的核心无法取得成功。”他补充说:“OpenHW Group正利用最佳实践而使得这一硬件技术成功。”

Oshana认为,其关键就在于如何利用最佳实践并“持续投资实际工程,以保持硬件开发的成功。”

同时,开源工具也在不断发展中。“我们需要一套可靠的硬件工具来支持,”Oshana指出。和其他人一样,他也认为真正衡量一个开放社群的标准是参与度。例如,一旦发布一种实施方案,关键指针就在于用户社群如何管理更改需求、修复错误等。Oshana说:“这相当于Linux的上游。维护者的角色必须明确。”

RISC-V International首席技术官Mark Himelstein也强调社群的重要性。“Linux并不一定是最好的操作系统(OS),但人们为什么用它?因为它拥有社群和支持。它的魔力就在于所有权的自豪。现在使用Linux很简单,但我认为RISC-V就是硬件的Linux。相信再过五到十年,人们也可以毫不费力地使用RISC-V作为硬件。”

硬件比软件更难

开源硬件和软件的主要区别在于整个堆栈的复杂性。O’Connor说:“看看当今生产的绝大部份芯片,其中有超过95%采用Verilog工具流程并在相应的商业验证基础设施中生产和验证。因此,如果我们想让别人使用这些核心,就要让它们轻松融入到这种商业工具流程中。”

RISC-V International首席技术官Mark Himelstein

SoC供货商大多使用SystemVerilog通用验证方法来验证环境。O’Connor说:“我们不会让他们采用不同的方法。如果我们真的想要在这些开放原始码区块中导入RTL,它们就必须能够融入该工具流程。”

硬件的实体特性仍然使软件开发人员面临前所未有的挑战。O’Connor指出:“在半导体晶圆厂中,从几何层面的物理特性来看,其秘诀就在于晶圆工艺。”他提到了采用较大节点工艺设计中那些鼓舞人心的成果。

他解释说:“当你有了晶圆工艺技术、最重要的工具库、生产GDSII的CAD工具物理层以及光罩技术本身;接着还需要生产光罩的设备、验证设计的仿真和验证软件与工具、用于撷取和合成设计的合成工具,以及用于这些设计的IP。”

O’Connor指出,“历经数十年开发,堆栈中的所有分层都包含与各层相关的丰富专利组合。层与层之间的联系也非常紧密。因此,任何商业公司都不会一开始就试着用开源方案和工具来替换整个堆栈。”

OpenHW Group创始人曾经考虑是否创建专门针对RISC-V核心的生态系统,但最终决定放弃。

O’Connor说,他们的首要目标是创建核心。“我们的中心思想和理念,都是为了克服开源硬件面临的挑战。换言之,我们的目标是利用通用建构模块轻松建构异质丛集,同时用自己的秘密武器(围绕着它建构的加速器和扩展)进行量身客制。”

其中涉及的工作包括在通用元素上合作,并在软件工具级、硬件RTL级甚至验证级上定义接口点。“加值之处在于如何修改一组通用的建构模块来添加客制加速,打造可实现自有加速器算法的客制异质丛集。因此,重点在于RISC-V作为一种ISA,让我们一开始就在处理器核心级采用吸引人的通用建构模块,然后在此基础上进行建构,同时利用最佳商业工具以增强使用者的信心。”

“所以,IP是他们可以信任的。”他并预测很快就会有开源FPGA,最后还有SoC。

RISC-V处理器设计浮上台面

相较于开源软件,基于RISC-V开源硬件的处理器设计有所不同:其架构冻结了ISA,使其作为一个可长期使用的组件。ISA在此是处理器能读懂的一种语言,让软件可以使用这个语言表来编写。如何采用这种语言对软件进行编码,有助于让处理器了解应该做什么。

任何人都可以使用RISC-V ISA,并完成设计扩展等。与开源软件的共同点是,RISC-V也没有IP版权的问题,且其参与者可以共享其设计成果。

简而言之,RISC-V让设计工程师得以创新,为其提供选择的自由。

SiFive共同创始人兼首席架构师Krste Asanovic在CES 2021的专题讨论中阐明了RISC-V在开源硬件领域的地位。Asanovic说:“RISC-V并非开源处理器,而是开发处理器的开放标准。”因此,这个规范是开放的,任何人都可以利用它进行设计。

这类似于一种微架构授权,让处理器开发人员能够完全按照其需要进行客制,以实现优化处理器设计。例如,储存设备制造商WD针对固态硬盘(SSD)设计开发自家的控制器处理器,其目标在于优化连接至主CPU和闪存的控制器接口。

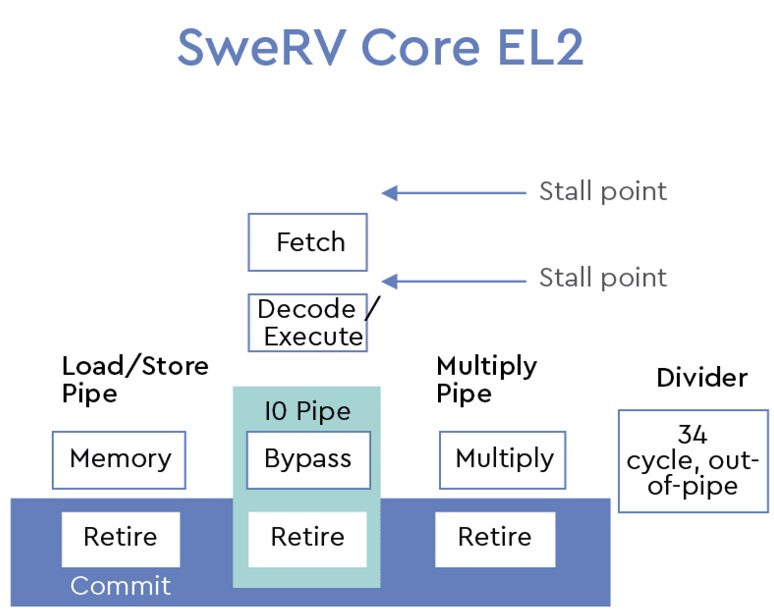

Western Digital (WD)的SweRV Core EL2核心专用于取代SoC的状态机和其他逻辑功能。

在2020年RISC-V高峰会期间,WD展示了一款搭载其开源RISC-V SweRV核心的闪存控制器。WD RISC-V资深业务总监Ted Marena表示,WD将在开源社群发布其RISC-V核心。

他说:“尽管我们开发了核心,实际上核心并不是真正的秘密武器,围绕核心设计的组件才是最重要的,例如与主处理器之间的接口。” Marena并补充道:“如何连接至另一端的闪存,才是真正的差异化优势所在。”将核心提供给开源社群也吸引着外部的其他开发人员作出贡献,从而改善设计。

例如,来自中国台湾的晶心科技(Andes Technology)就是商业公司如何致力于开源架构的最佳写照。晶心科技还推出了几款RISC-V处理器,目前已经获得一些客户的采用。

除了为SK Telecom和瑞萨电子(Renesas Electronics)设计RISC-V核心,晶心科技最近宣布,专注于开发5G基站芯片的新创公司EdgeQ也将使用Andes核心RISC-V授权以及客制扩展,以提供整合人工智能(AI)的可编程开放5G平台。晶心科技的客制扩展让EdgeQ得以设计、扩展和客制自己的指令集,以实现当前无线基础架构无法满足的性能、功能和功率特性。

晶心科技首席执行官林志明

晶心科技首席执行官林志明说:“对我们而言,RISC-V是用于硬件接口或描述的开源ISA,而非开源核心。在RISC-V阵营,所有的公司之间都是竞争对手。谈到RISC-V标准,大家都是彼此合作的关系,但在日常业务中,又不得不相互竞争。”

CPU核心选择

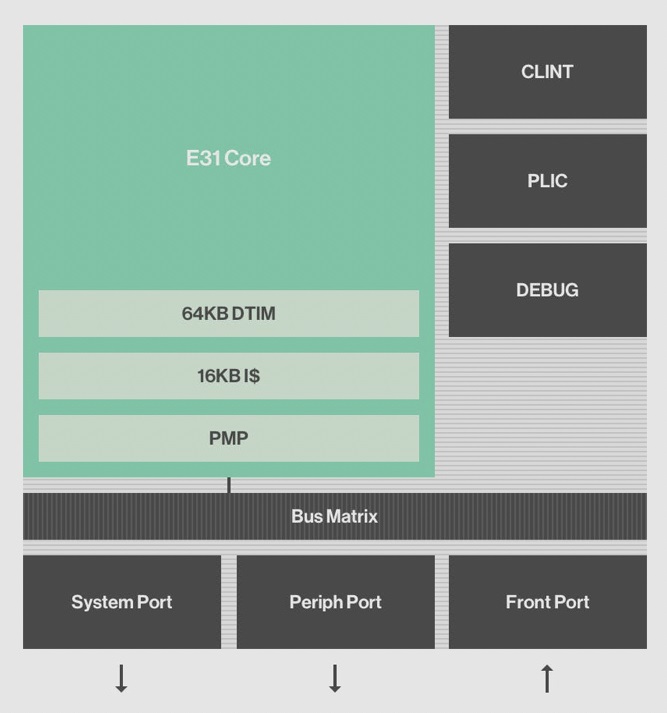

Nvidia和WD等公司都采用了自家RISC-V核心来设计芯片,有些公司则用户许可证的可配置核心。处理器设计人员在设计商业芯片时,可以从SiFive等公司购买各种授权的RISC-V核心,SiFive认为该公司在RISC-V的角色就类似Red Hat之于Linux。

尽管这是SiFive业务的重要组成部份,该公司除此之外也向工程师提供服务,从设计到制造协助其打造处理器芯片。

SiFive的E31核心针对物联网、储存和工业应用。

AI芯片制造商Esperanto Technologies总裁兼首席执行官Art Swift表示,越来越多的设计人员在追求不同商业模式的过程中转向采用RISC-V。“相较于现有的微控制器(MCU)均采用相同核心,RISC-V则提供授权更多的核心选择的机会。”

目前提供商业RISC-V核心的厂商至少有七家。

Swift说,现在的专有ISA是由某家供应商管理,客户只能使用一个专有ISA,因而处理器设计无法满足特定的产业需求,除非取得昂贵的架构援权才能打造客制核心。而且,现在也无法再转卖核心了。因此,很少有公司像Apple那样能够负担得起这么高的投资。

然而,RISC-V的架构是免费授权的。用户可以设计自己的核心,也可以选择开源核心。正如Swift所指出的,拥有众多的核心选择对于打造经未来验证的设计至关重要。

最早采用RISC-V的Esperanto已经在单芯片中封装了1,000多个低功耗RISC-V核心,以加速其数据中心的AI工作负载。

下一轮计算革命?

几乎就在二十年前,程序设计人员并不看好Linux,认为这只是一项利基技术,推测其发展有限。如今,我们看到硬件社群再现了二十年前Linux的发展过程,新创公司基于RISC-V开放标准来设计处理器,创投业者则在仔细审查这些芯片新贵。

像Nvidia和WD这样的巨擘也在开始大量采用RISC-V。

RISC-V最初只是一项研究项目,经过不断发展,现在已经发展成为处理器设计的开放标准了。正如Swift所指出的,RISC-V并不同于过去指令集之间的派系之争,而是展现其创新能力和选择自由。

随着RISC-V的迅速发展,围绕RISC-V处理器设计的基础设施和软件生态也汇集在一起了。RISC-V开放标准稳健发展且充满活力,象征着开源硬件的未来前景,或许也正引领着下一场计算革命。

(参考原文:Can Open Source Hardware Emulate Linux?,By Nitin Dahad & Majeed Ahmad)

本文为EDN Taiwan 2021年4月刊杂志文章,作者Nitin Dahad为EE Times欧洲特派记者,Majeed Ahmad为EDN主编

责编:Luffy Liu