英特尔(Intel)创办人Robert Noyce和Gordon Moore为半导体产业带来了两项重要传承。其一是“摩尔定律”(Moore’s Law)——众所周知,但却经常被误解。其次是平面集成电路(IC)。另一位集成电路发明人Jack Kilby在2000年获得诺贝尔奖时曾经说,“如果Noyce还活着的话,一定会和他一起因为集成电路而共享诺贝尔奖的荣耀。”

Noyce和Moore为业界带来重大发明——商用晶体管和集成电路——双极性接面晶体管(BJT)以及平面集成电路技术,并成立了第一家公司——快捷半导体(Fairchild Semiconductor)。当他们离开Fairchild后成立了英特尔,致力于打造高密度内存以及低功耗逻辑芯片——全新的金属氧化物半导体场效应晶体管(MOSFET),并引领第二次的产业转型。

这些芯片仅使用一种MOSFET的晶体管类型(p型或n型),具有三种电源电压(+12V、0V或接地以及-5V)。然而,相较于使用双极性接面晶体管制造的集成电路,他们仍然具有更低的功率以及更高的密度。

在那个时代,还没有像当今所熟知的CMOS等互补式MOSEFET (n型和p型)单芯片整合技术。一直到15年后,大约在1980年代初,尽管CMOS集成电路较复杂且制造成本高,但由于降低功耗的需求,CMOS整合电路成为英特尔与业界打造逻辑芯片与内存芯片的选择。

众所周知,当今的高性能运算数据中心消耗大量的电力,而行动运算芯片则受到能量供应以及电池寿命的限制。这两个细分市场目前都受到每一代CMOS工艺电源电压微缩速度放缓的挑战。

针对可以使用平行运算的应用(例如绘图和平行算法),我们利用多核心处理途径来降低功耗。这正是英特尔在2005年采取的所谓“向右转”(right-hand turn)策略。

当然还有一些应用无法实现平行化,因此被称为单线程应用。此外,透过互连走线在内存与运算逻辑之间来回移动数据的能量,成为最主要的运算功耗来源。

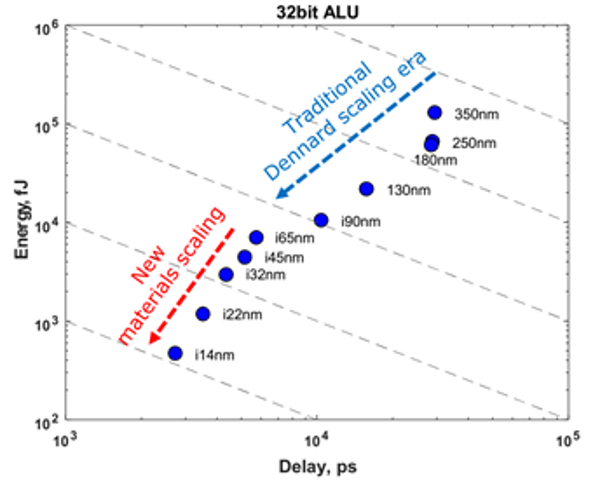

从1990年代起,业界逐步为每一工艺世代提高3倍的CMOS逻辑开关能效。这主要是透过Dennard微缩定律实现的——该定律规定在每个新的工艺世代,MOSFET闸极的长度和宽度、电源电压和闸极氧化层的厚度都减少0.7倍。

从5V降至1.25V,大约有三分之二的开关能量改善就来自于每一工艺世代微缩0.7倍的电源电压(V)。遗憾的是,Dennard微缩定律在2003年130纳米(nm)节点时止步。之后,每一世代的开关能源降低幅度因此减少了。

由于MOSFET在关断状态的漏电流限制,因而不可能再降低30%的电源电压。CMOS晶体管可以被开启或关断的程度,取决于电子热能分布的物理限制特性——在室温下每10倍电流变化受限于60mV。这种效应被称为Boltzmann Tyranny。

由于Dennard微缩在2003年左右结束,其后每一代新工艺中的功率密度不再保持趋近于恒定,而是必须透过减慢或限制CPU频率增加,从而克服功率密度增加的挑战。

使用多个平行处理核心,就能提高运算性能。由于摩尔定律仍持续进展,而且使CMOS技术能够在每代工艺提高约2倍的晶体管密度,从而降低了每一世代中的每个晶体管成本。这是摩尔定律的基本前提。

英特尔工艺技术世代中,32位算术逻辑单元的能量与延迟比较(来源:Intel)

自Dennard微缩结束后,英特尔与业界持续创新并致力于延续摩尔定律,引领业界走向所谓的MOSFET材料和组件结构微缩的时代:

• 在90nm节点应变信道,以提高信道迁移率

• 在45nm节点使用高k闸极电介质,以减少闸极氧化物漏电流

• 使用FinFET减少短通道在源极—漏极关断状态的晶体管漏电流

• FinFET技术还能以鳍片高度缩小组件面积

展望未来十年,功耗和功率密度将会被视为限制数据中心和行动装置运算性能提升的因素。我们将再次面临挑战,就像1980年代使用80386处理器时的情况一样——运算性能受到功耗或热的限制,但事实上,这些问题最终都透过芯片封装技术改善了。

在面临这一挑战时,英特尔曾经将微处理器制造技术从仅使用n通道MOSFET改变为采用互补n型和p型MOSFET的CMOS,在同一工艺技术中提供了两种晶体管。

在接下来的系列文章中,我们将继探索在CMOS持续微缩过程的限制因素,以及如何引导业界走向克服挑战之路。

编译:Susan Hong EETTAIWAN

- 未来日记里能看到晶体管革命性的变化