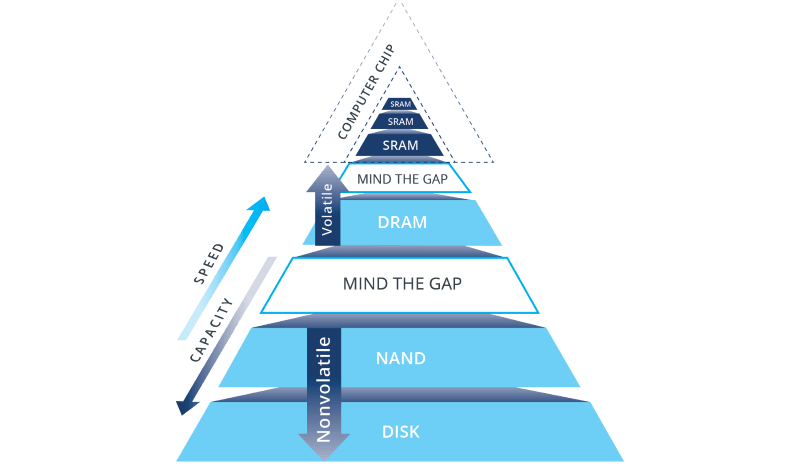

利用磁性材料作为计算机用内存,可以追溯到1940年代末发明磁芯(Core)内存之时。从1960年代起,硅基内存的出现,阻碍了磁性内存的进一步发展,同时也带动静态随机存取内存(SRAM)、动态随机存取内存(DRAM)以及各种形式的非挥发性内存被广泛采用。各种内存类型迅速扩展,伴随着计算机中央处理单元(CPU)对于加快速度的要求,导致了所谓的“内存阶层”(memory hierarchy),如图1所示。

图1:内存阶层显示传统内存类型如何以速度(越接近顶部速度越快)和容量(接近底层容量最大)排列

速度更快且更昂贵的SRAM内存在实体上更靠近CPU,二者通常位于同一个芯片上。另一方面,相对速度较慢的DRAM内存在实体上远离采用客制芯片工艺制造的单独芯片,从而为最大内存密度实现优化。尽管金字塔形的阶层式内存可能给人固定不变的印象,但是,存在数十年的内存类型在使用上仍然出现了重大问题。

如今,距离SRAM的发明已经将近50年了,内存产业正处于颠覆的阵痛期。 NAND Flash已经朝向3D转型,而DRAM也正接近其微缩极限。SRAM在经过多年作为片上存储器(on-chip memory)的骨干后,如今也在成本和能量耗费方面遭遇严峻的挑战。这些半导体内存方面的问题,加上所涉及的市场规模,导致市场上陆续出现各种候选技术以取代内存——特别是针对SRAM。

SRAM面临的挑战

SRAM是采用任何CMOS工艺“免费提供”的内存。自CMOS发展早期以来,SRAM一直是开发和转移到任何新式CMOS工艺制造的技术驱动力。随着近来用于深度学习的所谓“特定领域架构”(DSA)崛起,每个芯片上的SRAM数量达到了数百个兆位(megabite)。这带来了两项具体的挑战。

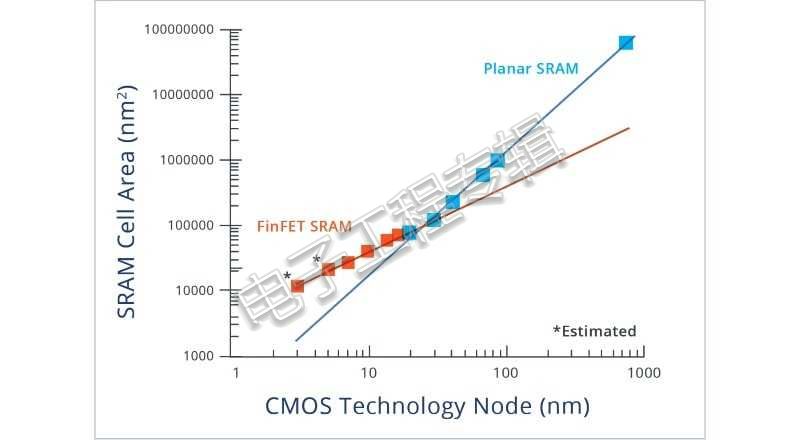

第一项挑战是随着采用FinFET晶体管的最新CMOS技术进展,内存单元尺寸的效率越来越低。从图2就可以看到,SRAM单元尺寸可以绘制为CMOS技术节点的一个函数。

图2:6T结构的SRAM单元尺寸在过去30年来的缩小演变。值得注意的是,当 FinFET晶体管成为CMOS的基础后,速度开始趋缓(来源:1987~2017年国际电子组件会议(IEDM))

从平面到FinFET (planar-to-FinFET)的转变对于SRAM内存单元的布局效率有着显著的影响。采用FinFET的临界间距逐渐缩小,导致SRAM单元尺寸缩减迅速减缓。有鉴于对于更大片上SRAM容量的需求不断增加,现在正是最糟糕的情况了。我们距离SRAM将主宰整个DSA处理器大小的情况不远了。

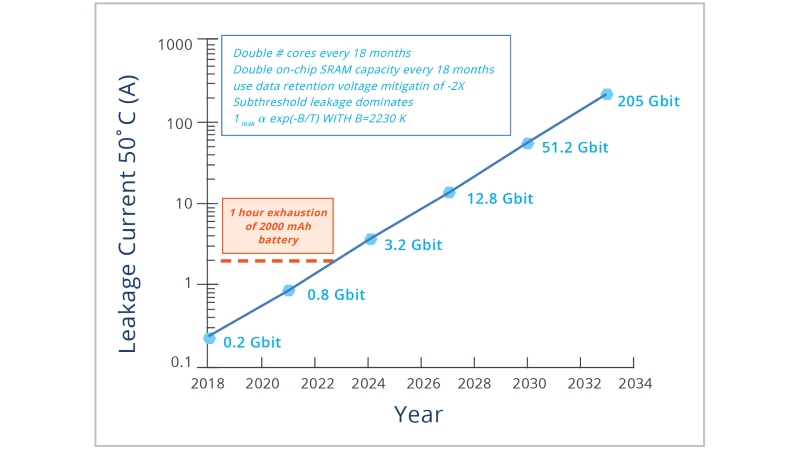

第二项挑战在于从正电源流经SRAM单元到接地的漏电流。其中很大一部份原因是次阈值晶体管泄漏的指数级温度启动——这意味着随芯片变热,这种漏电流将会急剧增加,这导致了能量的浪费。虽然这通常称为静态功耗,但这种漏电流也会在SRAM处于有效使用状态时发生,并形成能量浪费的下限。

近20年来一直是使用缓解技术来限制这种影响,最先进的方式是将SRAM电源电压从其工作值降低到所谓的数据保持电压(DRV)。一开始,这种技术带来明显减少的漏电流,降低至工作电源电压值的5到10倍。随着技术节点日趋进展,电源电压不断降低,工作电压和DRV之间的裕量也缩小了,导致使用这种技术的漏电流减少,大约仅减少2倍。

基本上,我们已经用尽了各种得以缓解漏电流的技术了,但“日益坐大”的SRAM容量仍将带来大量的电流浪费。图3显示CPU芯片上的SRAM容量每18个月增加一倍。

图3:随着片上SRAM容量不断增加,在50℃时预期会出现的SRAM漏电流。图中结果模拟自次10奈米CMOS中的晶体管漏电流资料

这两种SRAM的挑战,再上对于增加片上高速缓存速度和容量永无止境的需求,导致在成本和浪费能源的使用方面造成真正的挑战。这种需求同时来自行动和数据中心应用。由于电池寿命的限制,以往对于能源效率的需求显而易见,未来还会变得更重要。

由于深度学习而打造的DSA芯片应该可以为数据中心优化性能、成本和能效。除此之外,其芯片需要在前向传播时“晃动”数据,为用于矩阵/向量计算的处理器实现优化。以“目标”比较所取得的数据,然后再将“错误数据”“甩”回内存,以便用于下一个收敛周期。除了每秒Tera浮点运算(TFLOPS)的处理器之外,还需要越来越快的片上高速缓存,才能处理这种巨大的数据移动。

在许多此类DSA芯片平行运作的环境(例如数据中心)中,过程中如果效率不彰将导致数千安培的电流从主电源流向地面。这些大量浪费的漏电流自然会导致庞大的成本浪费。

对技术发展的影响

当代技术的发展带来了资料泛滥。它最主要的成长动力来自物联网(IoT)、5G、人工智能(AI)、扩增实境和虚拟现实(AR/VR)以及自动化。在大多数情况下,由于速度和能量的原因,数据必须储存在靠近CPU的位置,意即与CPU核心位于同一芯片上。唯一一种能够如此接近CPU的内存就是SRAM。

然而,SRAM由于效率不彰的尺寸和漏电流本质,导致这些成长驱动力的发展瓶颈。SRAM引起的速度和功率限制,阻碍了这些应用的明显进展,同时还不断地提高成本。这导致对于各种新兴内存替代技术的需求和投资与日俱增——特别是需要高效率的SRAM替代内存。

编译:Susan Hong,EET Taiwan

编按:本文作者Andrew Walke是Spin Memory [原Spin Transfer Technologies]产品营销副总裁