NOR闪存被广泛部署为FPGA的配置器件。工业、通信和汽车ADAS应用中使用的FPGA性能取决于NOR Flash的低延迟和高数据吞吐量特性。快速启动时间要求的一个典型例子是汽车环境下的摄像系统。汽车一发动,后视图像就要马上显示在仪表盘显示屏上,这是一个首要的设计挑战。

上电后,FPGA立即加载存储在NOR器件中的配置位流数据。传输完成后,FPGA转换到活动(已配置好)状态。FPGA包括许多配置接口选项,通常包括并行NOR总线和串行外设接口(SPI)总线。支持这些总线的存储器在不同制造商的产品之

最新发布的JEDEC xSPI规范是由所有主要的NOR闪存制造商联合开发的。新标准结束了数十年NOR闪存制造商独立开发产品而没有通用规范的局面。虽然存在细微差别,但核心JEDEC xSPI功能在所有制造商的存储器产品中都是一样的。JEDEC xSPI规范标准化了总线事务、命令和大量内部功能。结合高吞吐量性能,这些新一代闪存可实现全新的应用和功能。例如,赛普拉斯的Semper NOR Flash系列不但符合JEDEC xSPI规范,而且可提供持续的400MB/s读取传输速率,非常适合作为FPGA的配置存储器。为了直观说明这一点,400MB/s的数据速率能够在320ms内传输128MB(1Gb)的内容。

FPGA配置的历史

当FPGA首次出现时,可选的配置存储器要么是并行EPROM,要么是并行EEPROM产品。随着时间的推移,NOR闪存技术开始出现,并因其系统内可重编程性和成本优势而被广泛采用。第二个演化是SPI存储接口在大多数应用中取代了并行NOR接口。今天的SPI存储产品具有高密度、小封装尺寸、高读取吞吐量等优点,最重要也许是其高效的低引脚数接口。

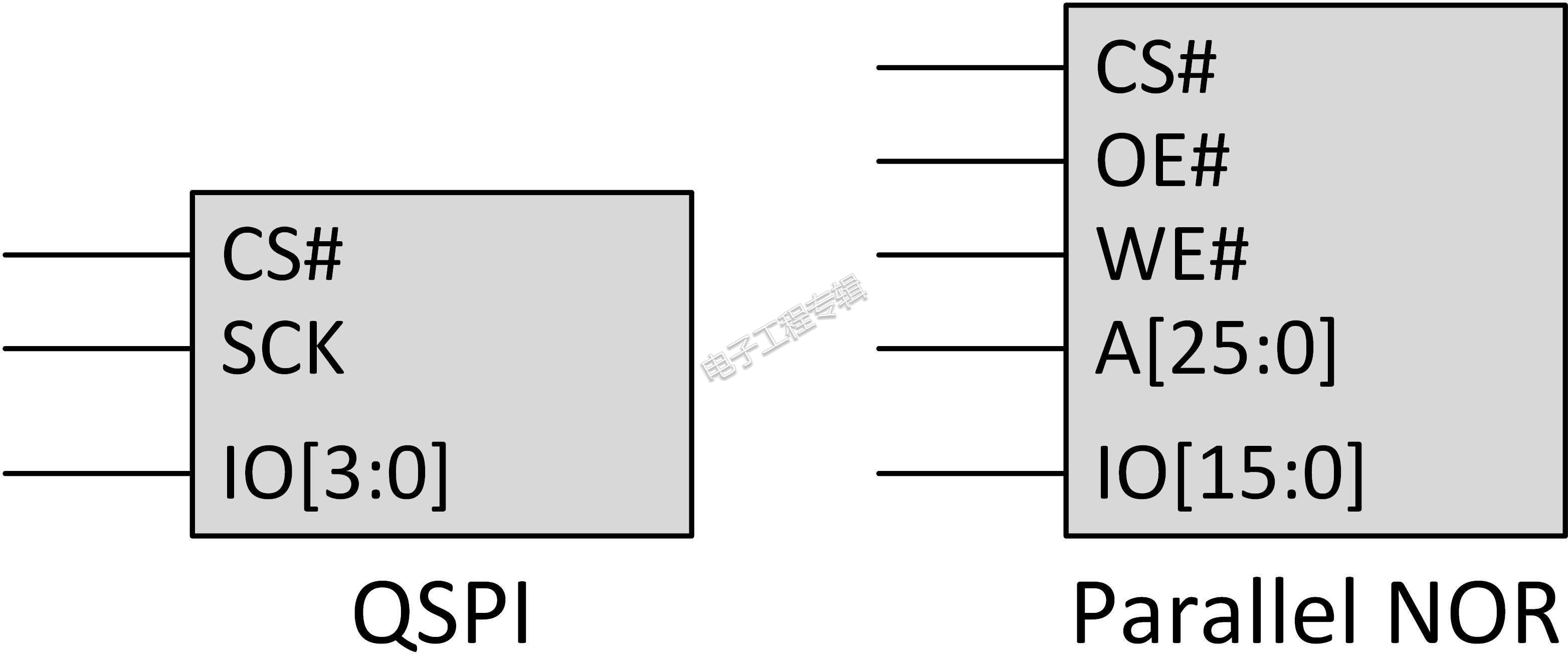

图1:千兆位四SPI(6引脚)和并行NOR(45引脚)接口(来源:赛普拉斯半导体)

图1示出了与千兆位并行NOR产品相对比的千兆位SPI器件的引脚排列。对于千兆位存储器,四串行外设接口(QSPI)器件带有一个6引脚接口,而并行NOR器件需要45个引脚。 引脚数量的极大减少让QSPI器件被广泛采用,成为首选的配置接口。QSPI接口可在不改变器件占用空间的情况下改变密度。

FPGA配置速度

随着工艺节点不断缩小,FPGA器件继续增加可用的可编程逻辑量。这就要求更高密度和更快速度的配置存储器。现代FPGA在配置期间需要加载多达128MB的数据。这些高密度配置比特流需要更长的时间才能从NOR闪存传输到FPGA。 配置接口不仅要针对读取吞吐量进行优化,还必须确保不同制造商的NOR闪存之间的互操作性。

SPI读取吞吐量

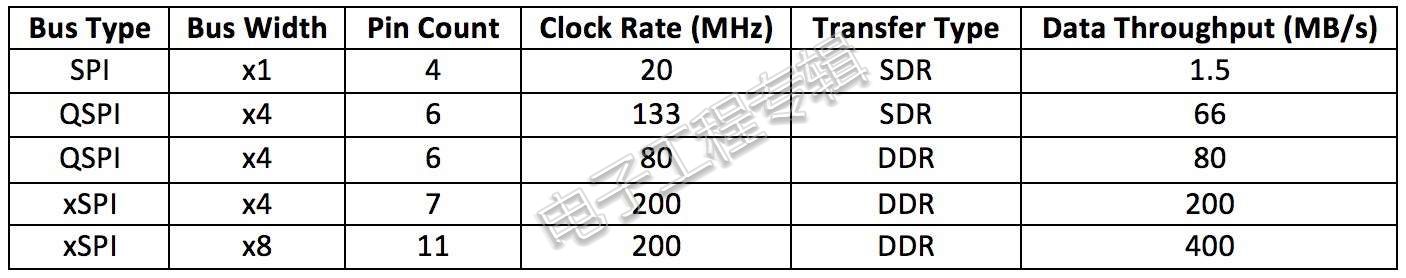

SPI读取吞吐量在过去几年中急剧提升,从最初运行在×1模式的SPI接口,一直到运行×4 DDR的现代QSPI存储器。从表1中可以看出,下一代闪存器件能够达到更高的SPI总线性能。

表1:闪存器件的SPI读取吞吐量选项。(来源:赛普拉斯半导体)

现代SPI器件能够被永久配置为固定总线宽度和传输类型,可在上电时立即运行。FPGA必须支持这一永久配置特性,以便在上电后立即开始配置过程。

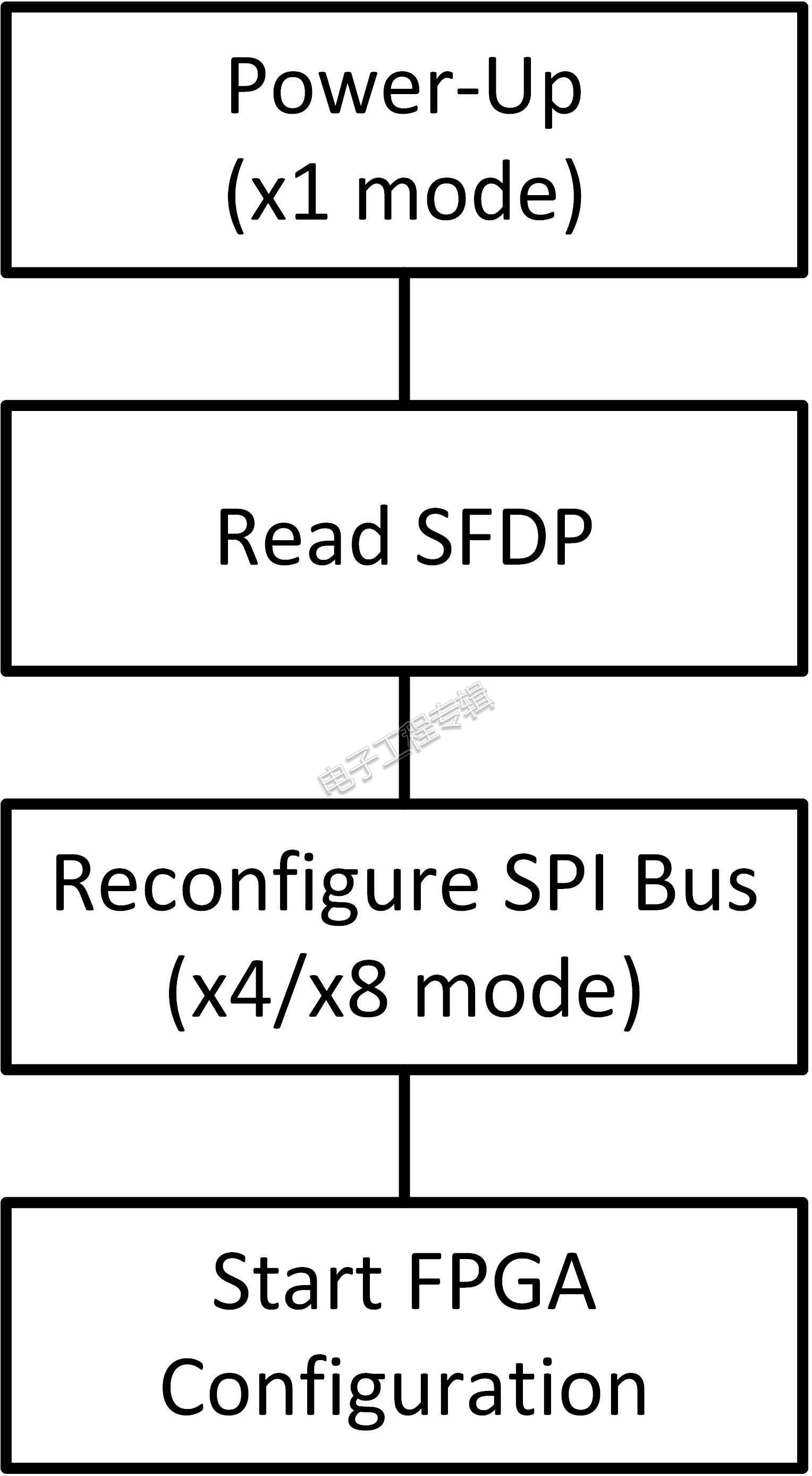

或者,SPI存储器可以在×1模式下退出上电,允许主系统(FPGA)查询存储器中的串行闪存可发现参数(SFDP)表中的特性。这种×1模式已成为多个存储器供应商支持的标准功能,而且可以让FPGA检索有关器件功能的关键信息。 一旦检索到器件特性,就可以快速重新配置FPGA存储控制器和SPI存储器件,以获得最大的读取性能。

图2:串行闪存可发现参数(SFDP)表用于在上电时配置SPI总线功能。 (来源:赛普拉斯半导体)

下一代闪存器件可以工作于×1、×4或×8总线宽度,并支持SDR或DDR传输类型,在使用中利用集成的SFDP表检索关键器件信息至关重要。选择哪种总线宽度和传输类型必须与FPGA上实施的总线接口配置保持一致。

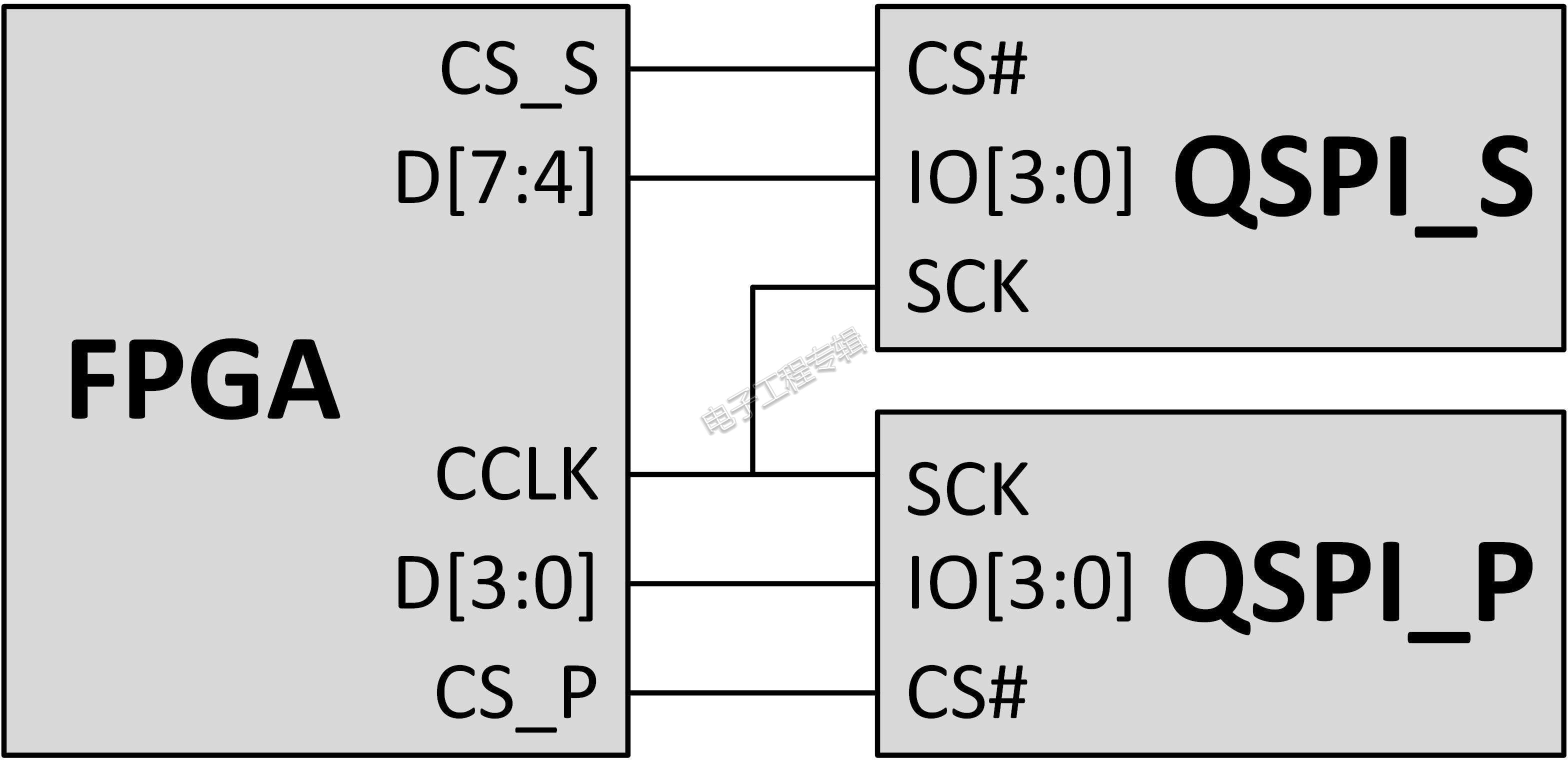

双QSPI配置接口

为了缩短FPGA配置时间,许多现代FPGA允许将配置位流划分到两个QSPI器件(图3)。 这两个QSPI器件以并行方式连接,其中位流的低半字节存储在“主”QSPI器件(QSPI_P)中,而位流的高半字节存储在“辅助”QSPI器件(QSPI_S)中。这两个器件在加载位流时并行运行,从而有效地使读取数据传输速率加倍。

请注意,除了共享的SCK线之外,接口基本上是独立于这两个器件的。实施共享SCK线的目的是在并行(即,同时)方式下读取器件时最小化时序偏差。 当使用相同的目标地址执行相同的操作时,可以一次一个地对器件访问,或者同时对两个器件进行访问。

图3 :双QSPI配置接口(11个引脚)允许配置位流在两个QSPI器件之间进行划分,从而有效地将读取数据传输速率提高一倍。 (来源:赛普拉斯半导体)

当大型FPGA器件需要以最快的方式传输大配置(即高密度)位流时,这种11引脚的双QSPI配置很有吸引力。

闪存配置

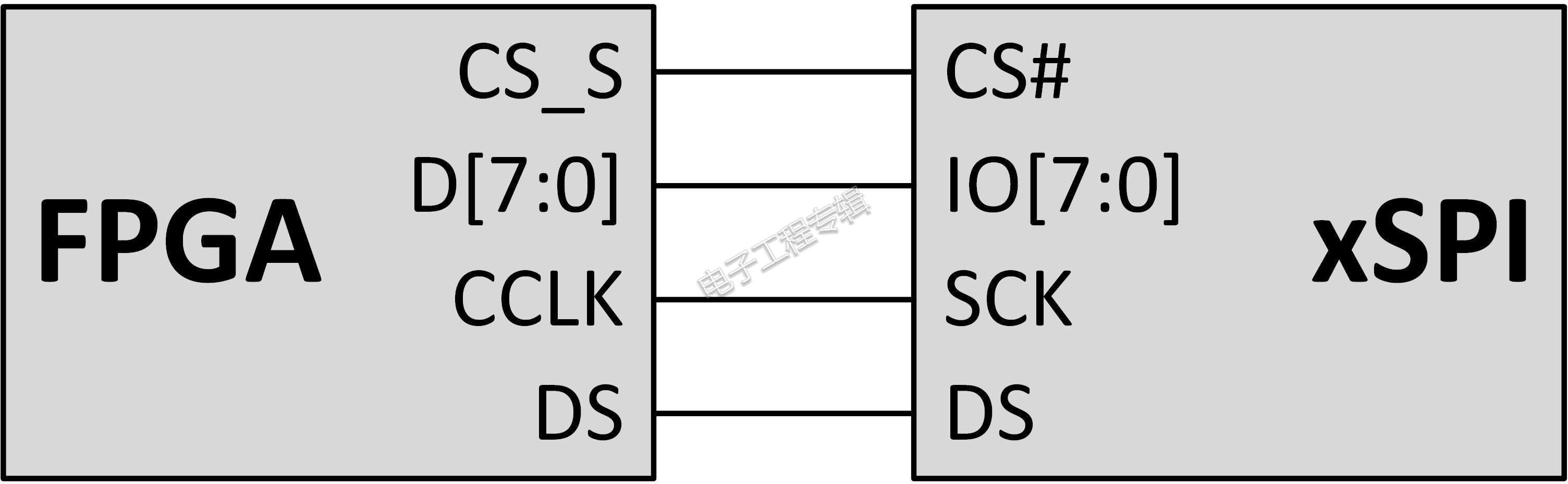

下一代闪存可以×1(主要用于SFDP访问)、×4或×8 IO总线宽度运行。数据可以SDR或DDR格式传输,并且使用新的数据选通信号以有助于高速传输。 例如,赛普拉斯的Semper NOR闪存器件的八进制配置使用11引脚接口(见图4)。

图4:使用低引脚数接口,可以SDR或DDR格式,按照×1、×4或×8 IO总线宽度来传输数据。 这里显示的是采用11引脚接口的赛普拉斯Semper NOR闪存的八进制配置。 (来源:赛普拉斯半导体)

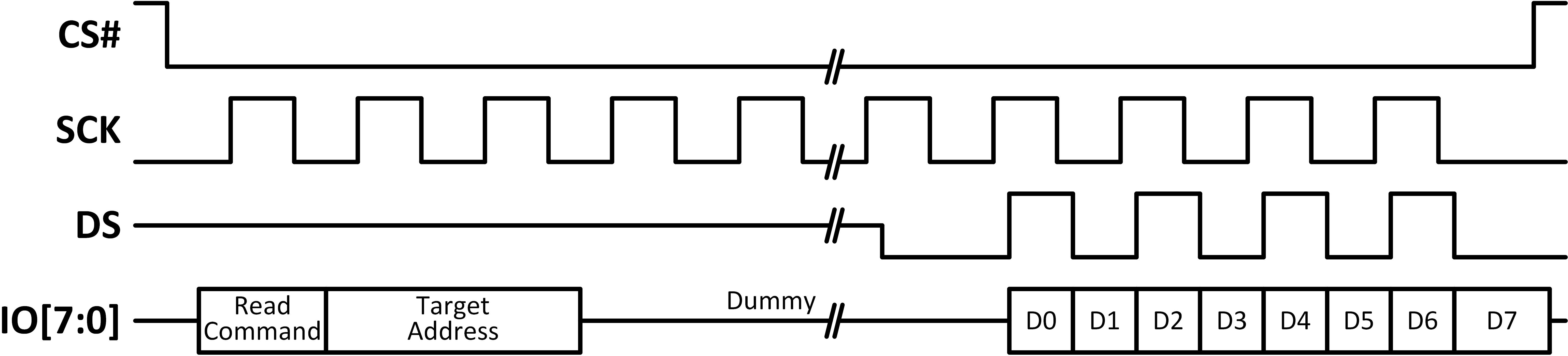

必须将新的Data Strobe合并到FPGA配置接口中,以充分利用下一代Flash器件的高吞吐量读取性能。数据选通与输出读取数据边缘对齐,其方式与低功耗DDR DRAM器件使用的选通方式相同(见图5)。Data Strobe可以“绘制”数据眼图,并让FPGA以高时钟速率有效地捕获数据。

图5:具有数据选通功能的×8 DDR读取事务与输出读取数据边缘对齐,使FPGA能够以高时钟速率有效捕获数据。 (来源:赛普拉斯半导体)

一个非常适合FPGA配置的闪存功能是可支持连续读取操作。连续读取开始于主机(MCU或FPGA)启动CS#,然后发出读取命令,后面带着目标地址。经过多次延迟周期,存储器从目标地址输出数据。如果主机继续切换时钟,那么存储器将通过从下一个顺序地址输出数据做出响应。只要时钟继续切换,存储器将继续从顺序地址输出数据。 这种顺序读取功能可以通过单个读取事务对FPGA进行配置。

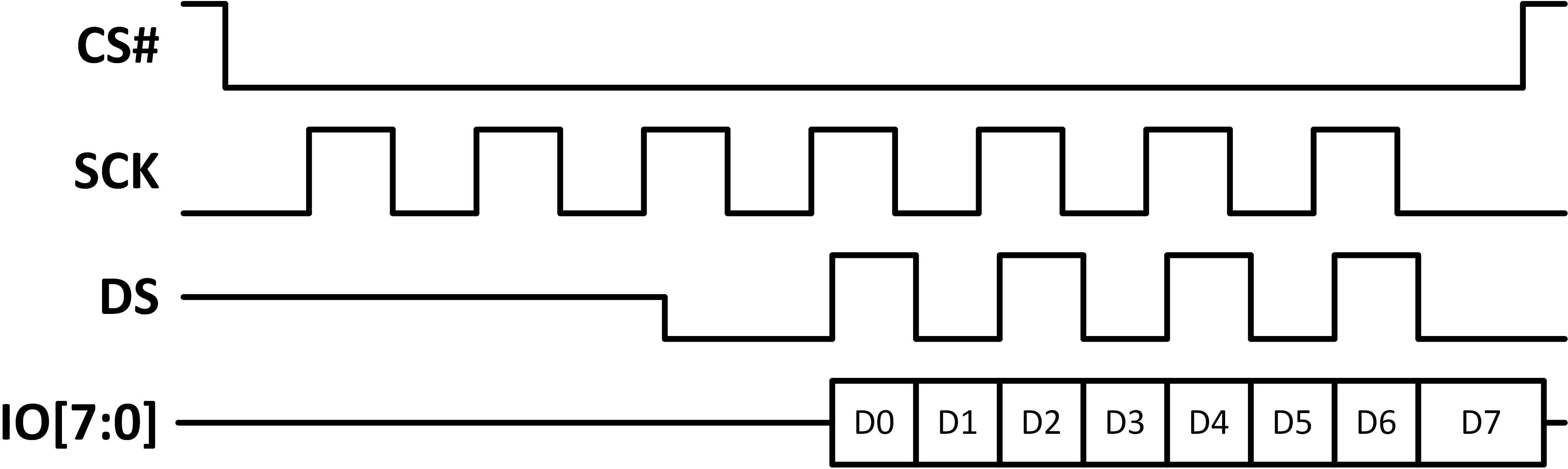

另一个有助于FPGA配置的功能是AutoBoot。AutoBoot在上电复位期间从预先配置的目标地址执行自动读取操作,然后在第一次启动CS#时立即输出数据(见图6)。这一功能对需要简单配置机制的ASIC器件也很有用。一旦CS#被置位,内存将返回到其待机状态,并以正常方式处理后续操作。

图6 :Autoboot读取功能(具有3个预热周期)正在运行中。(来源:赛普拉斯半导体)

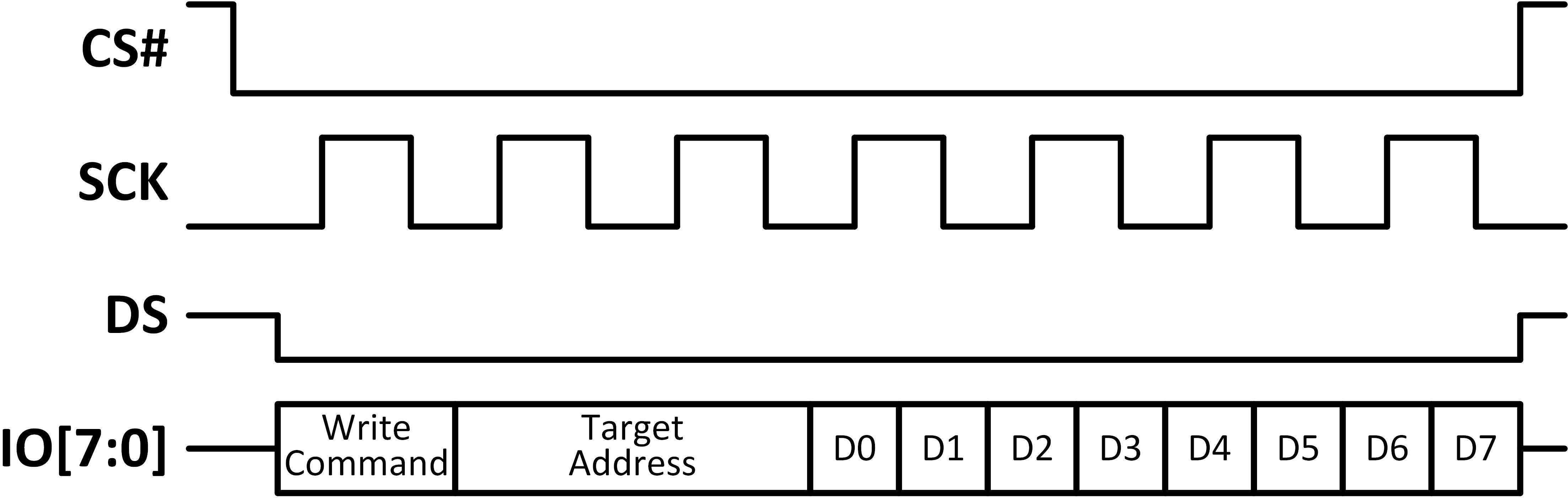

NOR Flash器件的写入事务(参见图7)与标准SPI操作几乎完全相同,但有两个例外。 首先,在整个事务期间必须将新的Data Strobe信号驱动为低电平。 其次,当配置为DDR操作时,数据被写为字(16b),而不是传统SPI产品上的字节编写粒度。

图7:NOR Flash的写事务要求在整个事务期间将Data Strobe信号驱动为低电平,并且在配置为DDR操作时将数据写为16位字。(来源:赛普拉斯半导体)

下一代NOR闪存器件的高吞吐量性能可满足大规模FPGA应用的高密度和即时启动要求。所有主要的NOR闪存制造商都参与了JEDEC xSPI规范的开发,这为OEM厂商提供了更多的采购选择。JEDEC xSPI规范涵盖了上述八进制SPI接口,以及HyperBus接口,两者均提供400MB/s的读取吞吐量。已实现的读取吞吐量远远高于传统SPI产品。需要对FPGA SPI控制器进行修改以充分利用其高速配置。需要考虑的新功能包括DDR数据速率、用于数据捕获的新数据选通引脚,以及扩展的×8总线接口。此外,一些NOR闪存器件(例如赛普拉斯的Semper NOR系列)允许在实施双QSPI配置架构时去除其中一个QSPI器件。在需要快速FPGA配置时间,以及执行实时重新配置的FPGA应用中,下一代闪存提供的性能具有很大的吸引力。

本文同步刊登于《电子工程专辑》2018年12月刊杂志

________________________________________

关于作者:

本文作者Cliff Zitlaw从事半导体存储器的开发已有36年。Cliff的主要研究焦点是总线接口,可以在不同的应用约束条件下优化存储性能。Cliff是Xicor微处理器串行存储器接口(EEPROM)、Micron CellularRAM接口(PSRAM)和赛普拉斯Hyperbus接口(NOR和PSRAM)的发明人。Cliff是49项跟存储功能和用法相关的专利作者或合着者。闲暇时,Cliff喜欢吃BBQ、看电视,周六小睡一把。