继台积电(TSMC)于本月初投片采用EUV微影技术的首款7+纳米芯片后,三星电子(Samsung)也宣布投片并逐步量产多款7纳米(nm) EUV芯片。为了迎头赶上台积电的生态系统,三星还将大力支持其IP和EDA基础设施,并详细介绍其封装能力。

在本周于美国硅谷举行的Samsung Tech Day上,三星宣布采用EUV的7纳米LPP (Low Power Plus)工艺研发完成,正式进入商用化量产,未来也将在此技术基础上朝5nm、3nm前进。此外,三星并宣布出样基于其16-Gbit DRAM芯片的256-GByte RDIMM,并计划采用内建赛灵思(Xilinx) FPGA的固态硬盘(SSD)。

不过,7nm商用化量产还是此次活动的亮点,再加上该公司内部开发的EUV光罩检测系统,正象征着三星的一个发展里程碑。

相较于其10nm节点,三星的7LPP工艺能缩小多达40%的芯片面积,速度提高20%,并降低50%的功耗。此外,三星表示目前拥有50家代工合作伙伴,包括Ansys、Arm、Cadence (拥有7nm数字和模拟设计流程)、Mentor、Synopsys和VeriSilicon,均表示采用7nm工艺投片。

据称7LPP工艺吸引了多方的兴趣,包括网络巨擘、网络公司和高通(Qualcomm)等手机供货商等客户。然而,三星预计最早要到明年年初之后,才可能会有客户发布相关消息。

三星代工营销总监Bob Stear表示,自今年初华城S3厂引进EUV设备以来,EUV系统一直维持在支持250W光源。目前的功率级可将产量提高到生产1,500片晶圆/天。他说,从那以后,EUV系统逐渐可达到280W峰值,而三星的目标是进一步提高功率到300W

三星华城S3厂EUV产线(来源:Samsung)

Stear指出,相较于传统氟化氩(ArF)系统需要五层光罩,EUV所需的层数较少,因此降低了成本而使得良率提升。不过,该技术节点在前段工艺(FEOL)仍然需要进行多重曝光。

三星开发了自家的系统,用于比较并调整预期和实际的光罩图案,以加速其EUV投产。由于目前尚不清楚它是否与典型的第三方检测系统一样自动化,VLSI Research首席执行官G. Dan Hutcheson认为它更像是一套光罩检查系统。

三星预计其7nm节点将在今年年底前通过Grade 1 AEC-Q100汽车标准。在封装方面,三星正在开发一种重分布层(RDL)中介层,可在单个组件上安装多达8个高带宽内存(HBM)堆栈。该公司并致力于在基板中嵌入被动组件,以节省数据中心芯片的空间。

三星代工营销总监Bob Stear展示三星S3厂生产的7nm EUV晶圆(来源:EE Times)

EUV光罩护膜可能延迟5nm?

市场研究机构International Business Strategies (IBS)首席执行官Handel Jones说,三星和台积电在7nm阶段都可能只将EUV用于两个芯片层,因为光罩护薄还在开发中,因此至今还未能使用。到了5nm时,他们很可能将EUV扩展至6层,但这至少要到2021年后了,届时的光罩护膜将有足够的耐用性和光传输能力。

Jones说:“三星大约提前了六个月采用EUV工艺,因为他们一直在DRAM和逻辑工艺中使用这一系统,但台积电在使用IP和工具方面处于领先地位,而且也有更多的客户合作关系,如超威(AMD)、苹果(Apple)、海思(HiSilicon)和英伟达(Nvidia)等。”

另一位分析师表示,思科(Cisco)原本是IBM代工业务的客户,目前正与台积电合作开发7nm产品。而高通的7nm设计预计将分别交由台积电和三星代工。

尽管如此,Jones预测这家韩国巨擘的营收可望在今年达到900亿美元,甚至到2027年可能超过1,500亿美元。从三星内存业务的成长力道来看,Jones估计其DRAM和NAND销售将分别达到50%的和45%的占有率。

三星可望顺利在明年6月之前开始量产5nm和4nm节点,在相同的技术基础上实现突破性的进展。Stear说,这一工艺节点的PDK预计在今年年底前发布,并将在S3厂旁为EUV打造另一条产线。

这三种工艺节点将使触点更接近并最终移动到闸极上方,以增加密度并减少金属间距。这是英特尔(Intel)先前针对其10nm节点所讨论的一种方法,但尚未量产。

Stear说:“我们正逐步处理闸极上触点(contact-over-gate)。正如有些人发现的,这是一个难以解决的问题。”

三星于今年5月宣布计划转向闸极全环(gate-all-around;GAA)晶体管,或称为纳米片,用于3nm节点。其目标在于将标称电压降至新低点,以持续降低功率。预计在今年六月就能提供用于3nm节点的第一版0.1 PDK。

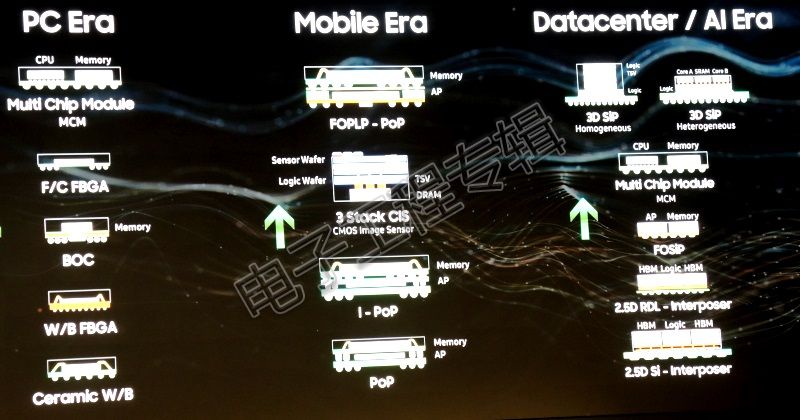

三星介绍内部开发的一系列封装技术进展

内存发展蓝图

在其核心内存业务方面,三星表示开始出样采用其16-Gbit芯片制造的256GB RDIMM。这些储存卡能以高达3,200MHz的DDR4速度运行,支持50ns读写,应该可以在今年年底前投产。

这些内存芯片采用一年前发布的1y纳米工艺制造。但未来1y工艺是否导入EUV,目前尚不清楚。然而,三星DRAM开发主管Seong Jin Jang指出,后续的1z和1a工艺节点将越来越广泛地使用EUV。

三星并展示在AMD EPYC服务器上运行的八个DIMM。相较于其现有的128GB卡在225W时提供380万次运算/秒,这些DIMM则能在170W时达到每秒320万次运算。

最终,三星的目标是将DIMM提高到768GBytes,最终在于使HBM数据速率从目前的307GB/s提高到512GB/s。他并补充说,GDDR6绘图内存将从目前的18Gbits/s提高到22Gbits/s,而LPDDR内存功耗则将从24mW/GB降至12mW/GB,但他并透露何时实现。

此外,三星宣布计划采用嵌入式Xilinx Zynq FPGA的智能SSD,将性能提升2.8倍至3.3倍。这些装置适用于各种数据库、AI、视讯和储存等应用。

该公司表示,该SSD将提供一种更易于扩展性能的方法,而不必再采用标准FPGA搭配独立加速器的作法。目前仍在原型阶段的这些SSD产品将采用各种密度和中阶FPGA。

三星所谓的智能SSD目前都还只是原型,并未透露任何规格或何时推出

编译:Susan Hong,EET Taiwan

物联网、人工智能、AR 、云计算等正颠覆着我们的世界。11月8-9日,“全球双峰会” 请来世界范围内极具影响力的业界领袖人物,齐聚中国电子创新之都 -- 深圳,探索影响未来的技术与趋势,讨论电子行业在新时代面对的机遇与挑战,同时将表彰对电子创新与发展做出重要贡献的企业和人士。 诚邀国内外企业高管、工程师及技术、采购决策人员一起进行思想的碰撞和交流!

点击下图报名

关注最前沿的电子设计资讯,请关注“电子工程专辑微信公众号”