汽车行业发展创新突飞猛进,从底盘到动力总成,从信息娱乐系统到联网和自动化系统,汽车设计的方方面面都有着日新月异的进步。然而,为人诟病的电动汽车(EV)充电用时问题(特别是在旅途中充电)带来的巨大不便,阻碍了电动汽车的推广普及,因此,车载充电器(OBC)设计或许将成为备受关注的领域。

同应对大多数工程挑战一样,设计人员把目光投向先进技术,以期利用现代技术以及诸如碳化硅(SiC)和氮化镓(GaN)等宽禁带(WBG)材料来提供解决方案。但半导体材料只是解决方案的一部分。任何车载充电器设计想要充分发挥其在功率密度和能效方面的潜力,都离不开高效散热设计。

在本技术白皮书中,英飞凌审视了车载充电器设计人员面临的挑战,细致深入地考察了半导体封装对于打造解决方案所起的作用。本文还探讨了一种顶部散热的创新方法,该方法可用于一系列高性能元器件,以供设计人员选用。

现代电动汽车车载充电器设计面临的挑战

车载充电器的作用是将来自电网的交流电转换为直流电,以用于为动力电池充电。车载充电器仅在汽车停放并连接充电电缆时执行这项功能。汽车行驶时则只能一路载着这个重物,因此,必须最大限度地减小车载充电器的尺寸和重量,以减轻其对续航里程的影响,同时又能实现快速高效充电。另一个挑战是车载充电器功率等级增长迅猛。几年前,3.6 kW还是最先进的技术,而在不久的将来,功率将提高至三倍左右,也就是说,在占用相同空间的情况下,功率可达到11 kW。

车载充电器设计人员面临着五大相互关联的挑战。其中,提高功率密度尤为重要,因为这意味着可缩小尺寸和降低重量,而这有助于延长电动汽车续航里程。提高能效不仅可以减少车载充电器内部的热量积聚(这降低了散热管理要求,因而可以减小车载充电器的尺寸并相应地提高功率密度),还能从电网供给更多电能为动力电池充电,从而缩短实际充电时间。

动力电池电压不断提高,典型电压已从400 V升至800 V,这主要是为了降低充电时和向主驱电机输送电能时电缆中传输的电流及相关I2R损耗。

图1:OBC设计对电力电子设计人员提出了一系列挑战

双向运行要求对车载充电器设计人员提出了另一个挑战。随着电动汽车越来越普及,电网承受的压力将大幅增加,特别是人们可能会在同一时段给汽车充电(譬如,每天通勤结束后在夜间充电)。电力供应商认识到,电动汽车中储存的大量电能,既可以用于稳定交流电网,也可以在高峰时段为住宅供电,以降低用电峰值需求。此外,当交流电网发生故障(停电)时,电动汽车可以充当“家用电池”。然而,要做到这一点,车载充电器需要在接收电能之外,还能从动力电池馈出电能。

为了应对这些挑战,拓扑和技术的选用都很重要,特别是对于开关元件。在大多数情况下,WBG解决方案将有助于提供所需要的性能优势。

然而,虽然知道WBG技术的益处,设计人员还必须考虑,改善散热性能对于实现这些重要目标有着至关重要的作用。

顶部散热——概述和优点

汽车环境对于电子组件存在很多危害因素,包括灰尘、污垢和液体,有鉴于此,电动汽车中的大多数电子系统都通过密封加以保护。这种情况不允许使用强制风冷式散热,因此,散热管理通常是将大功率元器件产生的热量传导至电动汽车内的冷却液。

一般来说,大功率SMD元器件的导热路径是从功率器件向下传导至PCB,PCB则键合在散热板上。这种方式被称为“底部散热”(BSC)。在散热任务艰巨的应用中,可以将功率器件贴装在绝缘金属基板(IMS)上,这样做可以优化散热性能,因为绝缘金属基板的导热性优于带散热通孔的FR4。然而,底部散热方法总是要在散热性能与电路板空间利用率之间谋求折衷。

通过创新封装,英飞凌研制出适用于功率分立器件和功率IC的顶部散热(TSC)技术。这项技术有许多优点,所有这些优点都能让车载充电器设计和其他类似应用受益。

底部散热通常将散热板安装到PCB/IMS底部进行散热。这样就有一个面不能放置元件,因而使功率密度降低一半。半导体器件与PCB键合在一起散热,意味着它们将在相同温度下工作。FR4的Tg低于许多现代功率器件的工作温度,这限制了这些器件充分发挥其潜力。

图2:TSC允许将元器件放置在电路板的两个面,从而使功率密度翻番

通过将散热板键合在功率元器件的顶部,这些问题迎刃而解,不仅两面都可以放置元器件,而且WBG器件能够在其整个工作温度范围内运行。

虽然IMS的散热性能优于FR4,但它也加剧了复杂度。事实上,许多IMS解决方案都变成多板装配,即,IMS仅用于功率器件,FR4则用于驱动器和无源器件。这令设计和制造变得极为复杂。然而,最近的一份拆解报告显示,现实中的这种装配使用了169个连接器——而等效的顶部散热设计只需要41个。

图3:简洁的TSC装配所需连接数量可减少最多76%

改为单板TSC设计可以少用128个连接器,这既节省了成本又降低了复杂度,而且在无形中化解了这些连接器造成的可靠性问题。还省下了IMS的成本,根据拆解报告的分析,装配成本降低了三分之一。

散热设计的关键参数是半导体结与散热板之间的热阻,因为这个参数定义了传导热量的能力。散热仿真表明,在FR4上采用顶部散热的热阻,比在FR4上采用底部散热改善了35%,甚至比在IMS上采用底部散热也略有改善,而成本却大大降低。

图4:尽管成本更低,TSC的性能却优于底部散热IMS设计

FR4本身的散热限制与此有关,这是一项安全要求。在底部散热方案中,MOSFET键合在FR4上,这意味着FR4的温度非常接近于半导体结温。FR4的温度限制意味着MOSFET的工作温度亦受限于此,因而无法充分发挥其潜力。在顶部散热方案中,MOSFET与FR4并未键合在一起散热,因此MOSFET可以在更高温度下运行。

使用IMS时通常需要将驱动器和无源器件贴装在单独的FR4 PCB上,因此,栅极驱动器与MOSFET之间可能存在较大距离,这不可避免地加剧了寄生效应,从而导致振铃。

图5:采用顶部散热的SMD功率器件可缩短栅极轨迹,减少寄生效应

TSC允许将所有元器件放置在同一个双面PCB上,因此,可以将驱动器直接放置在相应的MOSFET的下方,从而显著减少PCB引起的寄生效应。这将提升系统性能,产生更干净的波形,从而降低功率元器件上的电气应力。

装配考虑事项

如前文所讨论的,典型的TSC装配通常比等效的底部散热方案更为简单,其中一个很重要的原因是它仅使用一个电路板并且所需连接数量显著减少。

直接将散热片安装到位于PCB顶部的发热MOSFET封装上进行散热。薄型元件也放置在这一侧,厚型元件则放置在下面。英飞凌在开发HDSOP系列时,已确保每个元件的标称高度均为2.3 mm。这样的统一高度大大简化了散热板,无需进行机械加工,即使在同一个设计中使用了不同的功率半导体技术,也可以使用更为优化的散热片。

图6:所有HDSOP器件均实现统一高度大大简化了散热片设计和装配

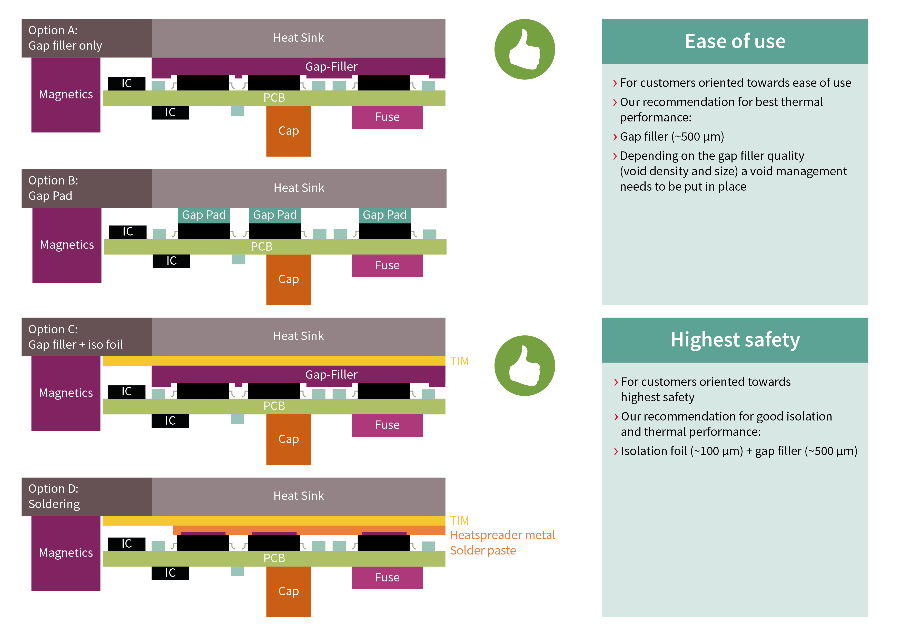

有多种方法可将MOSFET封装与散热板键合到一起进行散热。一般而言,最简单的方法是在MOSFET与散热片之间放置一个导热填缝垫片。经优化的填缝料高度可以实现最佳散热性能,但前提条件是填缝料填满不留空隙。此外,液体填缝材料可用于全自动生产线。

图7:填缝料是首选散热键合方法,加装绝缘片可满足更高安全要求

尽管填缝料已能够在MOSFET与导热散热片之间实现足够的电隔离,还可以在填缝料与散热片之间加装一片绝缘垫片,以便在不明显降低散热性能的情况下提供适当的电气隔离水平,从而满足更高安全要求。

英飞凌QDPAK——高级TSC解决方案

英飞凌QDPAK器件经专门设计,可以充分利用TSC的优势,并提供多种特性以满足不同应用的要求。这个系列的器件均为标称尺寸20.96 mm x 15.00 mm、统一高度2.3 mm,以便轻松装配。

QDPAK器件能够实现高功率耗散,并且具备多个专门用于漏极和源极连接的引脚,因此它们非常适于大电流工作。采用开尔文源极引脚来确保高度可控性和满载效率,以支持高频工作,实现功率密度目标。对称平行引线布局确保了PCB的机械稳定性,同时也便于装配和测试。

图8:实现了顶部散热(TSC)的QDPAK可为制造/装配带来许多益处

图8:实现了顶部散热(TSC)的QDPAK可为制造/装配带来许多益处

作为标准参数,QDPAK(PG-HDSOP-22-1)可在最高450 V工作电压下提供3.20 mm爬电距离,适用于400 V以下电池电压等级的大多数应用。对于更具挑战性的应用,HV QDPAK(PG-HDSOP-22-3)采用I级塑封料,并在封装中留出凹槽,使爬电距离增至4.80 mm,可支持950 V工作电压。

总结

虽然在利用功率解决方案来不断提高能效和功率密度这场较量中,宽禁带(WBG)半导体材料占据了新闻头条,但高效散热管理在实现电气性能以及降低尺寸、重量和成本方面起着重要作用。

创新封装设计,如英飞凌的QDPAK,可以实现顶部散热(TSC)。在这种设计中,热量从封装顶部经由导热介质直接流向散热板。这种方法有许多优点,包括散热性能优于等效的IMS解决方案。更为简洁的结构避免了多板装配,减少了元器件数量和成本(尤其是连接器)。得益于此,性能显著提高,装配时间和成本也有所缩短和降低。通过充分利用电路板的两个面,大幅提高了功率密度,同时也减少了系统中的寄生元素。

虽然顶部散热(TSC)可能看起来很“新”,并且在许多方面确实很“新”,但这个解决方案真正的优点在于,它使用经反复检验的技术,如填缝料或结合导热介质,打造出既简练又极为可靠的解决方案。

欢迎浏览英飞凌QDPAK产品页面,进一步了解我们面向大功率应用的创新顶部散热SMD解决方案,以及这些解决方案搭配我们最新推出的高压CoolMOS™超结MOSFET和CoolSiC™技术所能带来的关键特性和益处。

作者:英飞凌科技全球电动汽车充电应用经理Daniel Makus、英飞凌科技高压功率转换高级应用工程师Severin Kampl