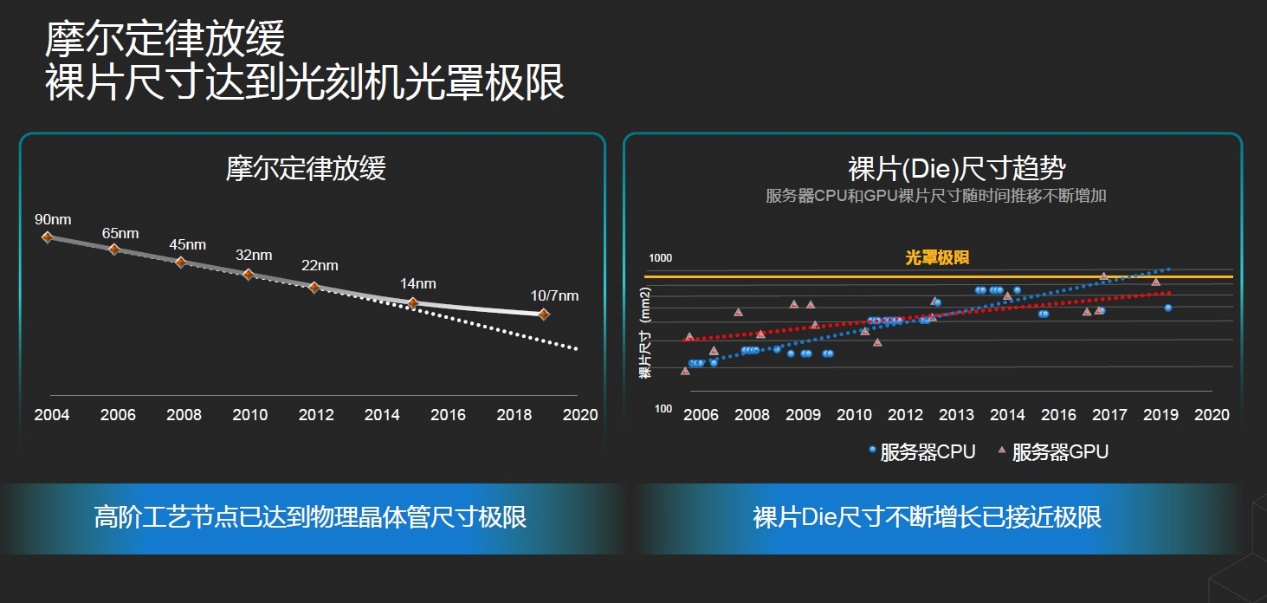

2019年8月,AMD CEO Lisa Su博士在Hotchips会议上发表题为《交付高性能计算的未来》的演讲时指出,从2012年开始,摩尔定律就逐渐放缓了前进的步伐,随着先进工艺节点向10/7nm制程迈进,偏差也变得越来越大,预示着高阶工艺节点已经达到物理晶体管尺寸极限。但与此同时,随着服务器CPU、GPU等芯片功能日趋丰富,性能日趋强悍,其裸片(Die)尺寸却在不断增长,正在逼近光刻机光罩尺寸的极限。

也就是说,两者之间的矛盾正变得越来越不可调和。一方面,晶体管微缩工艺难度猛增,导致晶体管容量增加遇到瓶颈;另一方面,日趋丰富的功能需求却需要越来越大的裸片尺寸,直逼光罩极限。

半导体行业中常常以“一美元所做出来晶体管长度之和”来直观展示摩尔定律。数据显示,2002年,当时的主流工艺为180纳米,一美元做出来所有的晶体管长度总和是2.6米;到了2012年,采用28纳米工艺时,长度变为20米。此后,到2014年采用20纳米工艺时,这一数字未发生任何变化,开始进入停滞阶段,近年来甚至呈现出明显的下降趋势。如果从经济学角度来解读的话,这意味着芯片的成本正在不断增加。

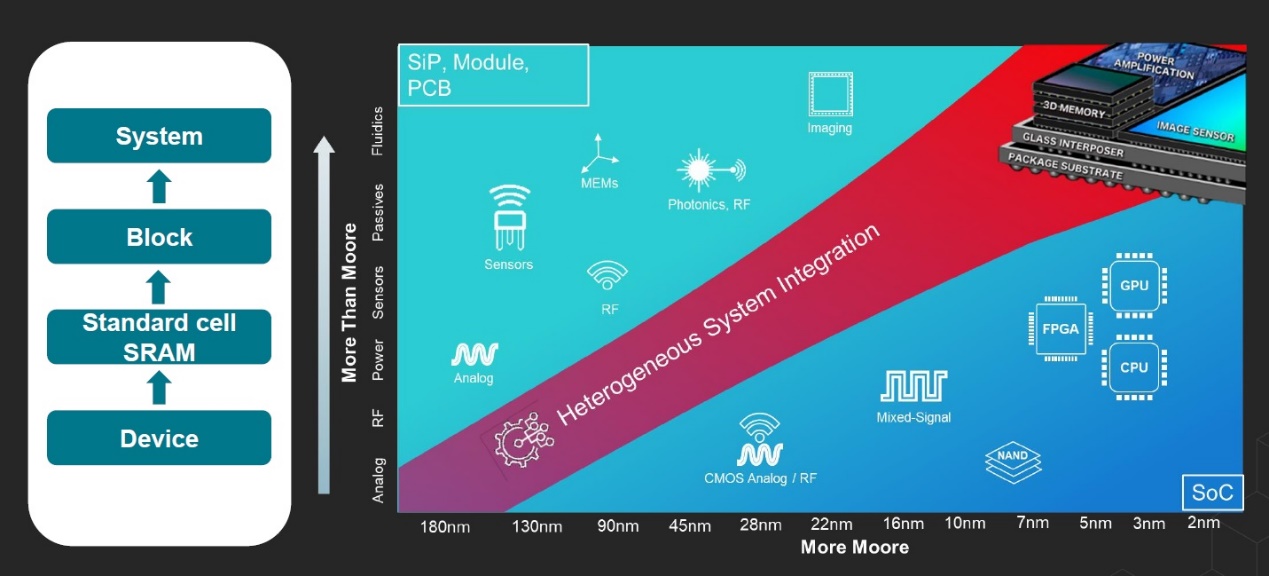

众所周知,一颗芯片通常由下至上被分为四个层次,依次是最低层的器件、标准单元库/片上SRAM、构件(Block)和系统,如下图左侧所示。所以,要想让摩尔定律在未来能够继续发挥指导作用,只能从两个维度实现突破:一个是More Moore(深度摩尔),铝-铜-HighK-FinFET-GA工艺的演进即为最好证明;另一个则是More than Moore(超越摩尔),即从系统角度出发,通过2.5D/3D堆叠、Chiplet和先进封装等技术,增加单位面积上的晶体管密度和功能。

从2D走向3D的优势是显而易见的,包括更短的引线、更低的功耗、更高的带宽、更小的封装尺寸等等。但Cadence公司数字与签核事业部产品工程资深群总监刘淼日前在接受《电子工程专辑》采访时也指出,对设计厂商和封装企业来说,3D-IC会带来很多挑战,比如裸片放置与Bump(凸点)规划、SoC和封装团队各自为战、缺少统一的数据库、跨芯片/Chiplet及封装的热分析、系统级裸片连接验证、设计复杂程度上升等。

Cadence公司数字与签核事业部产品工程资深群总监刘淼

集成化、高容量3D-IC平台

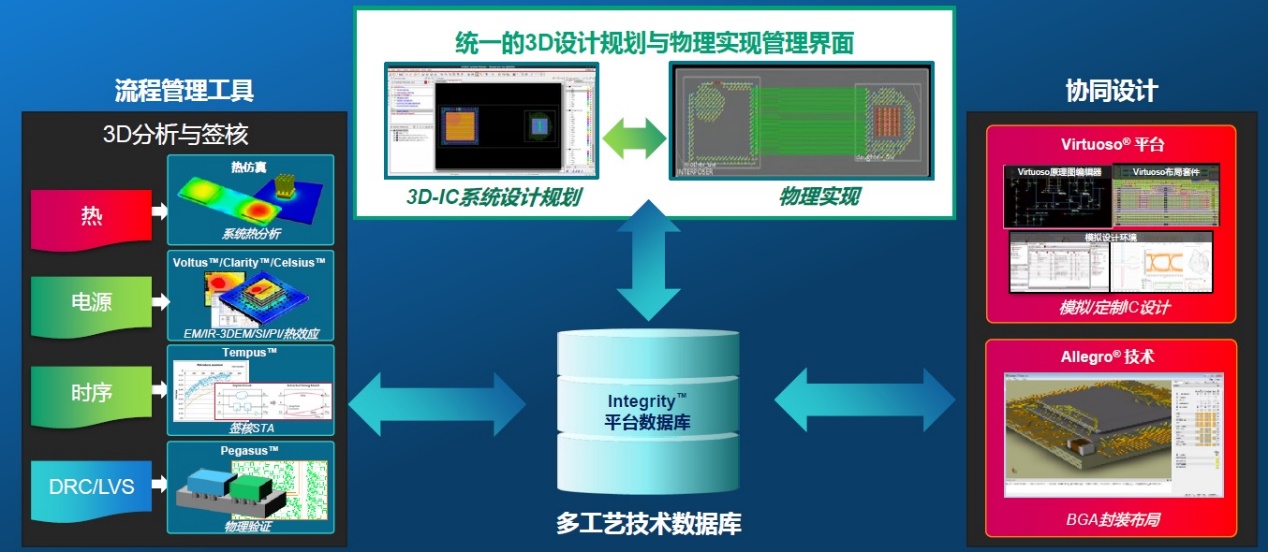

为此,Cadence公司日前向业界正式交付了全新的Cadence Integrity 3D-IC平台。这是业界首款完整的高容量3D-IC平台,将设计规划、物理实现和系统分析统一集成于单个管理界面中,客户可以利用平台集成的热、功耗和静态时序分析功能,优化受系统驱动的小芯片的功耗、性能和面积目标(PPA)。

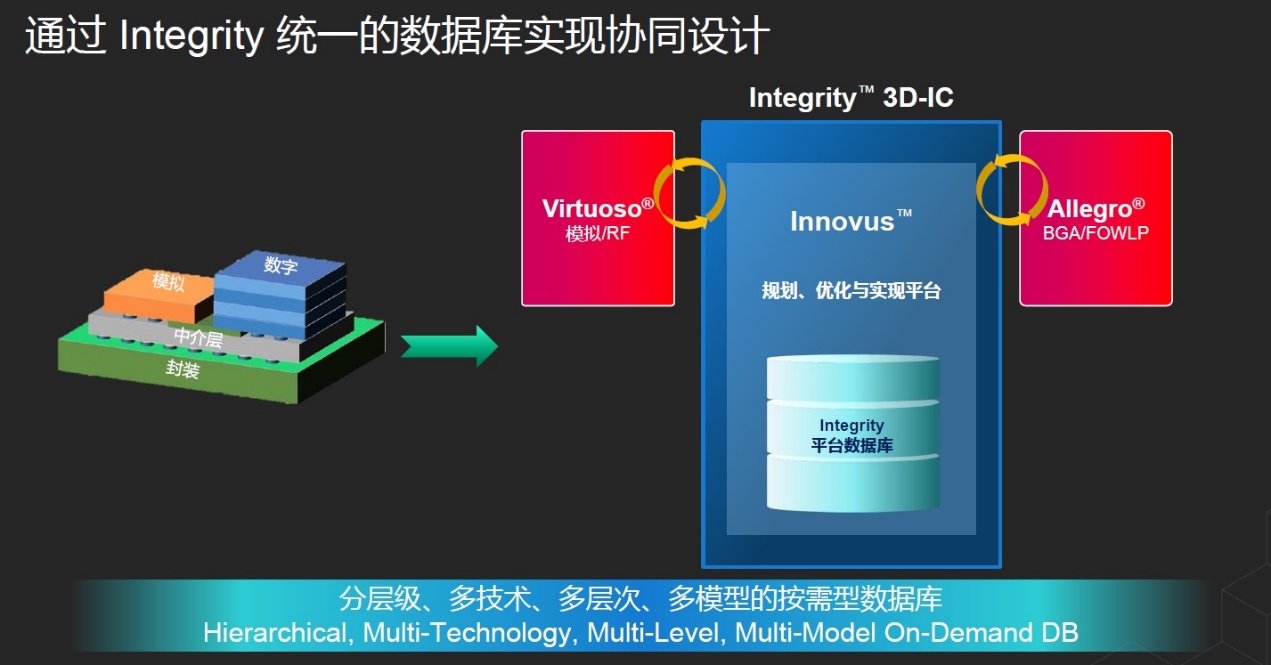

作为Cadence广泛3D-IC解决方案的组成部分,Integrity 3D-IC平台在数字技术之上同时集成了系统、验证及IP功能。例如,支持Palladium Z2和Protium X2平台组成的Dynamic Duo验证平台实现全系统功耗分析;基于小芯片的PHY IP互联;与Virtuoso设计环境和Allegro平台的协同设计;IC签核提取和STA;Clarity 3D Transient Solver与Celsius Thermal Solver热求解器等,从而提供集成化的信号完整性/功耗完整性分析(SI/PI),电磁干扰(EMI)和热分析功能,打通了内部工具互通瓶颈。

Cadence Integrity 3D-IC平台

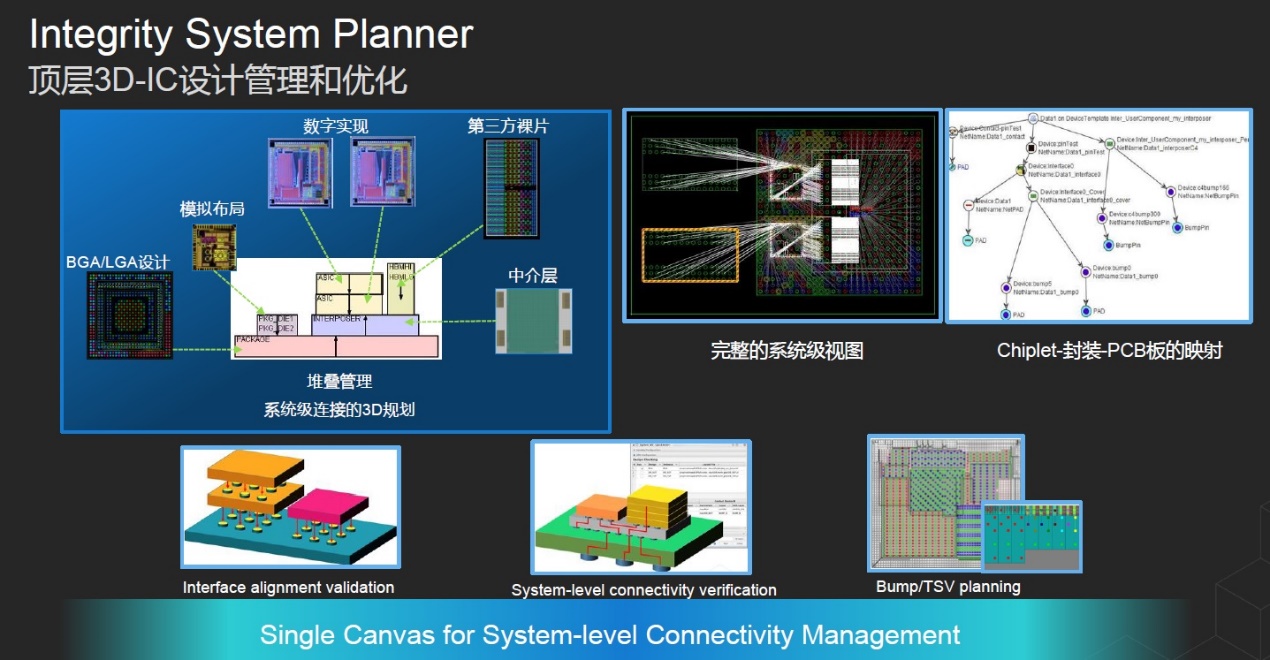

“中国有句老话,叫‘万事开头难’,所以我们花了很大的精力去做Integrity System Planner工具。”刘淼说,作为顶层3D-IC设计管理和优化工具,Integrity System Planner集成了完整的3D-IC堆叠规划系统,支持所有3D设计类型,帮助客户管理并实现原生3D堆叠。这就要求设计者需要具备系统级连接的3D规划全局观,能够对数字实现、第三方裸片、中介层、模拟布局以及BGA/LGA设计进行统筹考虑,将设计从理念变为现实。

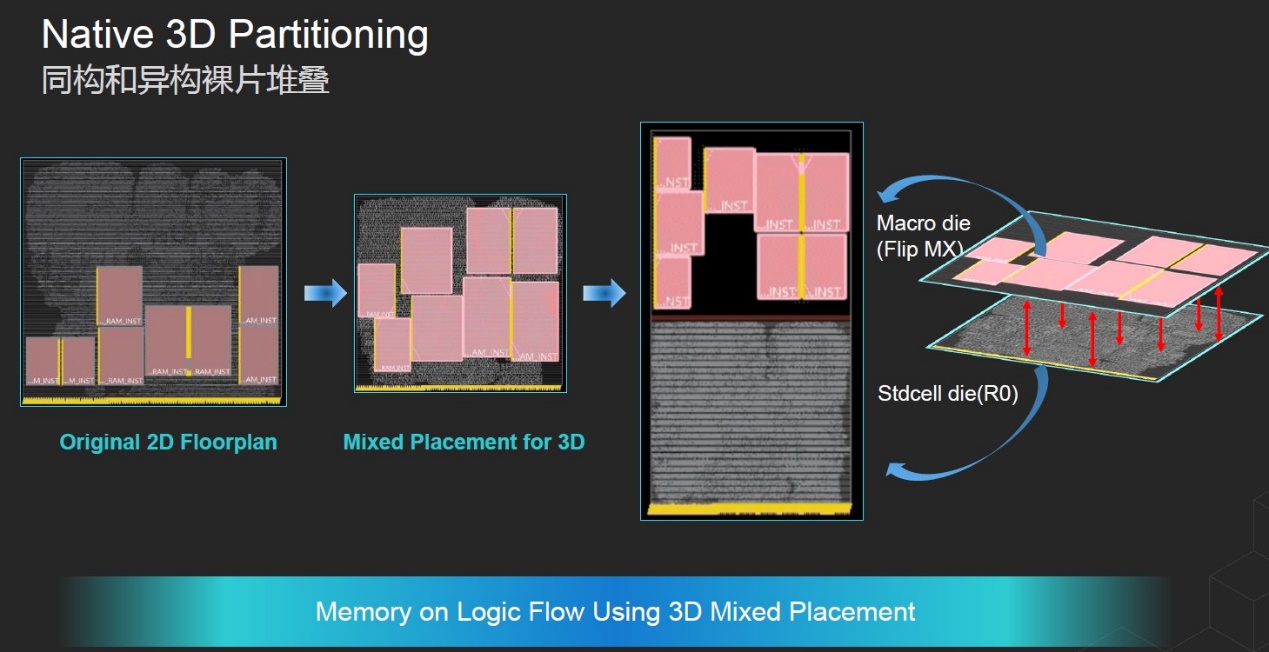

值得一提的是,Cadence中国团队提出了同构和异构裸片堆叠(Native 3D Partitioning)方案,能够有效地提升3D堆叠下的PPA。该技术也体现了Cadence中国团队成立15年来积累的技术实力。

如前文所述,与Virtuoso设计环境和Allegro封装实现了协同设计。这样,通过层次化的数据库设计,工程师可以将设计数据从Cadence模拟及封装环境无缝迁移至系统的不同环节,快速实现设计收敛,提高生产效率。SoC和封装设计团队也可以对完整系统进行完全同步的协同优化,更高效地将系统级反馈集成采纳。

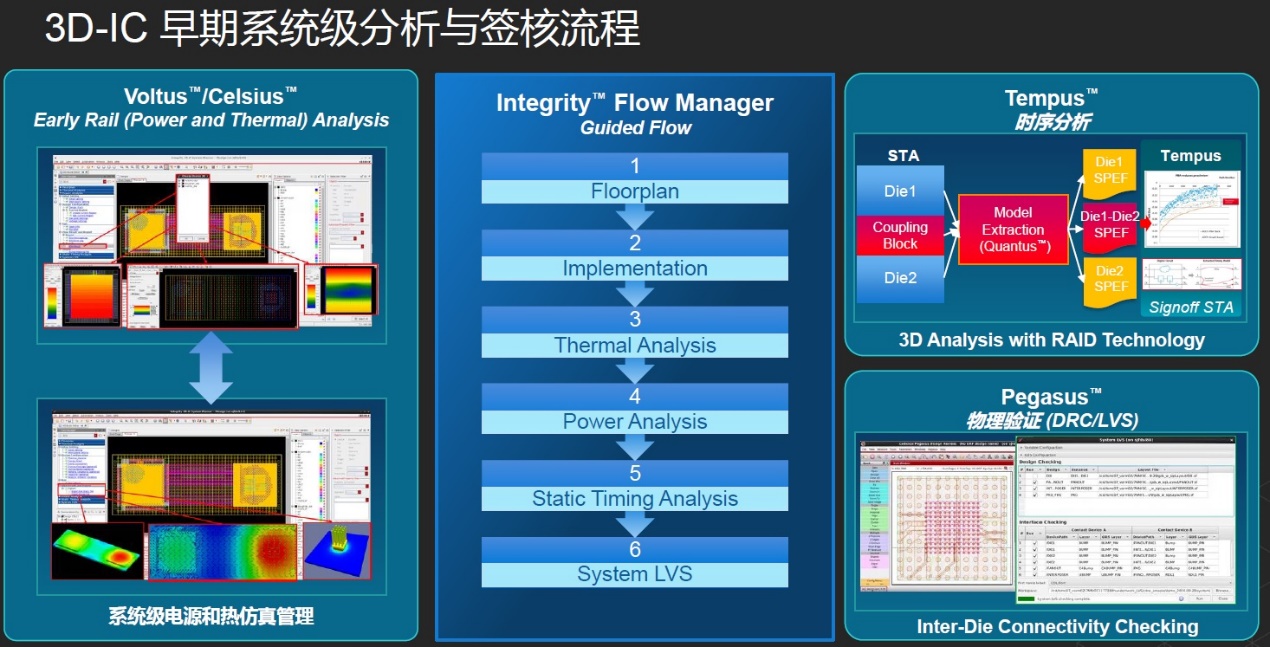

此外,为了在3D-IC设计早期就能实现系统及分析与签核流程,Integrity 3D-IC平台还与Cadence Innovus Implementation System设计实现系统通过脚本直接集成,简单易用,通过3D裸片分区、优化和时序流程实现高容量数字设计;通过早期电热及跨芯片STA,创建稳健的3D-IC设计,利用早期系统级反馈优化全系统PPA。

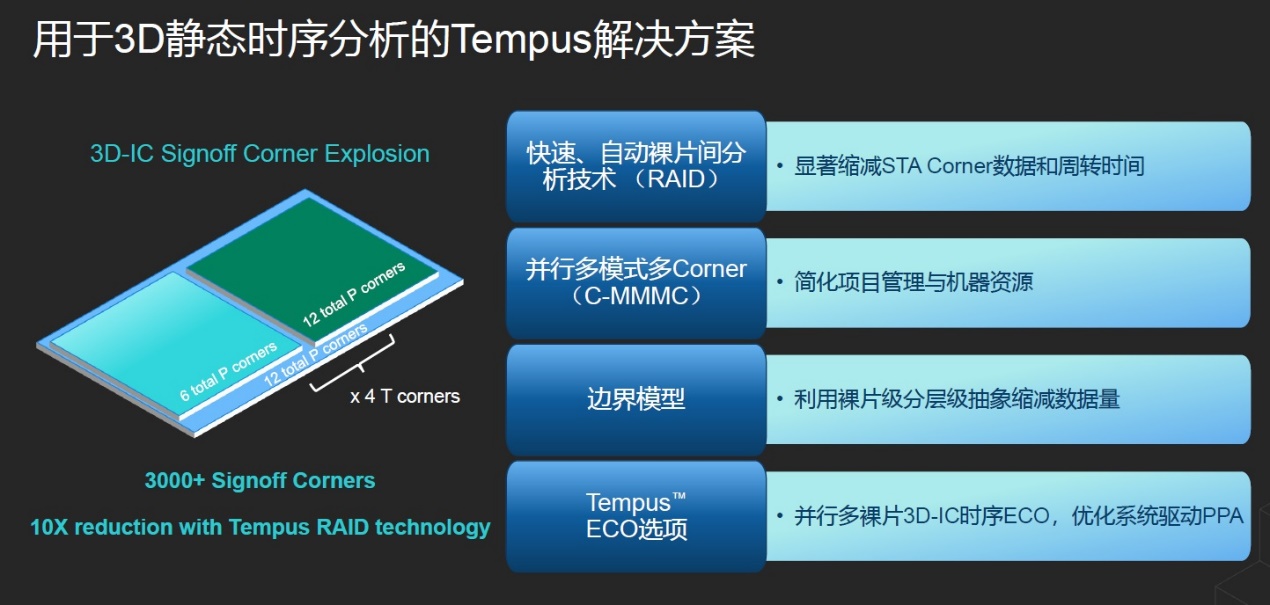

Integrity 3D-IC平台还支持3D静态时序分析Tempus方案。相比2D封装,3D-IC会显著地提升Corners(偏差)数量,加大厂商验证难度和成本,Tempus的快速、自动裸片分析技术(RAID)和并行多模式多Corner技术(C-MMMC)不但可以显著缩减STA Corner数据和周转时间,还能简化项目管理与机器资源。同时,3D exploration流程可以通过用户输入信息将2D设计网表直接生成多个3D堆叠场景,自动选择最优化的3D堆叠配置。

超大规模计算、消费电子、5G通信、移动和汽车应用是Integrity 3D-IC平台主要的应用领域,但考虑到不同应用有着自身独特的诉求,Integrity 3D-IC平台在使用时也会加以灵活应对。刘淼举例称,在存算一体化应用中,用户可以凭借该工具对3D堆叠进行优化,将存储和计算之间的距离尽可能的“缩短”,从而提升效率;而在通信领域,与以往单纯依靠人工花费数周时间进行HBM和SoC绕线截然不同,在Integrity 3D-IC平台的加持下,只需2分钟即可完成全部工作。

Lightelligence和中兴微电子是Integrity 3D-IC平台早期合作的两家中国公司,前者一直在采用多芯片堆叠技术,意图用光学计算技术推动AI的演进加速;后者则通过Integrity 3D-IC平台将优化的中阶层设计实现和系统分析完美集成,提供快速、完整的系统分析,使其能够提供满足超大规模计算和5G通信应用的内存带宽需求的设计。

“在3D-IC领域,中国还是很领先的。”,刘淼表示,未来,随着Integrity 3D-IC平台的发布,会对国内多芯片3D堆叠技术起到极大的促进作用,设计人员将摆脱传统单一脱节的Die-by-Die设计实现方法的束缚,获得更高的生产效率。

- 这是一个单独的平台吗?为什么在Cadence无法下载?