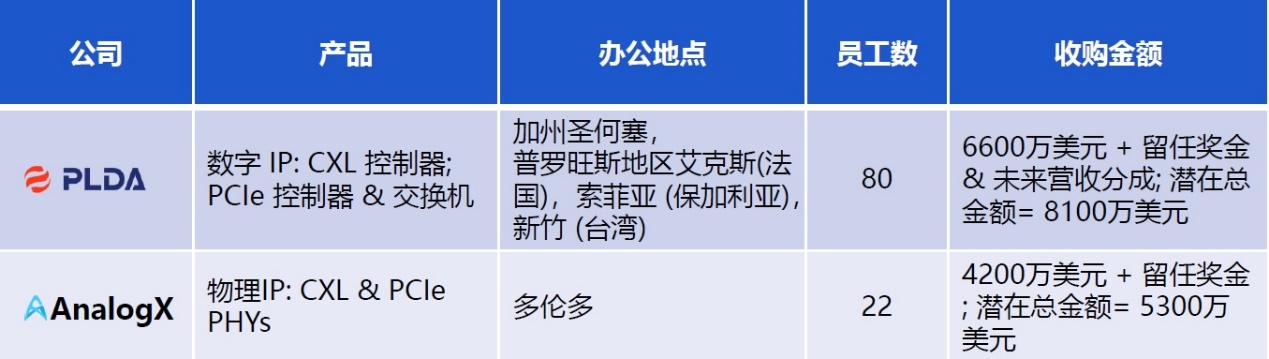

作为行业领先的Silicon IP和芯片提供商,Rambus日前围绕Compute Express Link (CXL)技术和生态展开了“迄今为止最为激进的”战略布局,从一天内宣布完成对AnalogX和PLDA两家公司的收购,到推出面向数据中心的“CXL内存互联(CXL Memory Interconnect)计划”,每一件,都令人印象深刻。

数据中心向革命性新架构演进

缓存一致性是当前数据中心领域亟待解决的核心问题之一,Rambus研究员与杰出发明家Steven Woo在接受《电子工程专辑》独家专访时也谈到了这个问题。他指出,数据和数据中心的重要性不言而喻,它们都是非常重要的核心资产,正在彻底地改变计算系统、平台及架构。

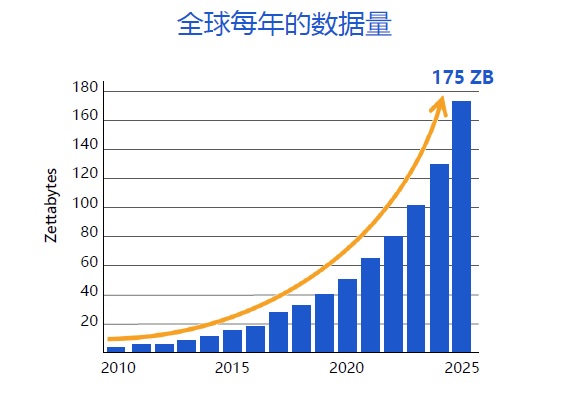

“数据正在以指数级的规模持续增长,预计到2025年,全球每年的数据量将达到175ZB的规模。“但Steven Woo也同时提醒业界需要引起注意的是,当前的数据中心架构,正在从以服务器为计算单元向分解型架构转变。也就是说,要改变资源的池化方式,将其转化为分离式的解决方案。这样,通过完全分解,计算资源可以按需组合,满足不同工作负载的需求。

图片来源:IDC《数据时代2025》

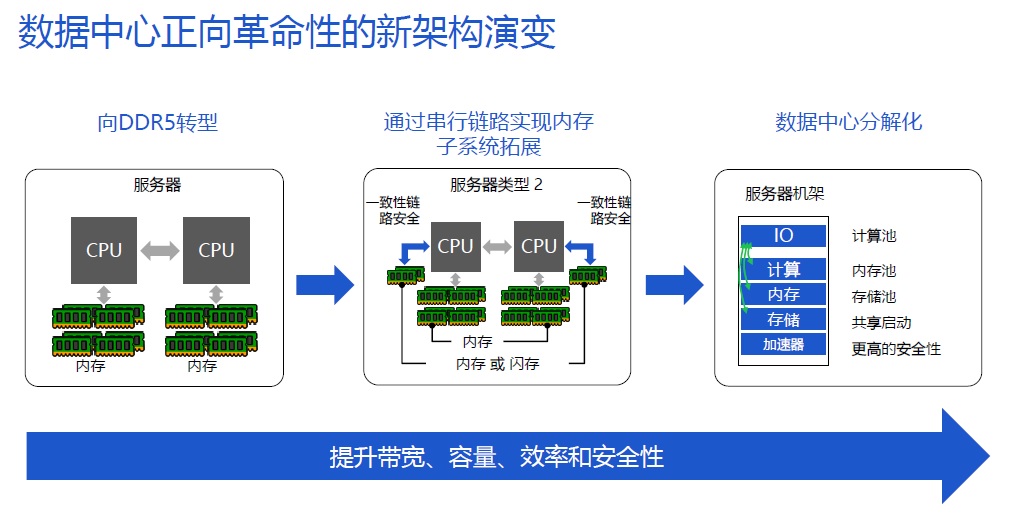

实现上述目标的方式,就是构建更加高效的数据传输与处理的体系架构,下图从左至右为我们依次展示了数据中心正在以及将要经历的三次重要转型。

首先,大约在2021年底,服务器内存将会开始向DDR5转型。与前代产品DDR4相比,DDR5整体架构较为一致,但在容量、能效等方面实现了大幅提升,具备现代化数据中心所必需的特性。

其次,预计到2022年,数据中心将会通过串形链路实现内存子系统的扩展,也就是前文所述的CXL。通过CXL,就可以在传统插拔式内存条的基础之上,为服务器及数据中心增加全新的内存扩展方式。相比传统插拔内存条的方式,CXL可以进一步提高现有数据中心内存的容量和带宽,也被称作“容量与带宽的双扩展”。

最后,数据中心分解化。CXL的使用将让业界更多关注资源池化和资源本身的功能效应,更高效率地分配资源。通过分解化的全新数据中心架构,计算、内存、存储等资源将进一步池化,从而能够按照工作负载的具体需求,将资源定向分配。使用完成之后,这些资源又将回归到统一的资源池中,等待后续的工作负载进行重新分配。

资源的池化一个重大优势,可以将资源的利用率大幅度提高,这会给超大规模计算提供商,特别是云服务提供商,带来巨大的优势,帮助他们大幅度降低总体拥有成本(TCO)。

因此,2019年3月,英特尔宣布联合微软、阿里、思科、戴尔EMC、Facebook、谷歌、惠普企业HPE和华为等公司,共同推出了一个全新的互联标准,取名为Compute Express Link(CXL),应用目标锁定互联网数据中心、通信基础设施、云计算与云服务等领域。

如前文所述,作为一种开放的行业标准,CXL可在数据中心内的专用计算、内存、I/O和存储元素之间提供高带宽、低延迟的连接,以允许为给定的工作负载提供每个元素的最佳组合。

部分CXL联盟会员

打造高速连接IP矩阵

Rambus IP核部门总经理Matt Jones详细介绍了“CXL内存互联计划”的相关细节。

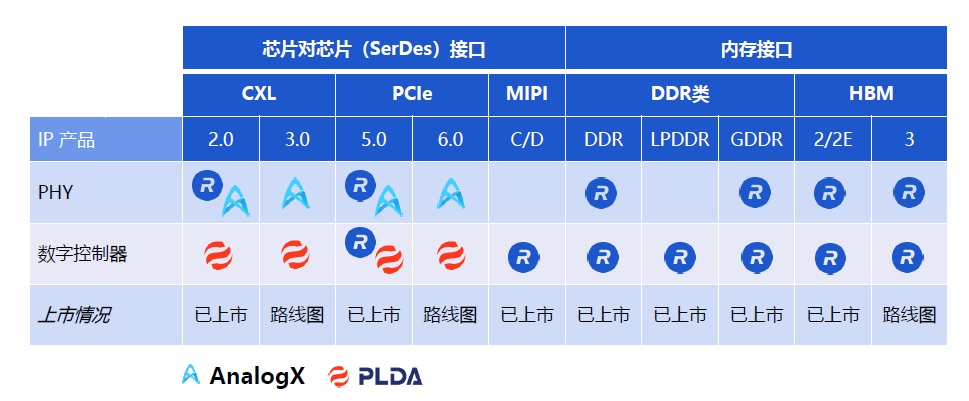

AnalogX是行业领先的高速、低功耗PHY解决方案提供商,此次收购增强了Rambus 系列PCIe 5.0和32G多协议PHY的SerDes技术,为其迈向PCIe 6.0和CXL 3.0奠定了基础;PLDA同样致力于通过CXL和PCIe技术,为数据中心的处理器、加速器、内存和网络设备之间提供高速互联。基于这两项收购,从物理接口到数字控制器,再到IP产品,Rambus CXL相关产品和技术路线图变得日趋完整。

AnalogX与PLDA主要IP产品

“Steven之前提到,Rambus希望能够进一步地推动数据中心转型到可分解、重组的架构。而在人工智能应用场景之下,高速GDDR以及HBM的需求是非常庞大的,所以我们在DDR、HBM内存上也正在推出相关的产品和相关解决方案。”Matt Jones表示,在SerDes接口方面,随着对AnalogX和PLDA这两家公司收购的完成,下一步,Rambus将继续迭代PCIe产品与CXL不同标准的协议。其次,在走向下一代协议支持的过程当中,公司还将继续开发更多SerDes互联产品,以实现基于CXL的互联。

在上述基础上形成的“CXL内存互联计划”,则意在通过内存扩展和池化解决方案推动数据中心的架构转变,支持分解和可组合的服务器架构。

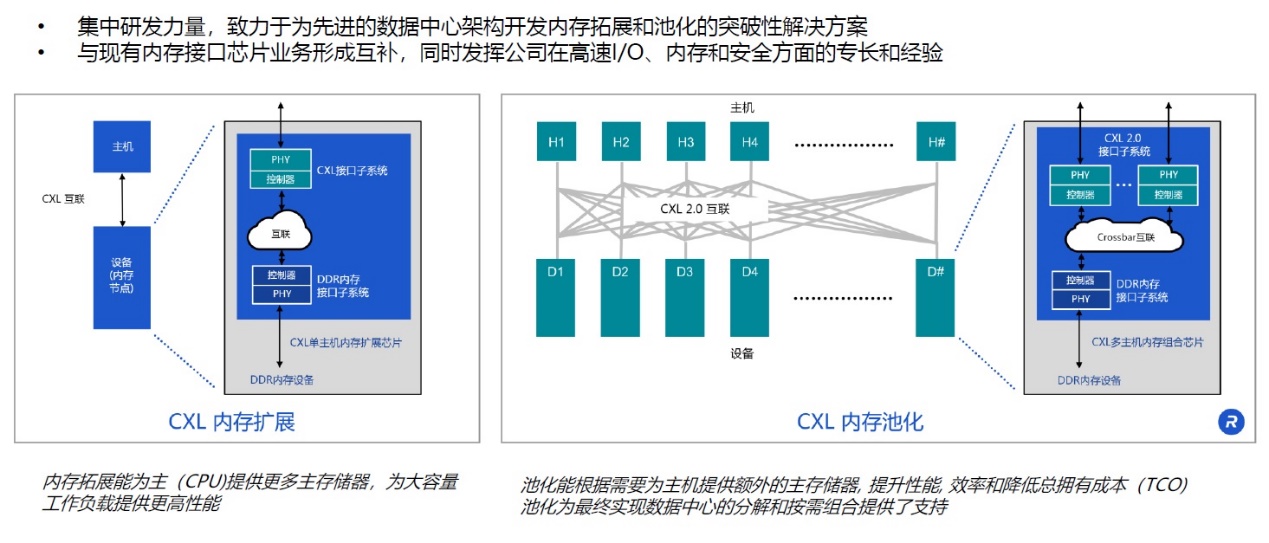

目前CXL有两种模式:一种是CXL内存的扩展,另一种是CXL内存资源的池化,这两种方式都可以推动数据中心内存扩展的转型。下图左侧是CXL内存扩展方式,传统的内存扩展是通过插拔内存条实现,但是现在,主处理器可以通过CXL链路,在高速和低延迟的模式下实现与内存节点和其他设备间的连接。

例如,无论是传统的计算节点还是系统,都会通过一个物理接口/控制器和CXL链路实现与其他关键设备和节点的连接。在下游,专业人员可以将内存设备连接至服务器主板上的CXL扩充槽,以实现内存扩展。基于这套技术的推进,以及后续市场的反馈,Rambus也希望在该解决方案体系之下,推出更多的产品。

CXL内存池化是一个全分解、可重组的全新模式。主处理器通过CXL内存的池化与具体内存来进行连接,并根据不同的工作负载进行资源的重新分配和调配。资源池化可以同时支持多个主机与最优的多个内存资源相匹配。这样,在整个物理接口、控制器、IP集成到设备的情况下,用户就可以更好地匹配具体的计算资源。在一个工作负载完成之后,还可以释放资源并应用到下一个工作任务中。

以下为采访实录:

EETimes China: CXL内存互联计划是一个前瞻性的计划,目前为止,有没有一些可以具体公布的内容?通过实施这样的计划,能够给下一代数据中心或者特定应用带来什么好处?

Steven Woo:总体而言,Rambus此番打造的“CXL内存互联计划”非常关注与半导体企业合作进行研发的项目。我们希望打造更多的使用模式,包括CXL内存扩展,以及内存的资源池化。

内存扩展带来的优势主要是容量增加、带宽拓宽。其次,可以为更多的APP以及不同的场景提供全面支持。CXL内存资源池化最大的优势是可以帮助使用者降低TCO,同时在性能上大幅获益,帮助数据中心获得全面提升。

EETimes China: CXL标准是2019年3月份推出的,运行在PCIe5接口上,是一个开放性的互联标准。但跟它同时/同期出现的还有其他的互联标准,比如CCIX、Nvidia的NVLink、Gen-Z等标准。这些不同的标准之间,主要区别在什么地方?各自有什么样的优势?

Steven Woo:像CCIX、Gen-Z或者NVLink这些标准在市场上已经存在多年了,目的基本上都是一致的,就是希望能够更好地实现处理器及内存之间的快速互联。而CXL的出现,标志着整个研究进入了全新阶段。当然,CXL也借鉴了过去多年其他标准应用中的一些反馈、经验,做出了更好的修正、更新和调整。

站在过去这些巨人的肩膀上,才有了CXL的出现。目前为止,CXL有着非常巨大的行业需求,也获得了行业各个生态系统的支持。CXL的推出牵动着业界的发展,我们希望继续推动CXL的发展,让整个行业生态系统从中获益。

EETimes China: 为什么Rambus选择CXL作为投资的一个方向?

Steven Woo:首先,从公司发展层面来讲,我们认为CXL是一个巨大的机会点,可以通过对CXL的投资和发展,进一步助力并且协同整个行业的整体成长。

其次,CXL和Rambus过去发展历史上的一些技术路线和技术储备是非常符合的,两者之间是有很好的互补。

再次,很多业界的其他合作伙伴,都主动要求Rambus加入CXL的合作和推广。他们一方面看重在CXL方面的专业积累和素养,同时也看重CXL领域的开发潜力。我们希望继续推进CXL项目,在具体的内存和互联上做出自己的贡献。

Matt Jones:我想从生态系统角度做一些补充。Rambus在内存架构领域一直是业界的领导者,有着非常先进的技术,在芯片和IP领域也有着非常强的技术储备。那些系统、云服务提供商以及超大规模计算的提供商,都希望Rambus能够向他们提供完整的全套解决方案。

在ASIC和加速器方面,他们也希望Rambus可以提供完整的IP套件支持。同时,在物理接口、内存控制器方面,我们也希望能够提供更加高带宽的解决方案,满足AI/ML领域未来的发展需求。而随着最新对两家公司的收购,我们在CXL内存互联上也获得了进一步技术增强。

简单来讲,不管是基于IP还是芯片,或者整个生态系统的合作,这都是Rambus选择CXL的原因。

EETimes China: CXL和PCIe 5现在形成了一种事实上的绑定关系。目前HPC、数据中心、超算对PCIe 5的接口需求比较旺盛。其实早在2019年11月,Rambus就发布了PCIe 5和CXL接口的方案。既然是一种绑定的关系,PCIe 5的价值体现在哪里?现在比较主流的是PCIe 4,这种取代的速度会不会因为CXL等的发展而加快?

Matt Jones:您的理解是完全正确的,CXL的确和PCIe 5有非常强的绑定。首先,PCIe是业界非常理解、熟知的一项技术,获得了非常广泛的业界支持,是CXL非常良好的伙伴和组成。

这种结合不仅可以帮助CXL在发展过程中清除更多的风险,也可以确保性能的优异性。在具体的用户场景、用户案例中,我认为CXL的确可以加速PCIe 5被采用的速度,并起到更好的协同作用。

Steven Woo:简单补充一点,PCIe的确是跟CXL有着非常好的协同和合作之处。不管是PCIe 5,还是现在的CXL 2.0版本,两者之间采用统一的电气接口,同时两者之间的数据传输速率也非常一致,这也是两者有机会进一步绑定的重要原因。

但从数据中心应用的角度来讲,这两者的目的也有一定的不同之处。PCIe是一个非常普及的技术和标准,它更加适用于芯片到芯片之间的互联。CXL增加了一些额外的属性,延迟比较低,同时可以保证缓存的一致性,更适用于在分布式计算架构体系之下,来进行内存资源的分配。

EETimes China: CXL标准的定义是一个统一的、开放性的互联标准。从它的定义上来看,会让我们自然而然联想到英特尔OneAPI,赛灵思Vitis统一软件平台,因为它们强调的也是统一的接口、统一的编程模式,属性上与CXL看起来比较。所以,CXL的出现有没有可能对软件提出新的要求?

Steven Woo:这个观察也是非常准确的。CXL能够让软件的开发工作变得更加简单化。其中一个非常重要的原因,就是CXL的缓存一致性。CXL可以帮助软件开发师们处理很多类似的工作,让软件开发师无需去担忧这些事情。从性能上来说,CXL可以非常好地为OneAPI或者Vitis平台赋能,帮助他们实现平台工具的进一步扩展。我们甚至可以这样认为,CXL可以在供应商、平台商之间实现双赢,在软件开发者之间达成多赢。

EETimes China:最后一个问题是关于Chiplet。Chiplet属于小芯片,它们之间的互联也要依靠高速互联。CXL适合Chiplet Design吗?如果是的话,是不是意味着每一颗小芯片上都会有这样的PCIe或者是CXL的控制器,会不会比较耗电?

Steven Woo:我们分两个方面来回答。有一些系统可能本身的接脚数量就比较少,有可能会用到CXL所提供的闪存一致性功能。在这种情况下,CXL是可以发挥作用的,因为也可以弥补这些系统商本身的一些缺陷。但其他的一些系统可能本身已经比较完备了,并不需要用到CXL的功能和属性,就可能会选择其他的一些标准。