挑战:一切都源于软件

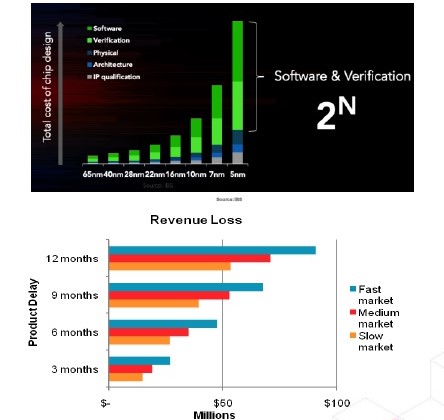

Cadence公司亚太区系统解决方案资深总监张永专对《电子工程专辑》表示,2021-2025这五年间,系统和芯片设计厂商不但面临着上市时间(Time-to-market)的压力,还要承受异构多核、高算力、差异化创新、系统与软件堆栈所带来的技术挑战,由此带来的软硬件协同设计和超过80%的IP复用问题,直接导致验证工作日趋复杂,开发人员不得不将60%以上的精力用于软件。

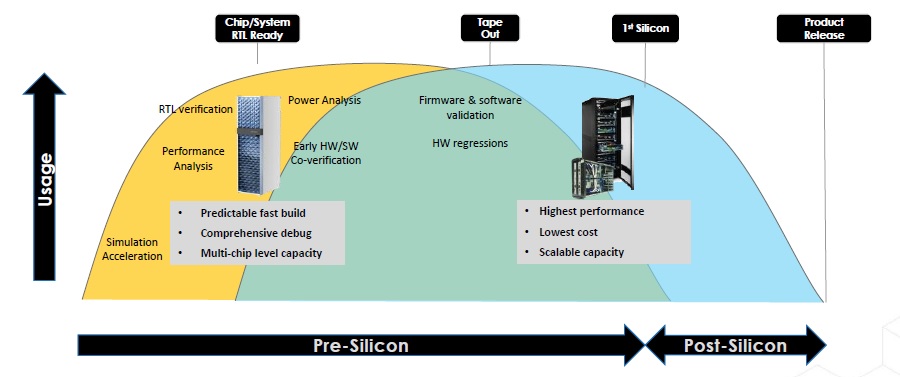

“软件事实上已经成为能不能成功做出一颗好IC的关键所在。甚至可以这样认为,所有芯片设计的最终挑战都来自于软件。”张永专说,软件正在主导芯片开发的成本、流程和周期,Cadence以及其他EDA厂商都希望在芯片正式流片之前,越早通过完整的系统级验证与仿真对芯片性能、功耗、软硬件协同进行测试越好,这也符合当前主流设计流程中所体现的“Shift Left”趋势。

强大的硬件仿真加速(Emulation)和原型验证(Prototyping)工具参与其中,是确保上述设计流程得以实施的关键,这也是Cadence选择在2021年4月推出全新的Palladium Z2企业级硬件仿真加速系统和Protium X2企业级原型验证系统的原因。由于双系统无缝集成统一的编译器和外设接口,因此“Palladium Z2+ Protium X2”的组合也被Cadence称之为“系统动力双剑(dynamic duo)”。

但张永专指出,这两种方法的关注点并不相同:在前期RTL代码验证阶段,倾向于采用硬件仿真加速模式;当设计成熟度达到80%以上,软件团队开始介入时,就会将设计迁移到原型验证平台,直至最终的Tape out。因此,在正确的时间,在正确的使用场景和工作中,使用正确的工具,对设计人员而言尤其重要。

双剑如何合璧?

其实,面对日益复杂的芯片验证和软硬件系统协同开发的迫切需求,Cadence发力硬件仿真和原型加速的努力可以追溯到2006年,甚至更早。

例如在2006年,Cadence就推出了Cadence Incisive Palladium III加速器/仿真器,当时能够支持最多32位用户同时运作,单工作站每小时编译能力可达3000万门,并且其容量的调整范围可以从每个域/用户180万门到整个系统的2.56亿门。

2013年,Palladium XP II验证计算平台作为Palladium XP仿真系统的更新产品面世,最多可以将验证性能再提高50%,更将其业界领先的容量扩展至23亿门。

两年后的2015年,Cadence又推出业内第一个数据中心级硬件仿真加速器Palladium Z1,凭借企业级的可靠性和可扩展性,最多能同时处理2304个并行作业,容量可扩展到92亿门。

而最新一代“系统动力双剑(dynamic duo)”则基于下一代硬件仿真核心处理器和Xilinx UltraScale+ VU19P FPGA,将为客户带来2倍容量提升和1.5倍性能提升,能够以更少的时间为大规模芯片验证完成更多次数的迭代。此外,模块化编译(Module Compiler)技术也突破性地应用在两个系统中,使得100亿门的SoC编译可以在Palladium Z2系统10小时内即可完成,Protium X2系统也仅需不到24小时就可以完成。

“与业内其它友商基于FPGA架构的产品不同,Palladium的硬件仿真核心处理器由Cadence定制开发,架构非常特别,无需进行传统的布局布线(Place&Route),从而确保实现快速迭代。”张永专解释说,如果用FPGA进行迭代,做硬件仿真,显然是“用错了地方”——因为任何一家EDA公司的仿真产品,都无法同时兼顾仿真方针的精确度和迭代速度,必须要在两者之间选择寻找到“精妙的平衡”。对硬件仿真而言,在RTL Code完全稳定之前,在纠错工作没有完全做完之前,FPGA其实很难实现快速迭代,没有效益,无法节省开发时间。与之相比,自定制的硬件仿真处理器可以提供业界最快的编译和Debug速度,结果所见即所得,以及最全面的硅前硬件纠错功能。

但Cadence却为Protium X2选择了FPGA处理器,原因在于这是为了进行硅前软件验证,属于软件调试范畴而非硬件纠错,通过使用通用型FPGA处理器,能够享受到先进制程和强大性能所带来的最高运行速度、最短初始启动时间、以及成本的降低。

模块化编译技术是另一个值得关注的创新点。简单来说,该技术就是在编译的早期对模型进行分割,并将其置于多个Bucket中进行独立的同步并行编译,客户无需进行额外干预,从而以多线程的形式将整体时间进行压缩。“Cadence是业内第一家帮助客户完成模块化编译的公司,目前为止,业内还没有其他类似的解决方案。”张永专表示。

与此同时,为了让整个产业最大程度的获得硬件加速带来的益处,Palladium Z2和Protium X2还在四个层面进行了优化:首先,支持包括RTL、Verilog、VHDL在内的所有硬件设计;其次,可以同虚拟模型放在一起同时仿真;第三,硬件加速器支持DDR4/DDR5/HBM/UFS等丰富的存储器类型;最后,为PCIE、USB、Ethernet等所有的接口协议提供相应的实际物理接口。

不过,张永专并不认为硬件仿真在未来会完全取代软件仿真。“软件仿真运行在服务器上,整体成本比硬件加速还是要低不少,非常适合形式验证、IP级仿真等应用。“但他指出,对于规模更加庞大的SoC芯片验证、软件调试、原型验证等工作,还是需要Palladium Z2和Protium X2这样量级的产品。

作为支持公司智能系统设计(Intelligent System DesignTM)战略的一部分,除了Palladium Z2硬件仿真加速系统与Protium X2原型验证系统外,Cadence验证全流程还包括Xcelium Logic Simulation大规模并行逻辑仿真器、JasperGold Formal Verification Platform形式化验证平台、以及Cadence vManager智能验证管理应用套件,可以提供最经济高效的验证吞吐率,助力实现SoC卓越设计。

考虑到中小型IC设计公司,尤其是创业公司,在资金投入方面比较谨慎,没有能力承担高成本的EDA工具,对开发工具的更新换代也并不频繁的现状,Cadence一方面选择通过云或者租赁的形式提供服务,另一方面,在机架硬件结构上也采取了灵活的配置方式。

“中小用户完全可以从自身实际出发,购买机架1/3或是1/2的功能,就能实现至少2亿门以上的验证规模。甚至,但如果只是做小型的AIOT方面的设计,普通的软件仿真就可以解决,并不需要Palladium Z2/Protium X2这样的工具。”张永专说。