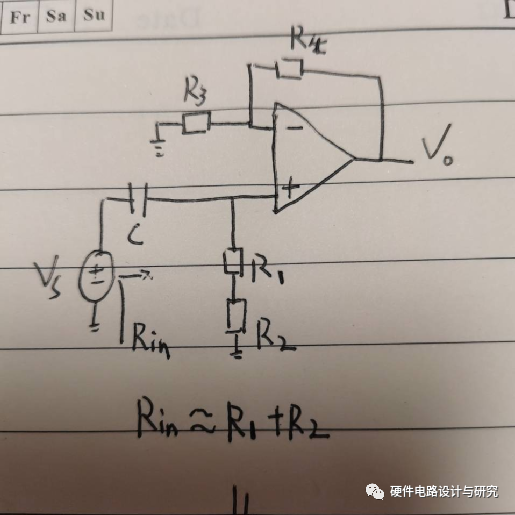

在电路设计过程中,常常需要隔直做交流AC放大,同时又需要高输入阻抗的情况,此时可以利用自举电容构成的自举电路来改善电路的性能,增大电路的输入阻抗,在此探讨一个自举电路的例子来详细说明它是如何增大电路的输入阻抗的,下图是个同相交流AC放大器,其中的R1/R2为同相输入端提供直流偏置通路,是不能省略的,否则运放的+输入端的偏置电流会不断对电容C充电,改变偏置电位,最后导致运放+输入端电位接近正电源或负电源,而无法正常工作,而偏置通路R1/R2会严重降低输入阻抗,因为R1/R2不能取得太大,太大的电阻,其热噪声太高(Un^2=4KTBR),降低输出信噪比, 那么能否在满足噪声要求得情况下,使用较小R1/R2电阻而获得较高的输入阻抗?此时可以引入适当的正反馈。

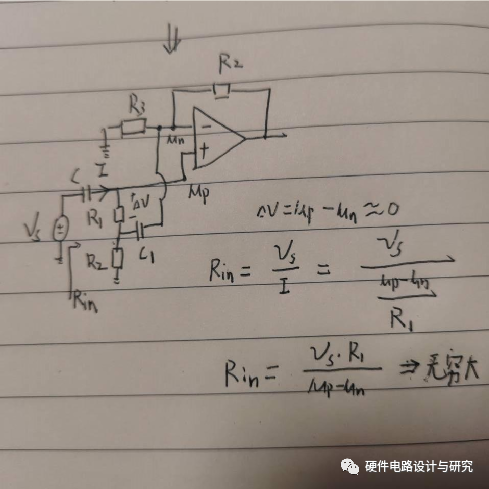

通过下图的C1电容引入适当的正反馈后:

这是低频时候的理论估算,实际上因为运放的内部相位延迟,导致up-un并不接近零,工作频率越高,偏差越大,自举效果越差,不过适当选择运放或工作在低频端时,自举提高输入阻抗的效果还是非常明显的。以下我们用一个实际运放搭建电路,在PSICE下仿真研究一下:

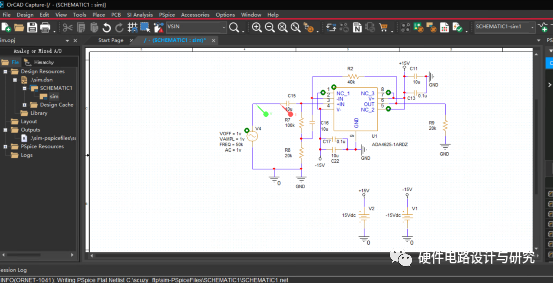

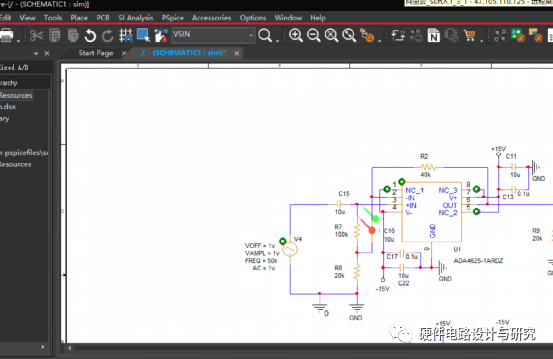

运放用实际的ADA4625-1,加载其pspice模型后,用allegro的pspice进行仿真研究:

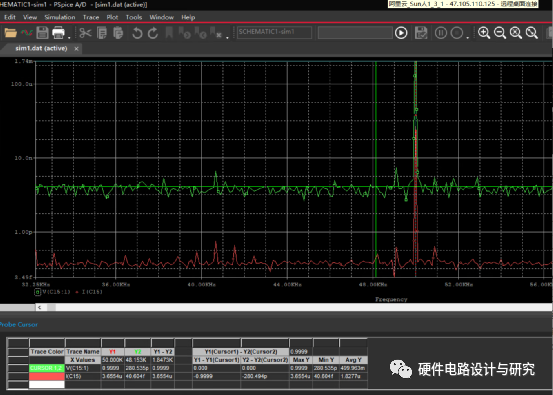

如上图所示,我们测量电容输入端口的瞬态电压、电流波形,并跳过起始过渡段数据,然后利用FFT求出测试数据的电压、电流交流幅度,用其比值作为测量的输入阻抗:

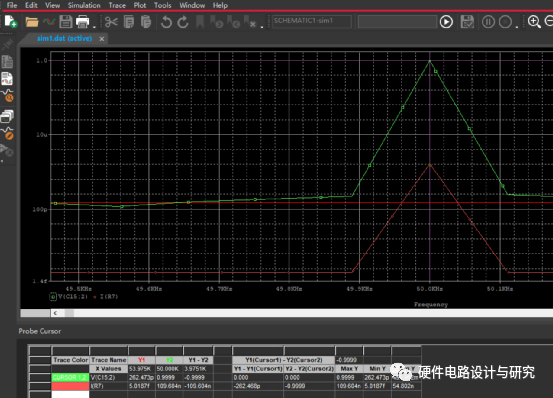

1) 输入频率为50khz,对瞬态分析结果做FFT,得到Us=1v,i=3.65ua,计算Rin=273k欧姆

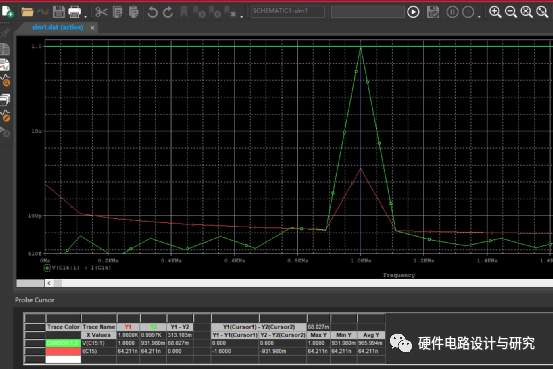

2) 输入频率为1khz,瞬态分析结果做FFT,得到Us=1v,i=64.211na,计算Rin=15.6M欧姆:

3)前述测量的阻抗由两部组成:R7/R8自举支路和运放自身的原本输入阻抗,现在我们改变一下测试点,如下图所示,直接估算一下R7/R8自举支路的阻抗:

同样对瞬态分析的结果,做FFT,得到50khz基波幅度Us=1v,50khz电流幅度i=106nA,可以计算得R7/R8支路的等效阻抗为9.4M欧姆,如下图:

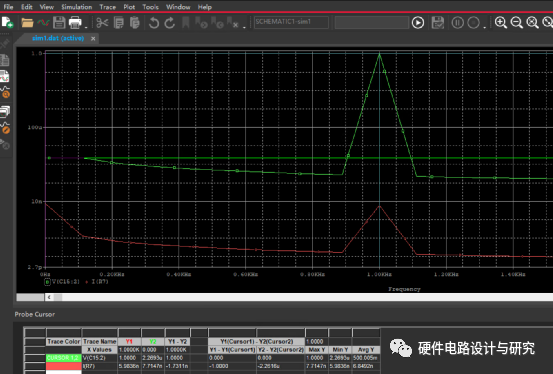

4)1khz时、直接测量估算R7/R8的阻抗为:同样对瞬态分析的结果,做FFT,得到1khz基波幅度Us=1v,1khz电流幅度i=5.98nA,可以计算得R7/R8支路的等效阻抗为167M欧姆,如下图:

如前所示,自举电路提高输入阻抗的效果非常明显,为啥高频时,总体阻抗下降比较快?主要还是运放自身的输入电容影响,我们示例使用的AD4625-1运放的输入参数如下:

图中所示输入电阻高达1000G欧姆,非常高!但是这是直流阻抗,而该运放是JFET运放,直流阻抗自然很高,但是输入电容也不小,图中所示差模8.6pf,共模11.3pf,而我们的自举接法,对本电路而言,运放而言,通过C16大电容等效为运放正负输入端并联,故其输入电容为取共模的11.3pf,对应阻抗为

1)50khz为rin=1/wc=1/(50k*11.3p*6.28)=281.7k欧姆

2)1khz为rin=1/(1k*8.6p*6.28)=14M欧姆

如前所示,R7/R8自举支路的单独测量阻抗为:

1)50khz为9.4M欧姆

2)1khz为167M欧姆

如前所示,总的交流测量阻抗:

1)50khz,Rin=273k欧姆

2)1khz,Rin=15.6Mk欧姆

高频时总的交流测量阻抗基本等于运放输入阻抗与R7/R8自举阻抗的并联,而低频时存在误差,这主要是支路的电抗特性导致两个支路的电流相位误差的原因,不能直接套用电阻串并联关系