来源 | 数字ICer

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

目录

1.UART

2.SPI

3.JTATG

4.I2C

5.CAN

UART:全称 Universal Asynchronous Receiver/Transmitter,中文可译为通用异步收发器。

UART的发明是由于贝尔自己需要将一个电传打印机(Teletype)连接到一个PDP-1,需要将并行信号转换为串行信号。贝尔于是设计了一个使用大约50个独立部件的电路。这个想法被证明是受欢迎的。当时西部数据公司(Western Digital)是一家制造计算机芯片的小公司,它设计了单芯片版的UART。

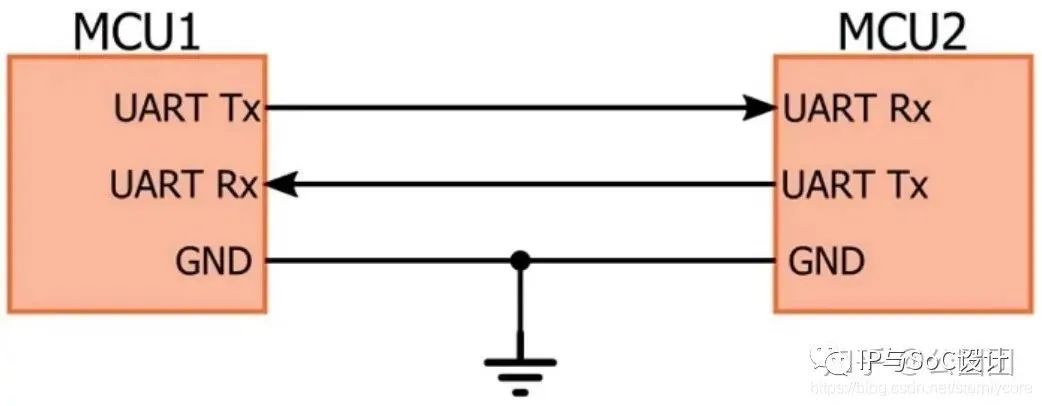

UART当前常用于MCU的低速互联,最少仅需要两根信号连接(TXD和RXD),信号支持TTL电平,RS232电平或者RS422电平。UART为全双工异步通信协议,最高支持115200bps的波特率(常用波特率为9600bps)。

UART定义了一种串行传输协议,单次可传输一个字符,包含5到8bit有效数据(常采用7bit数据,ASCII)。

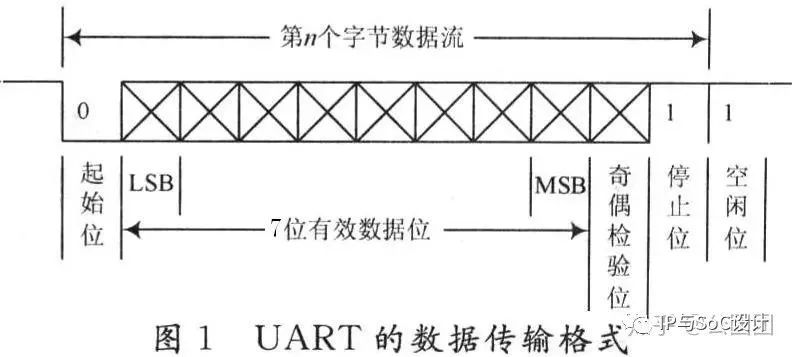

UART的一个字符除了包含有效数据位外,还包含起始位1bit,奇偶校验位1bit和停止位1bit(也支持1.5bit或者2bit配置)。UART一次传输最多8bit有效数据而不是更多的原因是其设计标准收发两端的频率误差在10%以内,当收到的数据为8bit时误差控制在1bit内,保证了数据的采样不会出错。

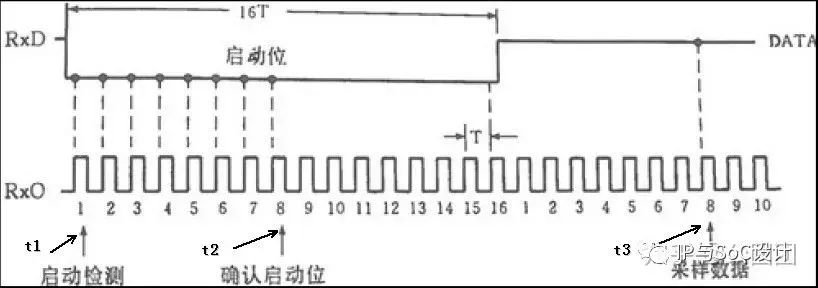

UART接收使用高频时钟进行采样,在最早的8086芯片中为兼顾速度和稳定性,常采用波特率的16倍时钟进行采样。当主时钟频率确定时,IC实现中可以通过设定波特率寄存器N实现任意波特率。

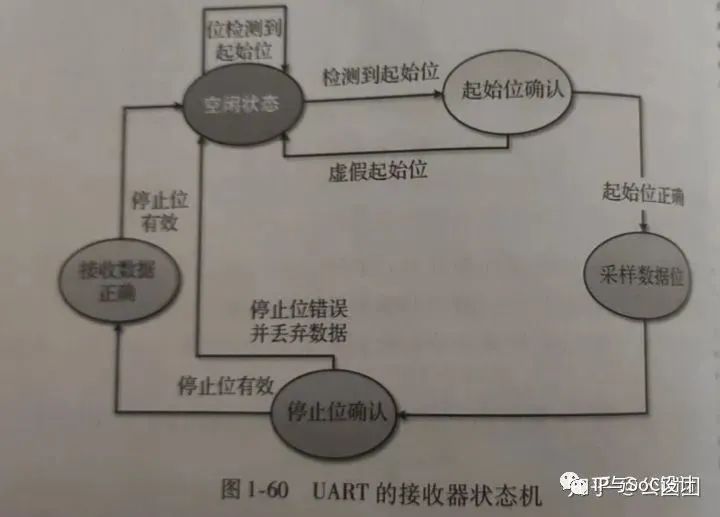

一个典型的UART接收器的状态机设计如图所示,在空闲状态时接收机通过监测接收信号从1变0,确定接收的起始位。为消除通信线路噪声的影响,只有连续接收到N/2个0后才认为这是一个真正的起始位,并开始在最佳采样点(N/2时刻)采样数据位。

UART的流控包括硬件流控和软件流控两种。

硬件流控基于RS232的两个信号接口RTS(数据发送请求)和CTS(数据发送允许),一端设备的RTS与另一端设备的CTS相连。RTS与CTS均为低电平有效,数据接收设备通过置低RTS接口通知发送设备的CTS接口,发送设备可以发送数据。

软件流控通过带内传输XOFF和XON信号,控制发送的起停。数据接收设备通过发送XOFF通知数据发送设备停止发送数据。数据接收设备通过发送XON通知发送设备继续发送数据。

SPI 全称 Serial Peripheral Interface,中文译为串行外围设备接口。

最早是由Motorola(摩托罗拉)公司开发的全双工同步串行总线,常用于微控制器与外设之间的连接比如SD卡,液晶屏等外设。SPI没有统一的协议规范,但由于其广泛的使用,根据实际使用中大家通用的习惯形成了一个类似行规的标准,具体的应用需要实际参考特定器件手册。

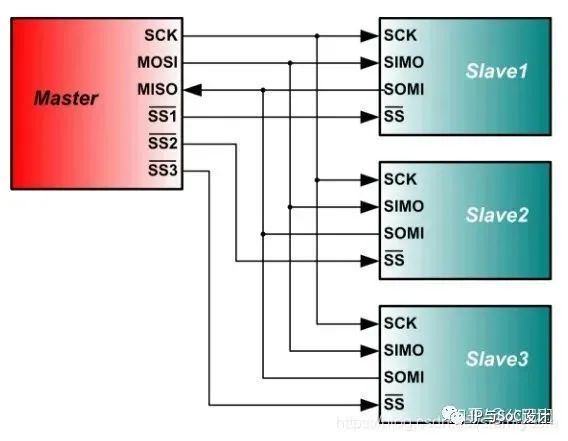

SPI用于在单个主控制器和一个或多个从设备之间交换数据,譬如MCU与EEPROM、FLASH、AD转换器的连接。SPI的两端中提供时钟的为Master,接收时钟的为Slave。SPI最少采用四线连接,SCLK,SS,MOSI,MISO。SPI按帧进行数据交换,支持的字长不限于8bit,可根据应用特点灵活选择消息字长。SPI是源同步时钟协议,支持100MHz以上的高速时钟。

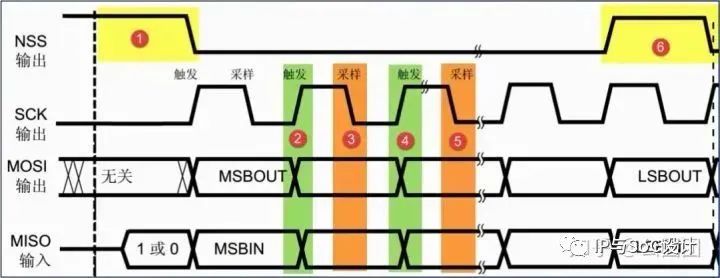

NSS电平由高变低,则产生起始信号;NSS电平由低变高,则产生停止信号。从机检测到自己的NSS线电平被置低,则开始与主机进行通讯;反之,检测到NSS电平被拉高,则停止通讯。

MOSI和MISO线在SCK的每个时钟周期传输一位数据,开发者可以自行设置MSB或LSB先行,不过需要保证两个通讯设备都使用同样的协定。

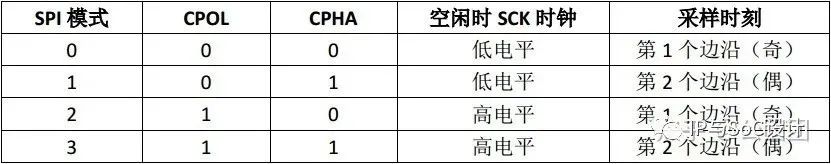

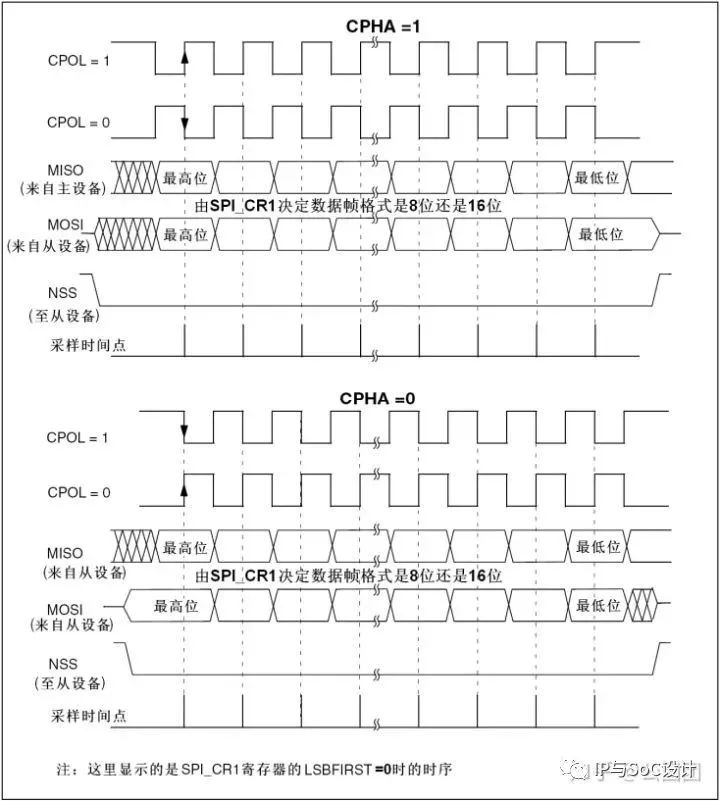

根据SCK空闲状态的电平(CPOL)和数据采样时刻(CPHA)的不同,SPI有四种通讯模式。Master和Slave需要工作在相同的模式下才能正常通讯,Master的MOSI如果在SCK上升沿launch数据,Slave的MOSI需要在SCK的下降沿capture数据,反之亦然。

当CPHA=0时,Master需要在第一个SCK的边沿出现前将数据在MOSI上准备好。

Motorola定义5类寄存器:SPI Control Register 1 (SPICR1)控制寄存器1,极性控制,数据长度控制SPI Control Register 2 (SPICR2)控制寄存器2SPI Baud Rate Register (SPIBR)波特率寄存器SPI Status Register (SPISR)状态寄存器SPI Data Register (SPIDR)数据寄存器

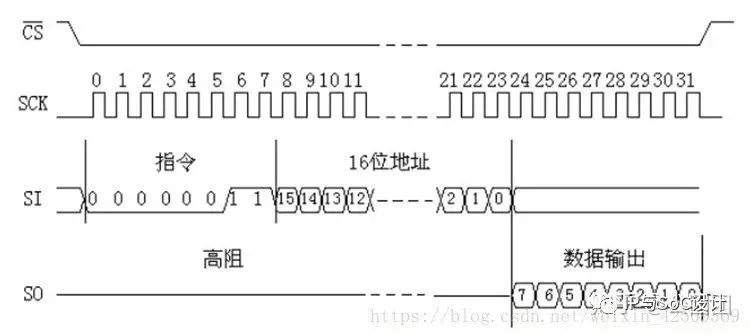

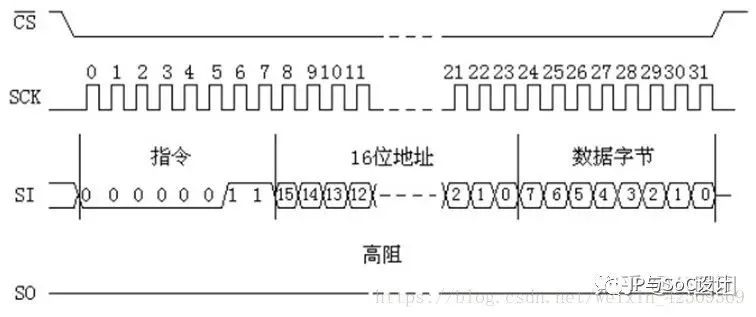

SPI读写每笔传输交换一帧数据,一帧数据的bit数据可以是8bit,16bit或者其他数量的bit。SPI读:片选---读指令---地址---数据读出

SPI写:片选---写指令---地址---数据写入

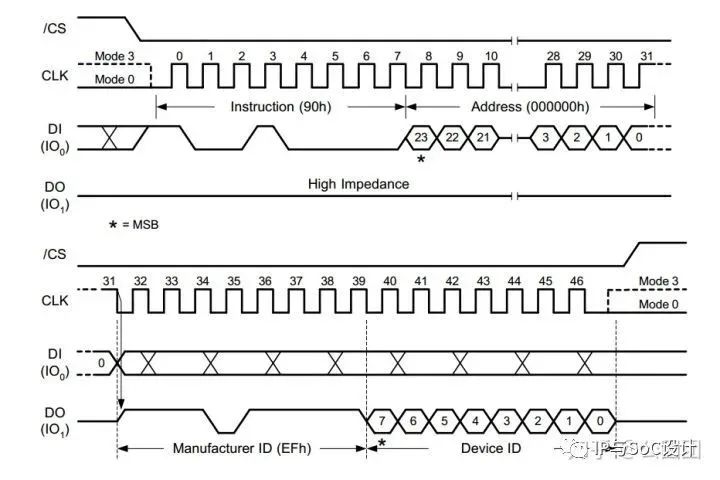

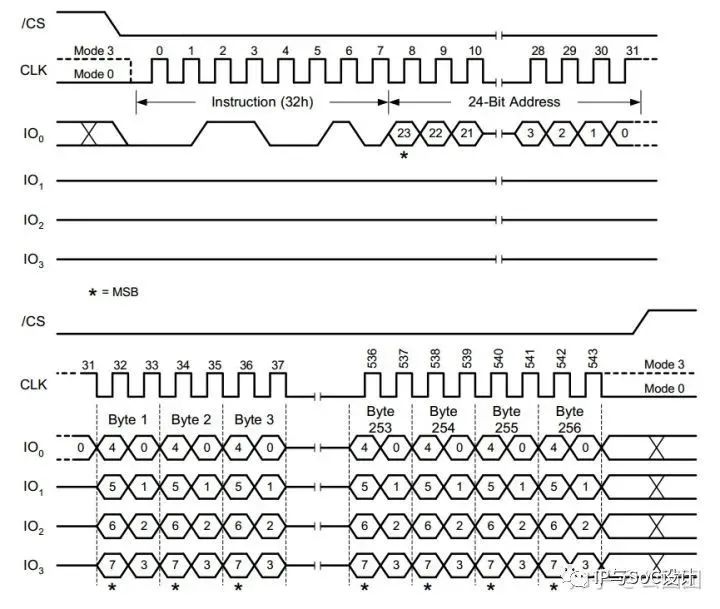

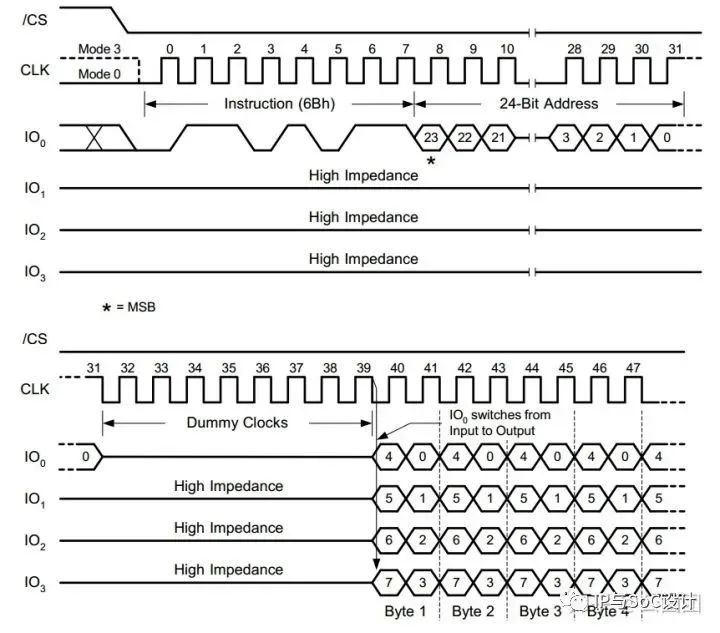

DSPI和QSPI主要用于存储器接口,其帧格式由存储器定义。归纳下来,QSPI的传输分为两种类型,第一种类型是传统的SPI的单线传输,第二种是QSPI的四线传输。

第一种类型传输常用于状态和控制寄存器的读写,譬如读ID。该传输过程采用MOSI和MISO进行数据交换,一帧数据是46bit。此外,单线传输也支持数据的读写。

第二种类型的传输常用于数据的读写,譬如四线写数据。该传输包含了两个阶段,第一个阶段是命令和地址阶段,第二个阶段是数据传输阶段。第一个阶段,采用单线传输,通过MOSI向器件发送命令和地址。第二个阶段,采用四线传输,通过四个IO向器件发送或者读取数据。

此外,读数据时在第一个阶段和第二个阶段中间会插入Dumy Clocks。

JTAG,全称Joint Test Action Group,中文名称联合测试行动组。

1990年JTAG正式由IEEE的1149.1-1990号文档标准化,在1994年,加入了补充文档对边界扫描描述语言(BSDL)进行了说明。从那时开始,这个标准被全球的电子企业广泛采用。边界扫描几乎成为了JTAG的同义词。

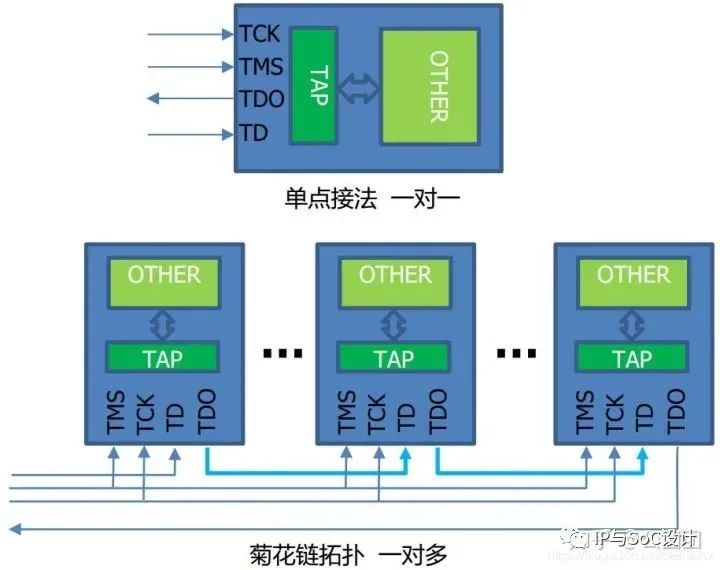

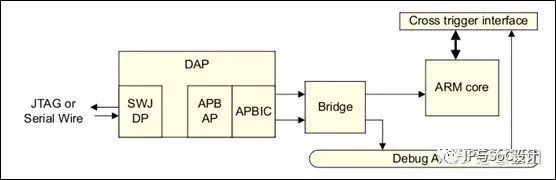

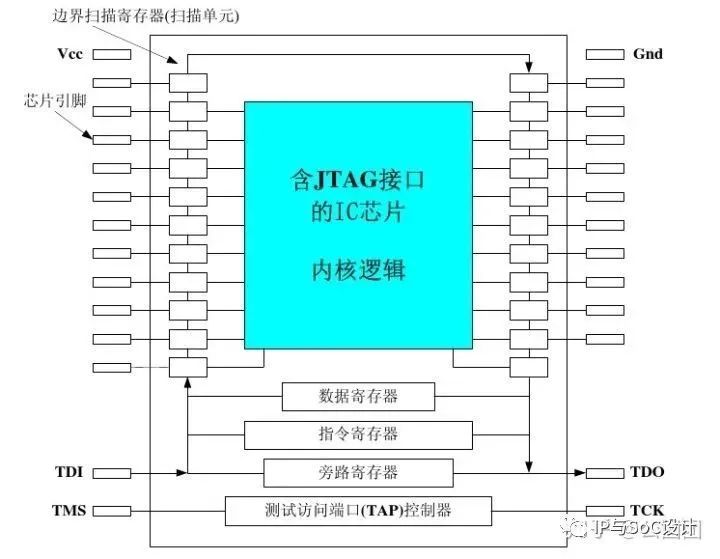

JTAG的基本原理是在器件内部定义一个TAP(Test Access Port,测试访问口)通过专用的JTAG测试工具对内部节点进行测试。当前JTAG协议也用来对芯片进行调试,JTAG通过器件内部的DAP(Debug Access Port,调试访问)访问内部总线。

JTAG最少使用四个信号,包括TCK,TRST,TMS,TDI和TDO,最高支持100MHz的串行数据传输。

JTAG协议核心是三个寄存器和TAP状态机。作为DEBUG的JTAG接口会在DAP中利用旁路寄存器将JTAG协议转换为APB协议。作为DFT的JTAG接口会直接利用数据寄存器进行边界扫描。

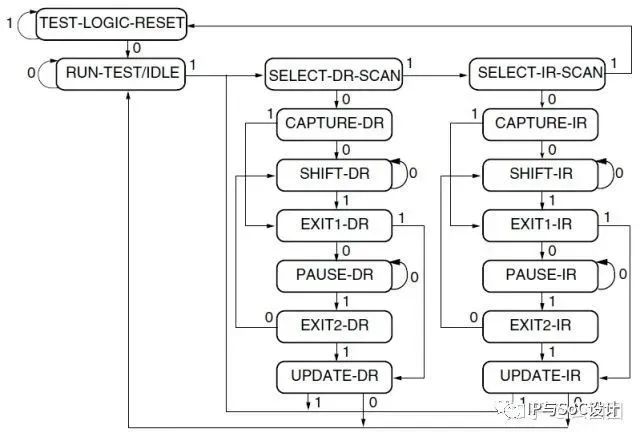

JTAG协议通过TMS信号控制TAP状态机的转换。

系统上电后,TAP Controller首先进入Test-LogicReset状态,然后依次进入Run-Test/Idle、Selcct-DR- Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR状态,最后回到Run- Tcst/Idle状态。

在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的。

其中,在 Capture-IR状态下,一个特定的逻辑序列被加载到指令寄存器中;在Shift-IR状态下,可以将一条特定的指令送到指令寄存器中;在 Update—IR状态下,刚才输入到指令寄存器中的指令将用来更新指令寄存器。

最后,系统又回到Run—Test/Idle状态,指令生效,完成对指令 寄存器的访问。当系统又返回到Run—Test/Idle状态后,根据前面指令寄存器的内容选定所需要的数据寄存器,开始执行对数据寄存器的工作。

其基本 原理与指令寄存器的访问完全相同,依次为seIect—DR—Scan、Capture—DR、Shift—D、Exitl一DR、Update—DR, 最后回到Run-Tcst/Idle状态。通过TDl和TDO,就可以将新的数据加载到数据寄存器中。经过一个周期后,就可以捕获数据寄存器中的数据,完成对与数据寄存器的每个寄存器单元相连的芯片引脚的数据更新,也完成了对数据寄存器的访问。

JTAG接口除了标准的4信号引脚外,TI还支持2信号引脚的SBW_JTAG。SBW_JTAG仅使用SBWTCK和SBWTDIO信号,常用于引脚受限芯片上。

I2C总线全称Integrated Circuit,中文名I方C总线。

I2C 总线是由 Philips 公司开发的一种简单、双向二线制同步串行总线。

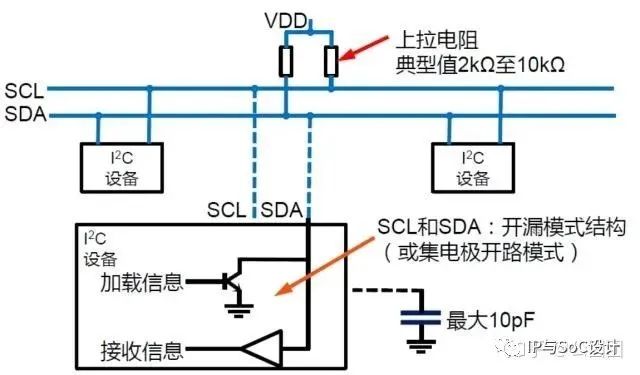

I2C总线大量用于Host与外部设备的连接,简化了系统布线。I2C是双向二线制同步串行总线,每次可传输NByte数据,支持100kbps/400kbps/3.4Mbps/5Mbps速率。I2C总线包含两条信号线,串行数据SDA和串行时钟SCL。I2C的一个总线上可以挂在多个主机和多个设备,每次数据传输都是由主机发起,且由主机提供时钟。

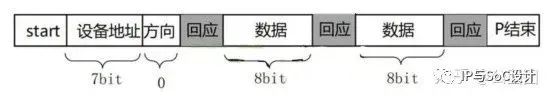

I2C传输是以8bit为单元传输数据的,每个8bit单元数据后必须紧跟1bit回应数据。I2C的每笔传输包含四个阶段:

(1)开始信号(S):SCL为高电平时,SDA高电平向低电平跳变,开始传送数据。

(2)结束信号(P):SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

(3)响应信号(ACK):接收器在接收到8位数据后,在第9个时钟周期,拉低SDA。

(4)数据信号(DAT): 必须为8bit,传输时先传输最高位(MSB),之后必须紧跟着ACK信号。

此外,每笔传输的第一个8bit数据被用来作为,设备地址和访问类型。

写数据

若配置的方向传输位为“写数据”方向,即第一幅图的情况,广播完地址,接收到应答信号后,主机开始正式向从机传输数据(DATA),数据包的大小为8 位,主机每发送完一个字节数据,都要等待从机的应答信号(ACK),重复这个过程,可以向从机传输N 个数据,这个N 没有大小限制。当数据传输结束时,主机向从机发送一个停止传输信号(P),表示不再传输数据。

读数据

若配置的方向传输位为“读数据”方向,即第二幅图的情况,广播完地址,接收到应答信号后,从机开始向主机返回数据(DATA),数据包大小也为8 位,从机每发送完一个数据,都会等待主机的应答信号(ACK),重复这个过程,可以返回N 个数据,这个N 也没有大小限制。当主机希望停止接收数据时,就向从机返回一个非应答信号(NACK),则从机自动停止数据传输。

读和写数据

除了基本的读写,I2C 通讯更常用的是复合格式,即第三幅图的情况,该传输过程有两次起始信号(S)。一般在第一次传输中,主机通过 SLAVE_ADDRESS 寻找到从设备后,发送一段“数据”,这段数据通常用于表示从设备内部的寄存器或存储器地址(注意区分它与SLAVE_ADDRESS 的区别);在第二次的传输中,对该地址的内容进行读或写。也就是说,第一次通讯是告诉从机读写地址,第二次则是读写的实际内容。

以上通讯流程中包含的各个信号分解如下:

通讯的起始和停止信号

前文中提到的起始(S)和停止(P)信号是两种特殊的状态,见图 24-5。当 SCL 线是高电平时 SDA 线从高电平向低电平切换,这个情况表示通讯的起始。当 SCL 是高电平时 SDA线由低电平向高电平切换,表示通讯的停止。起始和停止信号一般由主机产生。

CAN总线全称Controller Area Network,中文名控制器局域网络。

CAN总线由以研发和生产汽车电子产品著称的德国BOSCH公司开发的,并最终成为国际标准(ISO 11898),是国际上应用最广泛的现场总线之一。

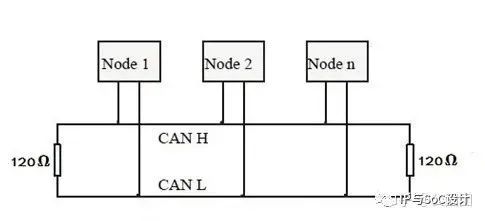

CAN总线采用差分信号线CAN_L和CAN_H进行通信,最高支持1Mbps的通信速率。CAN总线采用多主控(Multi-Master)线性拓扑结构,加入网络节点的设备均可以向总线发送广播消息,其他设备通过ID过滤掉不感兴趣的消息。CAN总线按照帧为单位进行数据传输,数据帧支持1-8Byte数据传输。

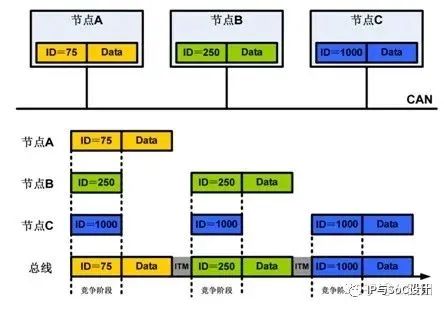

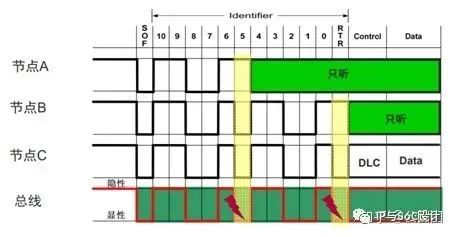

CAN总线基于多路载波侦听+基于消息优先级的冲突检测和非破坏性的仲裁机制,所有节点必须都等到总线处于空闲状态时才能往总线上发送消息,多个节点往总线上发送消息时具备最高优先级的消息获得总线。

通过ID仲裁,ID数值越小,报文优先级越高。

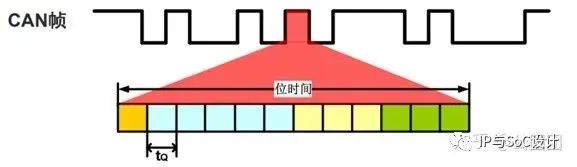

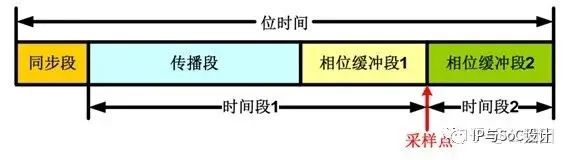

CAN总线通过过采样技术进行位同步,CAN控制器工作的最小时间单位(CAN时钟周期)称为时间份额,一个位包含多个CAN时钟周期。

为了实现位同步,CAN协议把每一位的时序分解成下图所示的四段。这四段的长度加起来即为一个CAN数据位的长度。一个完整的位由8-25个Tq组成。

当总线上出现帧起始信号(SOF,即隐性到显性的边沿)时,其他节点的控制器根据总线上的这个下降沿对自己的位时序进行调整,把该下降沿包含到SS段内。这样根据起始帧来进行的同步称为硬同步。因为硬同步时只是在有帧起始信号时起作用,无法确保后续一连串的位时序都是同步的,所以CAN引入了重新同步的方式。在检测到总线上的时序与节点使用的时序有相位差时(即总线上的跳变沿不在节点时序的SS段范围),通过延长PBS1段或缩短PBS2段来获得同步,这样的方式称为重新同步。

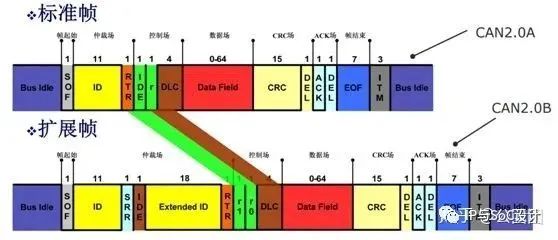

CAN一共规定了5中类型的帧,帧也称为报文。数据帧在CAN通信中最主要,也最复杂。数据帧以一个显性位(逻辑0)开始,以7个连续的隐性位(逻辑1)结束。CAN总线的数据帧有标准格式(Standard Format)和扩展格式(Extended Format)的区分。

- The End -

声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!