两年前在Twitter上看到一个网站ZIPCPU分享的信息,没太在意,毕竟RISC-V处理器很火,而看ZIPCPU的处理器并没有号称是第五代这么炙手可热的一个,且感觉CPU这个领域感觉离我们学习FPGA还是有点远。

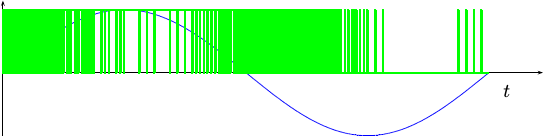

最近要用DDR的方式将ADC/DAC和FPGA数据连起来,就搜寻一些资料,又遇到ZIPCPU,碰巧看到这个网站上的一些技术文章非常有营养,入迷阅读了一下,发现篇篇都是作者的精品奉献,从原理到实际操作,由浅入深。比如关于PWM:https://zipcpu.com/dsp/2017/09/04/pwm-reinvention.html

给你截然不同的认识。

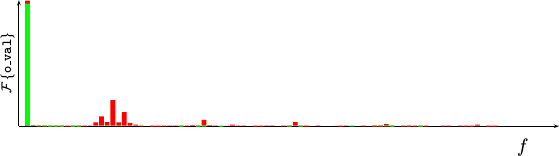

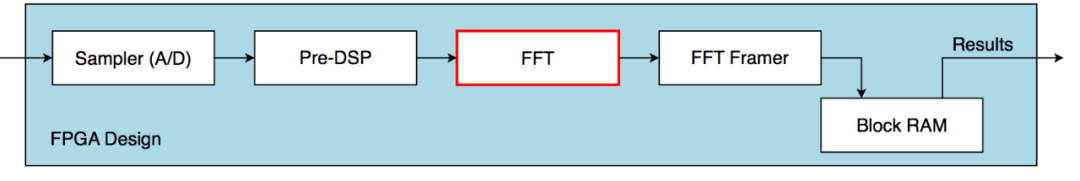

比如如何构建和调试FFT:

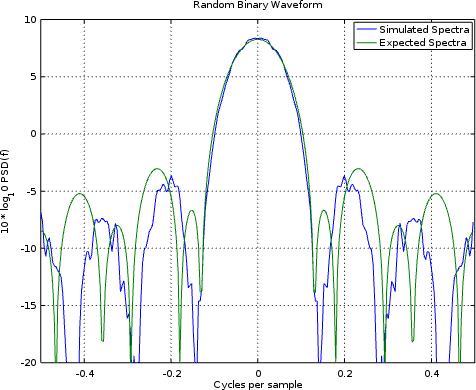

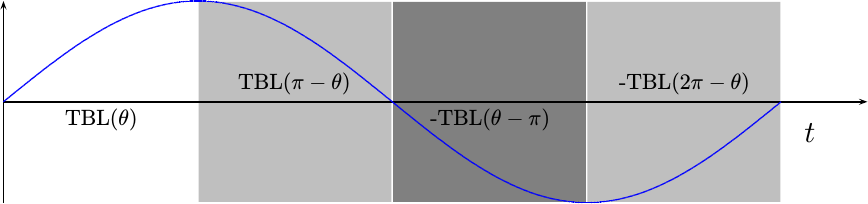

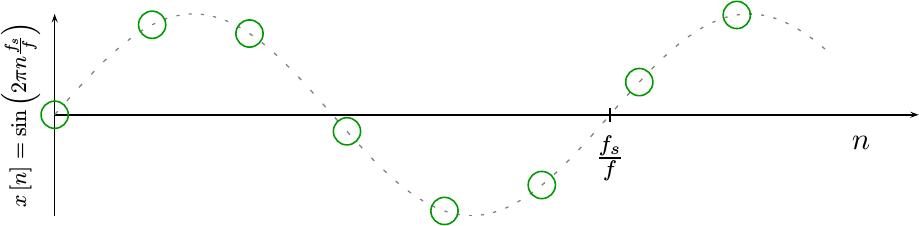

比如用多种方式构建正弦波表:

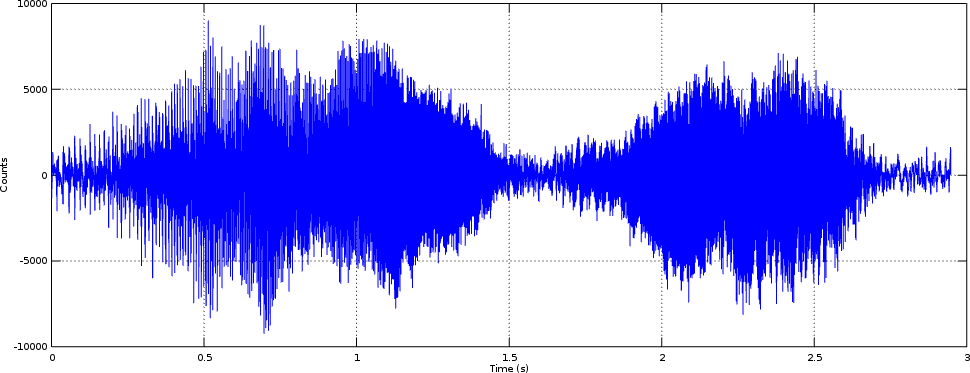

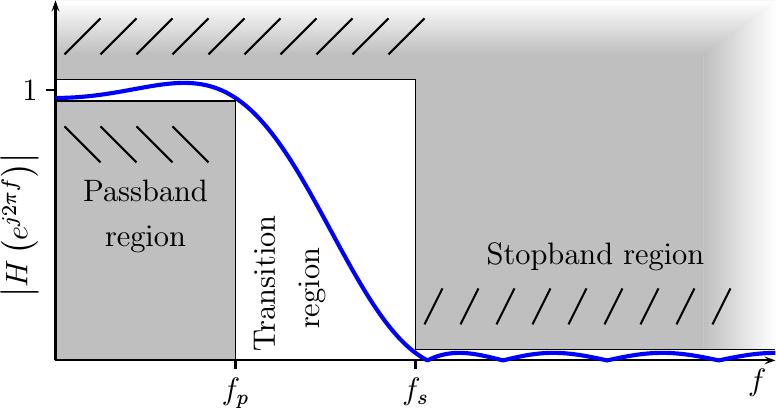

如何设计数字滤波器:

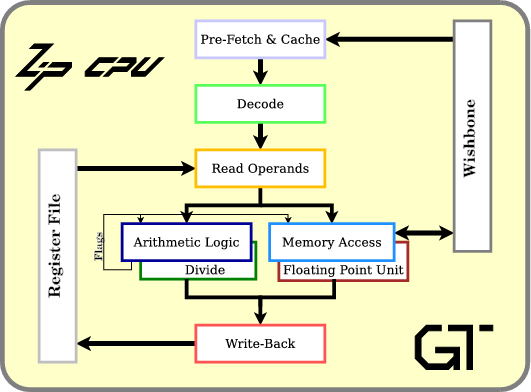

当然它的核心还是构建一个32位的CPU:

这个CPU内核全部开源,不依赖任何一家的FPGA,也就是说你用Xilinx、Intel、Lattice的FPGA都可以使用,并且所有的功能模块 - UART、I2C、SD卡、DDR、Ethernet等都是用逻辑写的,没有调用这些厂商现成的IP。

如何调试CPU

这些功能模块资源对我们就是非常好的参考。

这个网站除了这些非常详尽、专业的技术文章外,还有一套适合FPGA初学者入门的教程,有PDF格式的PPT文件以及参考代码。

无论你是FPGA的初学者,还是进阶的工程师,在这个网站上你都可以找到非常有价值的参考资源,你所需要的就是用“英文”来阅读。

我们“寒假一起练”的FPGA平台之一:

用FPGA来做嵌入式系统的有趣功能 - “2022寒假在家一起练”参考(2)

采用的是Lattice的iCE40UP5K,一款非常适合于做软核的FPGA芯片,在项目目标中设定了RISC-V的移植,当然同学们也可以试一下这个ZipCPU,按照这个网站的技术资料和教程,在我们的iCE40 FPGA平台上把它跑起来。

同时,我已经把这个网站上的资源做了汇总,放在电子森林里:

你可以点击左下角的“阅读原文”跳转,希望能够对FPGA的入门者、尝试实现CPU功能的同学有所帮助。

周末愉快!