1.BSI back side passivation process

表1 back dielectric and thickness

Layer(fromdown to top) | composition | Thickness (nm) |

AR back dielectric 1 layer | 金属氧化物薄膜(HfO2) | 6 |

AR back dielectric 2 layer | 金属氧化物薄膜(Ta2O5) | 52 |

back dielectric 3 layer | Oxide(此时开始形成TSV) | 160(以及Wgrid) |

Light shielding(W gird) | W/Ti-based | 220(190/30) |

back dielectric 4 layer | Nitride | 65 |

back dielectric 5 layer | Oxide | 260 |

back dielectric 6 layer | SiCNO(SiC,Si3N4,SiO2) | 68 |

back dielectric 7 layer | Oxide | 100 |

remark:data is Sony BSI 8M 1.12um pixel,TSV形成后去除4.5.6.7layer;

1.1 backside金属氧化物薄膜材料

两层金属氧化物薄膜材料起到抗反射涂层(ARC)作用;其中,HfO2薄膜在紫外到近红外有着良好的透过率(>80),与silicon晶格匹配好,具有较高的激光损伤阈值;

HfO2薄膜中固定电荷(负电荷)会在silicon表面感应出正电荷,形成表面P区,起到PINimplant降低入射光线串扰作用 ;

Addition Samsung:Ahafnium oxide-based trench fill provides a charge trapping layer to Passivatethe Si surface and also serves as an anti-reflevtion layer.

Ta2O5薄膜是可见光到近红外波段中具有较高的折射率,可应用于超低损耗激光薄膜和高损伤阈值激光薄膜领域;两层金属氧化物薄膜都具有较高的介电常数,击穿电场较高,漏电流较低;

1.2 Reduce Crosstalk CIS Structure

CIS光路的串扰主要分为三种:spectral(光谱),optical(光路),electrical(diffusion/drift);spectral主要是通过R/G/B过滤不可见光,optical可采用Wgrid进行isolation,electrical需要在silicon内部进行DTI(deep trench isolation);

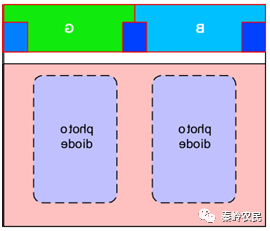

1.2.1 BCFA(buried color filter array)结构(spectral +optical)

BCFA: buried color filter array,掩埋的Color Filter阵列,使CFA距离silicon表面及backsidemetal更近,减少光串扰;

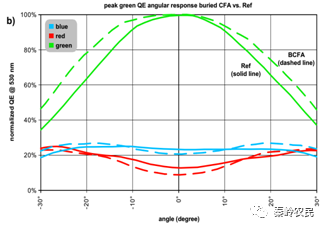

(1)BCFA结构(2)波长530nm量子效率对比

将R/G/B颜料层直接做在W金属grid中间,减小了PD到CFA的距离,有效的提高了量子效率;波长530nm,BCFA结构的量子效率明显比普通的高;

1.2.2 DTIStructure(electrical)

DTI:deep trench isolation,深沟槽隔离。主要是隔离silicon中pixelarray之间可能发生的电子扩散/漂移到相邻像素中造成的串扰;

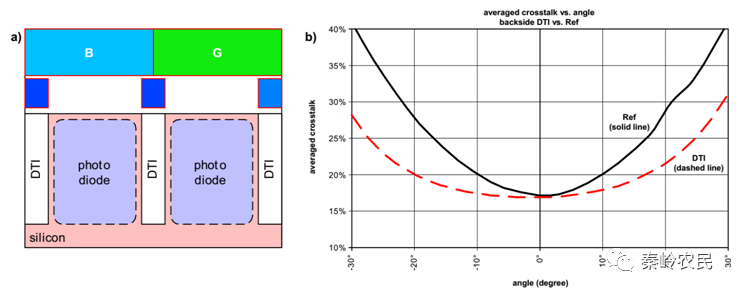

(1)DTI结构示意图(2)crosstalk&DTI

通过BCFA和背部DTI结构隔离来提高大阵列BSI sensor透光性;Backside不但在颜料层有Wgird隔离crosstalk,而且在PD区增加pixel与pixel之间的DTI isolation,进一步降低了电性和光的crosstalk;

1.2.3 SEM实物分析

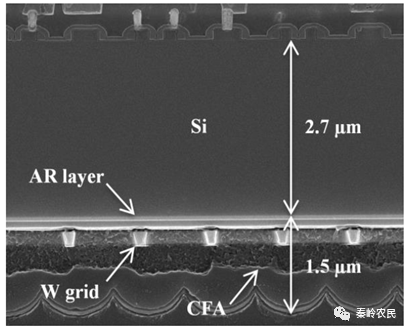

Sony和samsung均采用backsidemetal(Wgrid),将colorfilter填充在grid metal之间,Sony光学stack有1.5um厚,据报道,较薄的光学stack层能提高边缘pixel的敏感度;

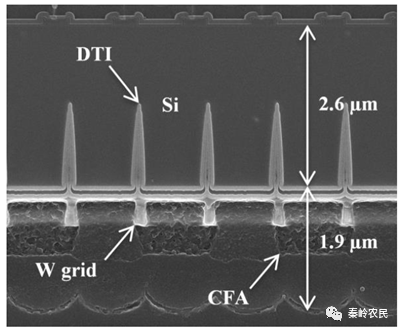

Samsung的colorfilter相对来说较厚,约1.9umopticalstack,他的策略是将嵌入的filter与silicon表面的deeptrenchisolation(DTI)结合技术来减少衬底的电性及光学crosstalk;DTI深度约1.6um,衬底厚度约2.6um;图(1)的CFA SEM不清晰;

(1) Sony IMX214, 1.12 µm Pixel, Embedded Color Filter Array(2)Samsung S5K2P2XX, 1.12 µm Pixel, Partial DTI

DTI Process flow(难点是backsidealignment):

(1)waferbonding及背面grinding;

(2)silicon表面deposited HfO2薄膜;

(3)photo&etch DTI形成deep isolation;

(4)深槽侧壁淀积deposited oxide;

(5)填充金属(一般为W);

Tips:(2)完成后可能还会淀积oxide,才会进行(3)的工艺,此处是主要工艺步骤;

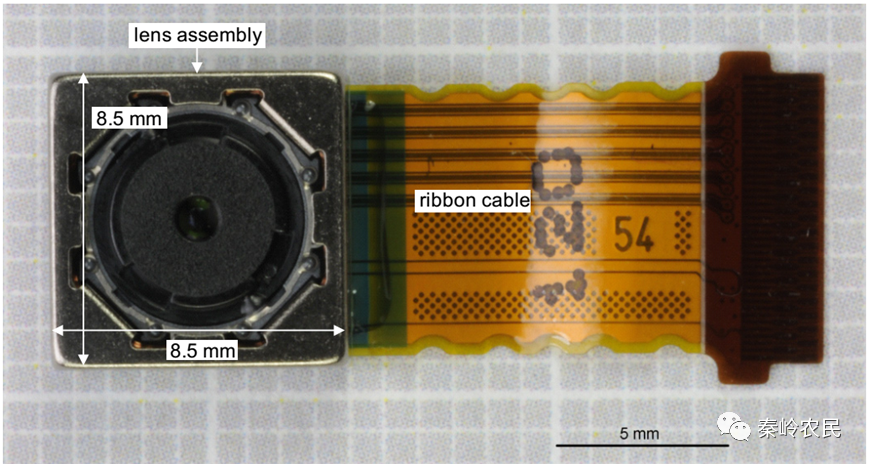

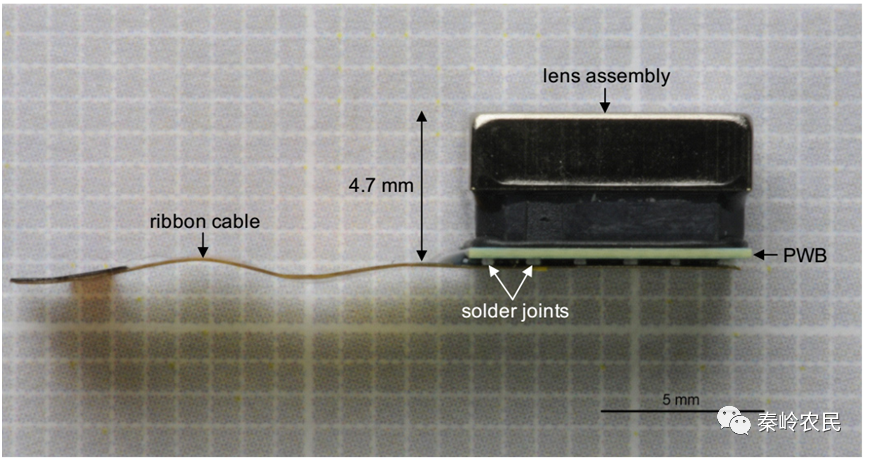

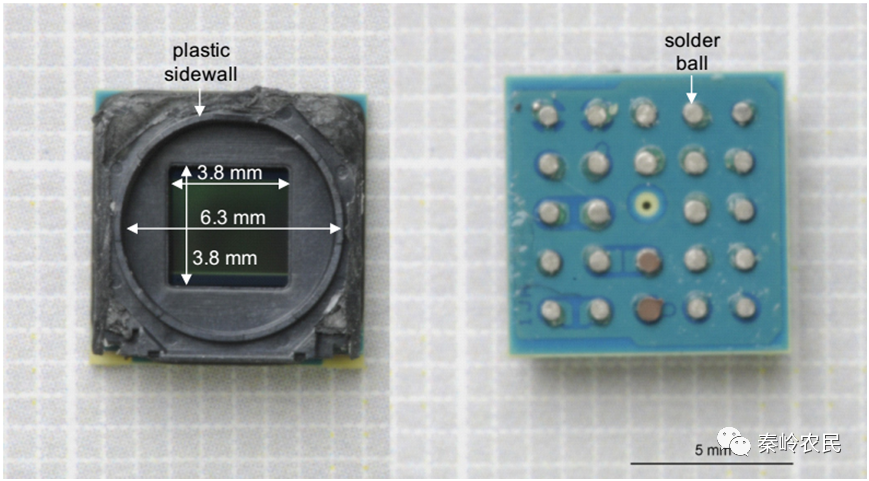

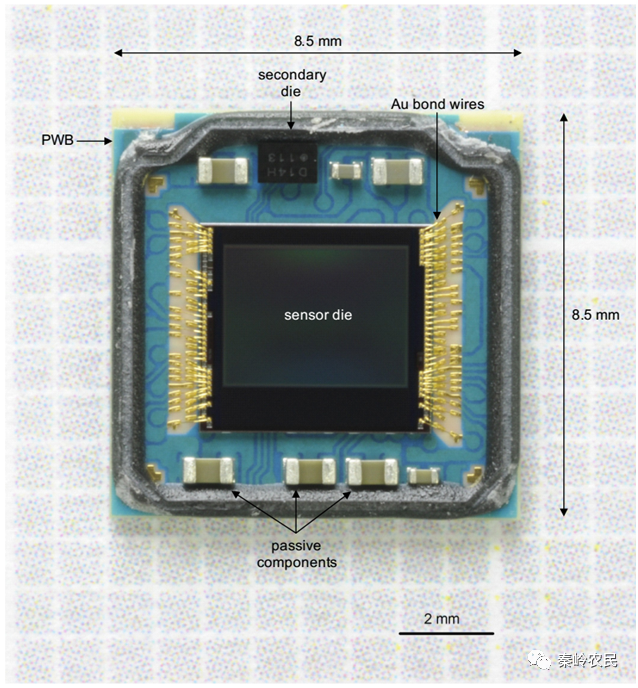

2 BSI Stack Package

2.1 sony stack CIS

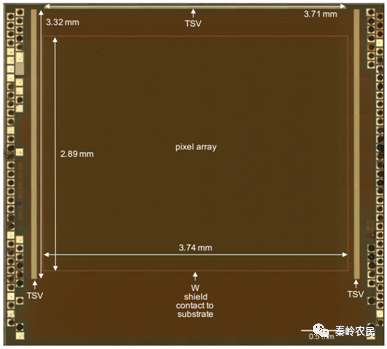

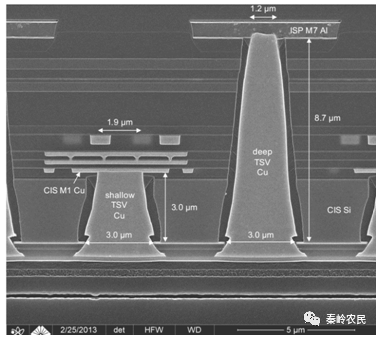

CIS采用BSI结构,将CIS wafer与ISP wafer face to facebonding到一起,CIS M1通过shallow TSV引出到芯片表面,ISP芯片M7通过deep TSV技术引出到与CIS同侧,极大地减小了电路互连和封装尺寸;

CISwafer使用Ptype衬底,90nmCMOS工艺,金属互连采用四级铜互连。许多CIS外围电路可转移到ISP芯片上,使得CIS芯片面积更小;

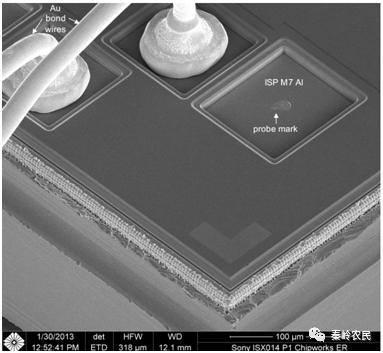

ISP芯片采用65nm工艺,使用6级铜互连和top层Al金属层(共7层metal),铝层形成器件的键合pad,wafer键合后通过蚀刻CIS背面介质层,silicon形成TSV通孔,shallowTSV到达CISmetal 1铜层,deep TSV到达ISP芯片metal7铝层,TSV腔体采用铜淀积互连形成,ISPpad opening通过蚀刻CIS背面,CISsilicon,介质层到达metal 7;Wafer总厚度170um(包含CISwafer 2.7um,ISP wafer 160um);

Remark:考虑到工艺难度及可靠性,可不减薄ISP芯片厚度(直接采用725um硅厚),不影响其他特性;

(1)sony stackCIS(data is Sony BSI8M 1.12um pixel CIS+ISP)

表1CIS+ISP参数

Parameter | CIS | ISP |

Silicon thickness | 2.7um | 160um |

Die size(from die edge) | 4.75mm*4.27mm | 4.75mm*4.27mm |

Die size(from die seal) | 4.68mm*4.22mm | 4.68mm*4.22mm |

Process type | CMOS BSI image | CMOS |

Metal layer | 4(cu) | 7(6cu,1Al) |

Process generation | 90nm | 65nm |

Shallow TSV(厚度3.0um) | 上开口(3.0um) | 下开口(1.9um) |

Deep TSV(厚度8.7um) | 上开口(3.0um) | 下开口(1.2um) |

Remark:CIS与ISP芯片diesize相同,便于wafer对位及dieTSV通孔实现;

此TSV技术属于后通孔(vialast)技术,先将wafer键合到另一wafer上减薄,然后再蚀刻得到通孔(vialast);

制作TSV通孔的方法主要有:激光钻孔(laserdrill)和深反应离子蚀刻(DRIE);激光钻孔直径在20um左右,此处应使用DRIE技术;

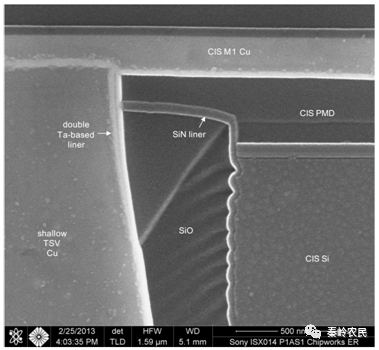

shallowTSV侧壁采用SiNliner-SiO2-Ta组成,TSV采用Cu金属填充。其中Ta金属层是doublelinerthickness;Cu与oxide粘附性较差,因此需要淀积Ta金属增加粘附性(也可采用Ti/TiN/TaN等金属薄膜);

表2TSV主要参数

Structure | Depth(um) | Top(um) | Bottom(um) | Thickness(um) |

Shallow TSV | 3.0 | 3.0 | 1.9 | |

Deep TSV | 8.7 | 3.0 | 1.2 | |

Nitride linear | ~0.04 | |||

Oxide buffer | ~0.45 | |||

Ta-based liner(double) | ~0.05 | |||

TSV strap(unknow) | 0.18 |

2.2 shallow/deep TSV process

2.2.1shallow TSV process

(1)在shallowTSV形成之前,CISwafer背面会先deposited一层ARlayer(6nmHfO2+52nm tantalum oxide layer,160nm厚的oxidelayer);

(2)然后开始etch形成shallowTSV(深反应离子蚀刻(DRIE);

接下来没有详细的资料介绍;

(3)shallowTSV形成之后,deposited65nmnitride layer及260nmoxidelayer;nitridelayer在TSV空腔内形成一层liner,oxidelayer,对于TSV条纹的连接,可形成trench结构;随后淀积种子层及电镀铜互连层;

(4)TSV形成之后,会在cooper条纹上deposited68nmSiCNO barrier layer,然后是100nm的oxidelayer,作为CIS背面介质层的top层;

(5)在pixel区域,Wmetalgird在ARlayer上方形成(即oxidelayer中),作为lightshield;背面的Wmetallayer是在Ti或氮化钛layer上形成;

ShallowTSV 通过etchsilicon到达CISPMD(pre-metal dielectric)的stoplayer层,但在到达CISmetal1pad之前;

2.2.2 deep TSV process

DeepTSV通过etch到达ISPmetal7铝层,TSV空洞内线性的depositednitridelayer,oxidedepositedTSV孔内侧;然后在CIS背面depositedoxidelayer,然后在TSV上方的oxide层trenches连接到了TSV;TSV底部的etchopen来增加TSV空洞与metalpad的连接;doubletantalum-based在TSV空洞内形成,随后进行铜淀积及CMP工艺;所有的pad在ISP芯片的metal7铝层形成,padopen窗口从CISsilicon,CIS介质层及ISP钝化层到ISPmetal7的铝层;