文章来源:中国战略新兴产业

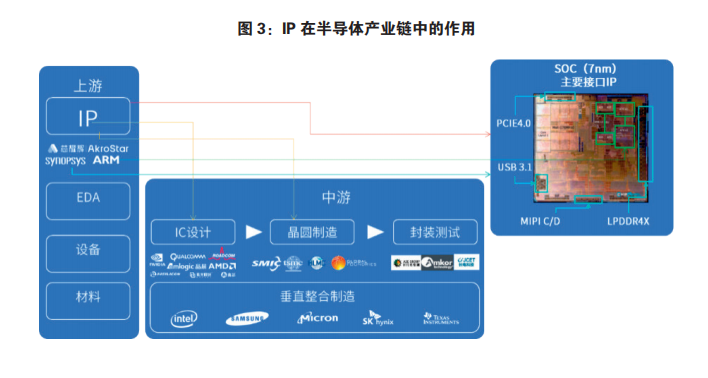

我国IC设计业和芯片代工业的崛起和高速发展,为本土EDA/IP产业发展提供了用武之地。一方面,本土IC设计公司要构建起自主可控的SoC芯片开发平台,相应的自主IP及其复用技术是不可或缺的关键模块和核心技术。另一方面,本土芯片制造厂商为打造自主可控芯片制造平台,必须根据新类别的IC开发及其应用,考虑引进并提前验证一些关键性国产EDA/IP,以便导入客户SoC产品投片并实现量产。

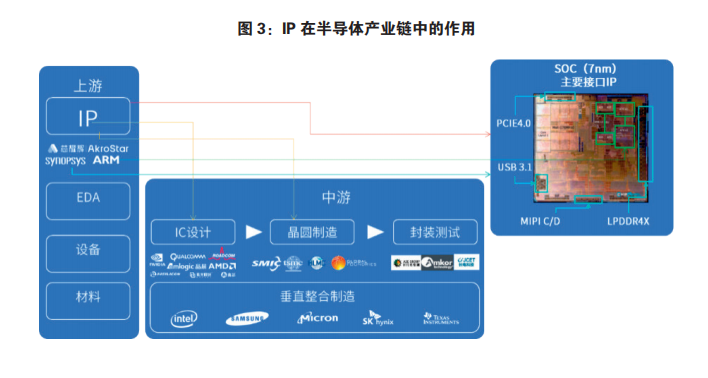

在半导体领域,所谓知识产权(IP)是指集成电路(IC)设计中那些具有特定功能、可以重复使用的电路模块,通常也称为半导体知识产权(SIP)。它的兴起和演进完全受益于专用标准产品(Application-Specific Standard Product,ASSP)和片上系统(System on a Chip,SoC)的发展,包括电子设计自动化(Electronic Design Automation,EDA)软件的发展。今天,IP及其复用已成为SoC设计平台的不可或缺的关键技术和核心基础,它决定着最终SoC芯片的性价比(面积、功耗、时延等)、市场竞争性及其系统创新性等。

应该看到,集成电路是国之重器,我国EDA/IP技术,至今受制于人的状况未有根本性改变。在“十四五”期间,我们必须以创新为动力,高质量发展为主题,加快关键核心技术突破,构建起以国内大循环为主体、国内国际双循环相互促进的新发展格局,创造新需求;坚持与国产EDA融合发展,励志于高起点开拓自主可控的“IP+EDA”民族事业,推动以IC为核心的战略性新兴产业融合化、集群化、生态化发展。

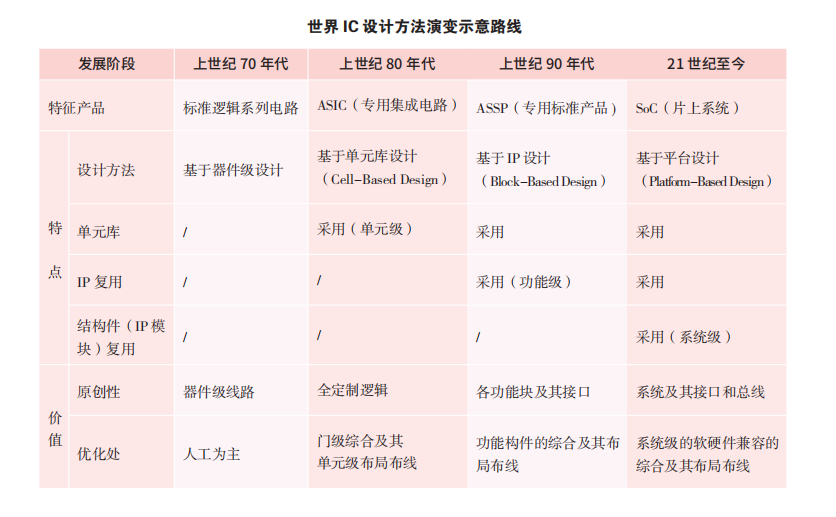

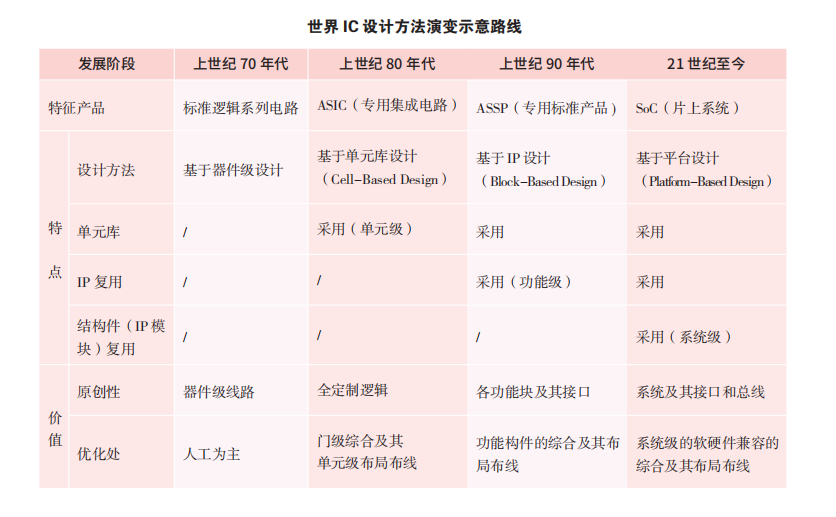

SoC概念是1995年由美国LSI Logic等公司首先提出,是指在单一硅芯片上实现一个系统所具有的信号采集、转换、存储、处理和输入、输出(I/O)等功能的电路。其基本特征包括:内嵌CPU核和其他诸如DSP等核心IP、包括丰富的输入/输出(I/O)接口,和一定容量的存储器;采用硬件、软件协同设计方法,包括完整的操作系统和用户软件;具有强大的数据、图像传输和处理能力,以及高可靠、友好的用户界面。如上表显示了世界IC设计方法进步带动其IC产品形态演变的过程。

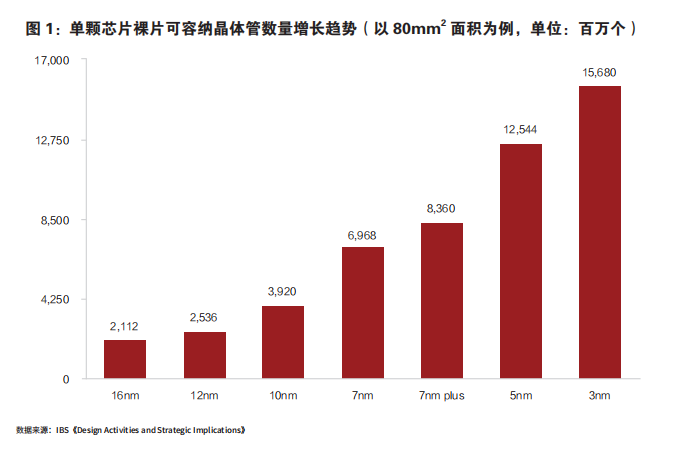

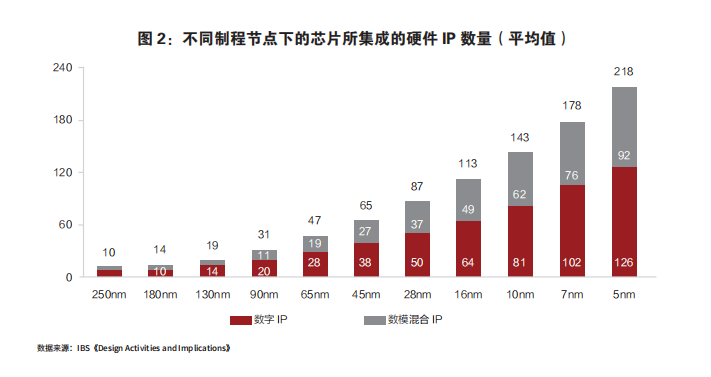

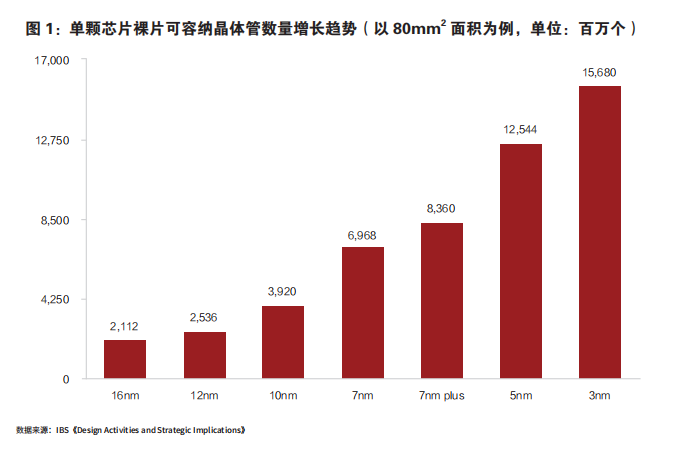

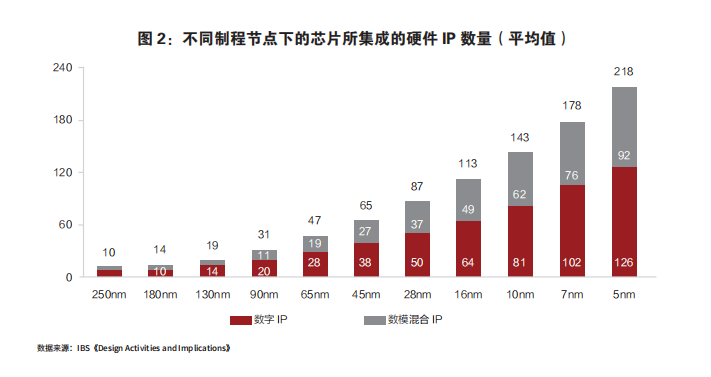

20世纪70年代,IC基于器件级而设计。这一时期为配合刚兴起的微处理器和存储器的开发应用,通用的系列化、标准化逻辑电路盛行。其设计主要以人工为主,仅在数据处理和图形编辑方面采用了计算机辅助设计。其中IC设计和半导体工艺不可分离。20世纪80年代,IC基于单元库而设计。这一时期由于微处理器和PC机的广泛应用和普及,标准化功能的IC难以满足整机客户对成本和可靠性的要求。于是专用集成电路(ASIC)诸如门阵列(GA)、可编程逻辑(PLDs)包括现场可编程门阵列(FPGA)、标准单元、全定制电路等应运而生。其比例在1982年,已占整个集成电路销售额中12%,此时ASIC单为一个客户服务。同时其设计方法随着EDA工具(电子设计自动化工具)的出现,PCB(印刷线路板)设计方法被引入,如库的概念、工艺模拟参数及其时序仿真概念等,并逐渐造成了设计和工艺分离的技术环境。20世纪90年代,IC基于IP而设计。这一时期由于互联网推动了通信和网络及多媒体信息家电的IC需求,仅为单一客户服务的ASIC已难以应对不同客户对某一类系统功能(如音频、图像压缩等)的不同要求,故ASIC延伸为专用标准产品;同时其设计方法由于EDA工具的发展,解决了过去IC设计技术中的时序收敛等问题,设计进入了功能级的抽象化阶段,即可复用以前的、经过验证、并有一定功能的设计资源。这些设计资源具有知识产权价值,故称为硅知识产权,且IP及其复用在业界巨头企业内部被普遍采用。特别是,到20世纪90年代中期,由于SoC的兴起,鉴于其使IC设计公司将有限的资源投入核心专长领域,故一些专门提供这种IP功能模块的知识产权的公司和供应商也就应运而生,IP开始成为市场化商品。21世纪初至今,IC基于IP模块及其复用的平台而设计。当前的硅加工技术已可以在一个芯片上制备近百亿个晶体管。根据IBS报告,以80mm²面积的芯片裸片为例,在3nm工艺节点下,该晶体管数量可增长到156.8亿个。另外,以5nm制程节点为例,可集成的IP数量将达到218个。

鉴此,基于平台设计的SoC架构特点有三点。一是,它基于结构件(IP模块)及其复用的系统级不同应用,故可应市地衍生出一系列不同功能的IC产品;二是,它基于软硬件协同设计的结构,故使得同一系列的IC产品升级更为方便;三是,它将有助于包括IP、EDA、芯片制造、封装测试和集成器件制造(IDM)及其应用在内的整个IC产业链和供应链的高质量地自主可控发展。

应该看到,IP在IC设计中所提供的可重复利用的模块方式,基本可分为三种形态。硬核(HardCore)。其是指已经过某特定工艺验证、提供最小面积和最优性能的、具有可保证性能的电路物理结构的全套掩模版图(GDSII文件格式)。由于硬核是IP的最深层次,硬核知识产权的保护比较简单,一般提供硬核的公司或通过芯片制造厂商能对它全权加以控制。硬核的缺点是价格昂贵,且受特定工艺或代工厂的限制,使得为缩小面积而进一步优化设计变得必须重新设计。软核(SoftCore)。其是指只完成晶体管逻辑(RTL)级的行为设计、具有可综合的硬件描述语句(VerilogHDL或VHDL)的文档形式。由于它是优化的行为级设计,且通常已经过工艺验证,不受工艺实现条件的限制,故其具有比硬核使用和修改的最大的灵活性,如字长、总线配置、I/O接口选择等指标都可以根据产品的变化而变化。但其缺点是对IP的预测性太低,增加了引入差错的设计风险,用户在后续的设计中需有相应的EDA开发和测试环境。固核(FirmCore)。其是一种间于软核和硬核之间的IP,指完成逻辑图设计,是以“与工艺有关的门级网表“的形式提交使用。由于它比软核有更大的设计深度,所以,只要用户单元库的时序参数与其相同,就具有正确完成物理设计的可能性。“十四五”期间,我国集成电路产业将从规模增长向高质量发展转型,是构建自主可控新格局的重大变革期,营造了前所未有的发展机遇。《国家国民经济和社会发展第十四个五年规划和2035年远景目标纲要》明确指出:要“推动集成电路、航空航天、船舶与海洋工程装备、机器人、先进轨道交通装备、先进电力装备、工程机械、高端数控机床、医药及医疗设备等产业创新发展。”这不仅加速促进我国本土“EDA/IP+IC设计+芯片制造+系统应用”生态体系建设及其高质量地融合发展;同时,大大增强EDA/IP在内的集成电路产业链和供应链自主可控能力及其创新发展。我国IC设计业和芯片代工业的崛起和高速发展,为我国本土EDA/IP产业发展提供了得天独厚的用武之地。一方面,本土IC设计公司要构建起自主可控的SoC芯片开发平台,相应的自主IP及其复用技术是不可或缺的关键模块和核心技术。另一方面,本土芯片制造厂商为打造自主可控芯片制造平台,必须根据新类别的IC开发及其应用,考虑引进并提前验证一些关键性国产EDA/IP,以便导入客户SoC产品投片并实现量产。中兴事件和华为实体名单所涉及的中美贸易摩擦,使国内信息产业和集成电路两大业界对“芯结”达成共识,对本土具有自主知识产权的EDA/IP寄予深情期望,国产替代成为不可逆转的大潮,将极大地激励着我国高质量地自主发展EDA/IP产业的决心和恒心。今天,我国已成为全球最大的IC应用市场,随着硅CMOS工艺制造已逐渐逼近物理极限,促使国内量子技术、第三代半导体技术的积极研发推进;加上国内“5G+AI+云计算”引发的数字经济蓬勃发展,这极大地推动包括协议、标准在内的半导体IP新结构、新模式的创新发展。毫无疑问,EDA/IP是半导体产业链和供应链的“金字塔”顶端。为此,我们必须立足自身资源禀赋、发展条件、比较优势等实际,精准把握我国IP产业高质量发展的新阶段、新格局的深刻内涵,找准突破瓶颈和短板的切入点和发力点,扎扎实实打造以本土EDA/IP为核心的自主可控的集成电路创新体系。基此,建议创新发展产学研结合新机制,加快构建以国内应用场景为主体的新发展格局,创造新需求,高质量发展我国IP产业,有力提供我国集成电路产业发展新动能。启动和实施IP集群培育工程,壮大一批具有IP生态主导力和核心竞争力的龙头企业。培育专精特新“小巨人”IP企业和IP业的单项冠军企业。驱动EDA/IP和芯片制造深度合作和统筹规划,打造完整国产IP生态,从而发展未来“EDA/IP+IC设计+芯片制造+系统应用”生态创新平台及新型研发机构,加快EDA/IP融合发展及其技术创新应用,提升IC产业链、供应链防护能力,防范化解安全风险隐患。培养造就高水平IP人才队伍。基于国家重大集成电路科研任务,重大工程项目,依托国家微电子学院等机构,建设IP交叉基础学科,加速培养EDA/IP急需的各类人才。营造良好政策发展环境,积极开展国际间开放合作,主动融入全球EDA/IP创新网络,建议制定政府财政支持的中外EDA/IP合作专项的政策和实施办法。

作者简介

曾克强,芯耀辉科技有限公司董事长兼联席CEO,曾任新思科技中国区副总经理。

余成斌,芯耀辉科技有限公司联席CEO,IEEE Fellow、澳门大学集成电路国家重点实验室联合创始人、中国半导体行业协会 IC设计分会副理事长。