集成电路工艺进步和设计技术发展促使芯片功能日益复杂,集成度越来越高。在高速数字系统中,电磁干扰(EMI)和信号完整性及电源完整性密切相关,相互影响,例如:信号过孔穿过参考平面时不仅会引起高速信号边沿的畸变和退化,而且有可能由于阻抗突变和回路面积增大向电源/地平面注入足够能量从而产生谐振,引起较大的EMI。

在芯片封装时减小EMI噪声,可以极大地减轻后续PCB级和整机的电磁兼容(EMC)设计压力,从而大幅度地缩短研发周期和降低成本,因此EMI问题在封装设计中不可忽视。然而,随着芯片集成度越来越高,尺寸日益减小,功能越来越复杂,元器件数目越来越多,芯片封装设计面临着严峻的EMC挑战。

据麦姆斯咨询报道,近期,中国电子科技集团公司第五十八研究所工程师孙明辉、王剑峰和王波在《电子产品可靠性与环境试验》期刊上发表了以“封装设计中辐射EMI产生机理及其抑制方法综述”为主题的论文。该论文通过分析集成电路封装设计中辐射电磁干扰产生的机理,对在芯片封装设计中存在的辐射EMI问题和应对方法进行了分析与总结,对于今后在封装设计中减小辐射EMI、保证芯片信号完整性有一定的指导意义。

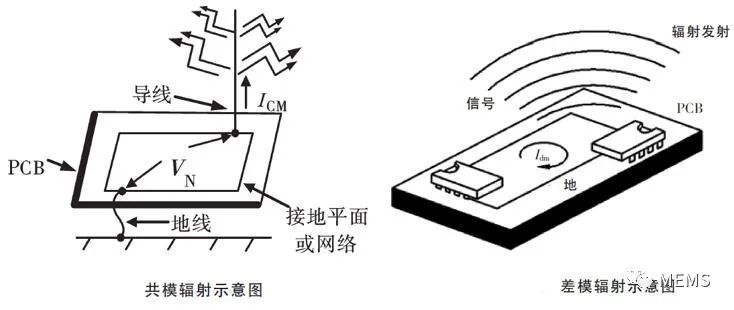

在电子系统中,所有引起电磁场变化的因素或电磁场未得到有效控制之处都会导致辐射EMI的产生,例如:接插件、过孔和通信接口等。辐射EMI有电场辐射和磁场辐射两种形式,其中以电场辐射为主,而电场辐射按照辐射产生的原理不同又分为共模辐射和差模辐射。

电场辐射

在封装设计中,任何非理想互连结构(键合线、信号过孔和参考平面不完整等)在高速信号或噪声传输时都极易引起辐射EMI问题,例如:走线、接插件和键合线等在1/4波长的尺寸下可能产生天线效应,成为辐射源。在封装设计中常见的EMI产生原因有以下几种:差分信号转化为共模信号、键合线引起串联谐振、封装盖板引起的EMI以及芯片的电磁耦合问题。

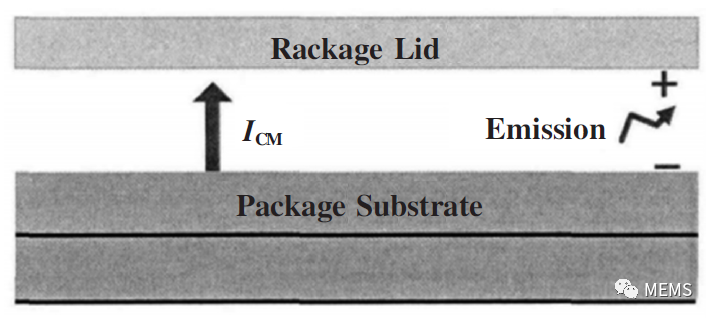

封装盖板的辐射EMI模型

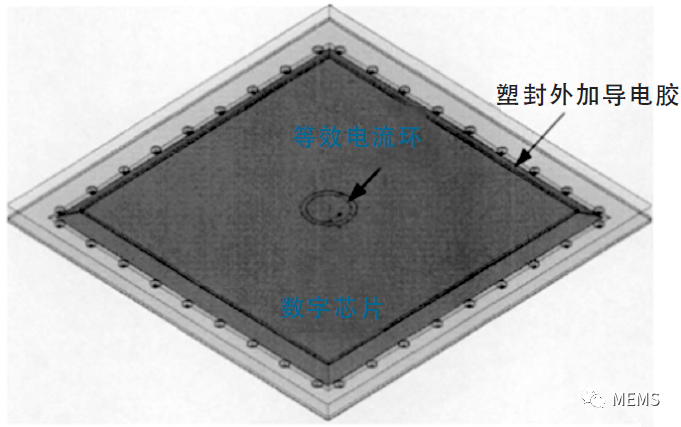

对于封装设计中的辐射EMI问题,现有的抑制方法主要集中在屏蔽、滤波和结构改善等方面。针对封装设计中常见的辐射EMI问题,国内外主要研究的抑制方案有:利用补偿电容和共模滤波器方法抑制差分信号中共模电流、利用异质系统集成的全新键合互连结构和新型同轴芯片互连系统抑制键合线引起的EMI、运用电磁带隙(EBG)结构可有效减少封装盖板引起的EMI、采用新型三维混合信号芯片屏蔽堆叠结构可有效地抑制电磁耦合产生的辐射EMI。

新型三维混合信号芯片屏蔽堆叠结构

在芯片封装设计中,必需考虑其EMC,尤其是辐射EMI问题,以确保信号完整性,保证芯片功能的正常实现。通过分析封装设计中存在的EMI隐患问题,针对不同的辐射EMI问题而有针对性地提出抑制方法,降低EMI对芯片电路的影响,确保芯片的可靠性和质量。